# Other Issues

- support for procedures (Refer to section 3.6), stacks, frames, recursion

- · manipulating strings and pointers

- Iinkers, loaders, memory layout

- Interrupts, exceptions, system calls and conventions

- Register use convention

| Name      | Register number | Usage                                        |

|-----------|-----------------|----------------------------------------------|

| \$zero    | 0               | the constant value 0                         |

| \$v0-\$v1 | 2-3             | values for results and expression evaluation |

| \$a0-\$a3 | 4-7             | arguments                                    |

| \$t0-\$t7 | 8-15            | temporaries                                  |

| \$s0-\$s7 | 16-23           | saved                                        |

| \$t8-\$t9 | 24-25           | more temporaries                             |

| \$gp      | 28              | global pointer                               |

| \$sp      | 29              | stack pointer                                |

| \$fp      | 30              | frame pointer                                |

| \$ra      | 31              | return address                               |

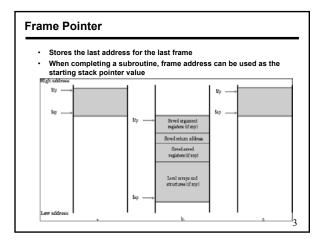

# **Stack Manipulation**

- Register \$29 is used as stack pointer

- · Stack grows from high address to low address

- Stack pointer should point to the last filled address

- Once entries are removed, stack pointer should be adjusted

# Alternative Architectures

- Design alternative:

- provide more powerful operations

- goal is to reduce number of instructions executed

- danger is a slower cycle time and/or a higher CPI

- · Sometimes referred to as "RISC vs. CISC"

- $-\,$  virtually all new instruction sets since 1982 have been RISC

- VAX: minimize code size, make assembly language easy instructions from 1 to 54 bytes long!

- We'll look at PowerPC and 80x86

PowerPC

- Indexed addressing

- example: lw \$t1,\$a0+\$s3 #\$t1=Memory[\$a0+\$s3]

- What do we have to do in MIPS?

- Update addressing

- update a register as part of load (for marching through arrays)

- example: lwu \$t0,4(\$s3) #\$t0=Memory[\$s3+4];\$s3=\$s3+4

- What do we have to do in MIPS?

- · Others:

- load multiple/store multiple

- a special counter register "bc Loop"

- decrement counter, if not 0 goto loop

### 80x86

- 1980: The 8087 floating point coprocessor is added

- 1982: The 80286 increases address space to 24 bits, +instructions

- 1985: The 80386 extends to 32 bits, new addressing modes

- 1989-1995: The 80486, Pentium, Pentium Pro add a few instructions (mostly designed for higher performance)

- · 1997: MMX is added

"This history illustrates the impact of the "golden handcuffs" of compatibility

7

"adding new features as someone might add clothing to a packed bag"

"an architecture that is difficult to explain and impossible to love"

# A dominant architecture: 80x86 9 complexity: 9 experience of the state of the source and destination 9 experience of the source of the source and the source of the source of

| Name<br>31 |    | 0 Use                              |

|------------|----|------------------------------------|

| EAX        |    | GPRO                               |

| ECX        |    | GPR 1                              |

| EDX        |    | GPR 2                              |

| EBX        |    | GPR 3                              |

| ESP        |    | GPR 4                              |

| EBP        |    | GPR ö                              |

| ESI        |    | GPR 6                              |

| EDI        |    | GPR 7                              |

|            | cs | Code segment pointer               |

|            | 89 | Stack segment painter (top of stac |

|            | DS | Data segment pointer O             |

|            | ES | Data segment pointer 1             |

|            | FS | Data segment pointer 2             |

|            | GS | Data segment pointer 3             |

| кір        |    | Instruction pointer (PC)           |

| EFLAGS     |    | Canditian codes                    |

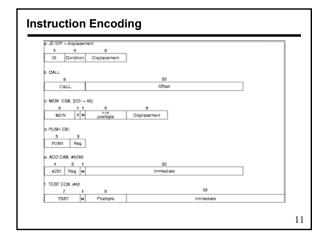

| xamples of non aithmetic instructions |                                                                     |   |  |  |

|---------------------------------------|---------------------------------------------------------------------|---|--|--|

| Instruction                           | Function                                                            |   |  |  |

| JE name                               | If equal (CC) EIP = name };<br>EIP-128 $\leq$ name $\leq$ EIP + 128 |   |  |  |

| JMP name                              | $\{EIP = NAME\};$                                                   |   |  |  |

| CALL name                             | SP = SP - 4; $M[SP] = EIP + 5$ ; $EIP = name$ ;                     |   |  |  |

| MOVW EBX,[EDI + 45]                   | EDX = M [EDI + 45]                                                  |   |  |  |

| PUSH ESI                              | SP = SP - 4; $M[SP] = ESI$                                          |   |  |  |

| POP EDI                               | EDI = M[SP]; SP = SP + 4                                            |   |  |  |

| ADD EAX,#676ō                         | EAX = EAX + 6765                                                    |   |  |  |

| TEST EDX,#42                          | Set condition codes (flags) with EDX & 42                           |   |  |  |

| MOVSL                                 |                                                                     |   |  |  |

| ·                                     |                                                                     | 1 |  |  |

# Summary

- Instruction complexity is only one variable

- lower instruction count vs. higher CPI / lower clock rate

- Design Principles:

- simplicity favors regularity

- smaller is faster

- good design demands compromise

- make the common case fast

- · Instruction set architecture

- a very important abstraction indeed!

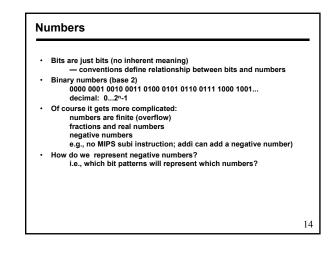

| Sign Magnitude:      | One's Complement     | Two's Complement     |  |

|----------------------|----------------------|----------------------|--|

| 000 = +0<br>001 = +1 | 000 = +0<br>001 = +1 | 000 = +0<br>001 = +1 |  |

| 001 = +1<br>010 = +2 | 001 = +1<br>010 = +2 | 001 = +1<br>010 = +2 |  |

| 010 = +2<br>011 = +3 | 010 = +2             | 010 = +2             |  |

| 100 = -0             | 100 = -3             | 100 = -4             |  |

| 100 = -0             | 100 = -3             | 1004                 |  |

| 101 = -1             | 101 = -2<br>110 = -1 | 1013<br>110 = -2     |  |

| 110 = -2             | 111 = -0             | 111 = -1             |  |

| sues: balance        | . number of zeros.   | ease of operations   |  |

| hich one is be       |                      |                      |  |

| licit offeris be     | St: Wily:            |                      |  |

| MI | S                                                    | • |

|----|------------------------------------------------------|---|

| •  | 2 bit signed numbers:                                |   |

|    | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |   |

|    | 1                                                    | 6 |

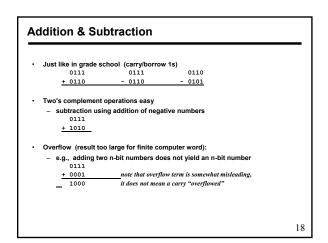

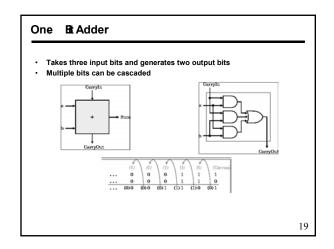

# Adder Boolean Algebra

· A B CI CO S • 0 0 0 0 0 . 0 0 1 0 1 0 1 0 0 1 C = A.B + A.CI+ B.CI 0 1 1 1 0 S = A.B.CI + A'.B'.CI+A'.B.CI'+A.B'.CI' 1 0 0 0 1 . 10110 1 1 0 1 0 • 1 1 1 1 1

20

| Real Design |   |   |   |   |   |   |                              |

|-------------|---|---|---|---|---|---|------------------------------|

|             |   |   |   |   |   |   |                              |

| •           | Α | в | С |   | Е | F |                              |

| •           | 0 | 0 | 0 | 0 | 0 | 0 |                              |

| •           | 0 | 0 | 1 | 1 | 0 | 0 |                              |

| •           | 0 | 1 | 0 | 1 | 0 | 0 | D = A + B + C                |

| •           | 0 | 1 | 1 | 1 | 1 | 0 |                              |

| •           | 1 | 0 | 0 | 1 | 0 | 0 | E = A'.B.C + A.B'.C + A.B.C' |

| •           | 1 | 0 | 1 | 1 | 1 | 0 |                              |

|             | 1 | 1 | 0 | 1 | 1 | 0 | F = A.B.C                    |

|             | 1 | 1 | 1 | 1 | 0 | 1 |                              |

|             |   |   |   |   |   |   |                              |

|             |   |   |   |   |   |   |                              |

|             |   |   |   |   |   |   |                              |

|             |   |   |   |   |   |   |                              |

|             |   |   |   |   |   |   |                              |

|             |   |   |   |   |   |   |                              |

|             |   |   |   |   |   |   |                              |

|             |   |   |   |   |   |   | 23                           |