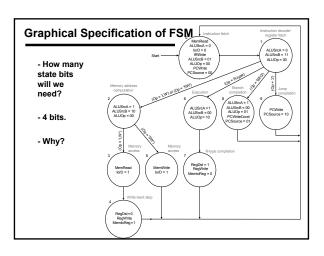

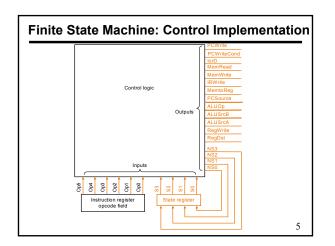

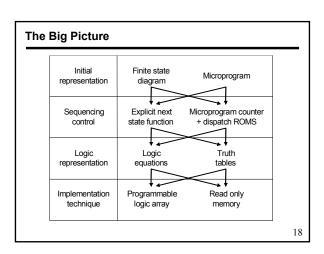

## **Deciding the Control**

- · In each clock cycle, decide all the action that needs to be taken

- The control signal can be 0 and 1 or x (don't care)

- Make a signal an x if you can to reduce control

- An action that may destroy any useful value be not allowed

- Control Signal required

- ALU: SRC1 (1 bit), SRC2(2 bits),

- operation (Add, Sub, or from FC)

- Memory: address (I or D), read, write, data in IR or MDR

- Register File: address rt/rd, data (MDR/ALUOUT), read, write

- PC: PCwrite, PCwrite-conditional, Data (PC+4, branch, jump)

- Control signal can be implied (register file read are values in A and B registers (actually A and B need not be registers at all)

- Explicit control vs indirect control (derived based on input like instruction being executed, or function code field) bits

3

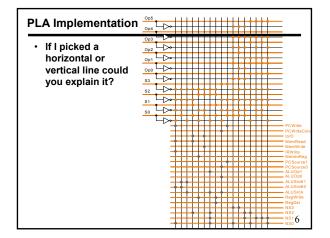

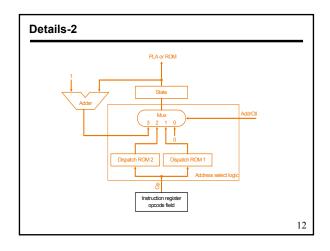

| C            | lispatch ROM1               |                | Dispatch ROM2 |            |          |  |

|--------------|-----------------------------|----------------|---------------|------------|----------|--|

| Op I         | Opcode name                 | Value          | Op            | Opcode nan | ne Value |  |

| 000000       | R-format                    | 0110           | 100011        | lw         | 0011     |  |

| 000010       | jmp                         | 1001           | 101011        | SW         | 0101     |  |

| 000100       | beq                         | 1000           |               |            |          |  |

| 100011       | lw                          | 0010           |               |            |          |  |

| 101011       | SW                          | 0010           |               |            |          |  |

| State number |                             | Value of AddrC |               |            |          |  |

| 0            | Use increment               | ed state       |               |            | 3        |  |

| 1            | Use dispatch ROM1           |                |               |            |          |  |

| 2            |                             |                |               |            | 2        |  |

| 3            | Use increment               | ed state       |               |            | 3        |  |

| 4            | Replace state number by 0 0 |                |               |            |          |  |

| 5            | Replace state number by 0 0 |                |               |            |          |  |

| 6            | Use incremented state 3     |                |               |            |          |  |

| 7            | Replace state number by 0 0 |                |               |            |          |  |

| 8            | Replace state               |                |               |            | 0        |  |

| 9            | Replace state number by 0 0 |                |               |            |          |  |

## Microprogramming

| Label    | ALU<br>control | SRC1 | SRC2    | Register<br>control | Memory    | PCWrite<br>control | Sequencing |

|----------|----------------|------|---------|---------------------|-----------|--------------------|------------|

| Fetch    | Add            | PC   | 4       | 00.111.01           | Read PC   | ALU                | Sea        |

|          | Add            | PC   | Extshft | Read                |           |                    | Dispatch 1 |

| Mem1     | Add            | А    | Extend  |                     |           |                    | Dispatch 2 |

| LW2      |                |      |         |                     | Read ALU  |                    | Seq        |

|          |                |      |         | Write MDR           |           |                    | Fetch      |

| SW2      |                |      |         |                     | Write ALU |                    | Fetch      |

| Rformat1 | Func code      | А    | в       |                     |           |                    | Sea        |

|          |                |      |         | Write ALU           |           |                    | Fetch      |

| BEQ1     | Subt           | А    | В       |                     |           | ALUOut-cond        | Fetch      |

| JUMP1    |                |      |         |                     |           | Jump address       | Fetch      |

| Field name                    | Value        | Signals active                           | Comment                                                                                                                         |

|-------------------------------|--------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

|                               | Add          | ALUOp = 00                               | Cause the ALU to add.                                                                                                           |

| ALU control                   | Subt         | ALUOp = 01                               | Cause the ALU to subtract; this implements the compare for<br>branches                                                          |

|                               | Func code    | ALUOp = 10                               | Use the instruction's function code to determine ALU control.                                                                   |

| SRC1                          | PC           | ALUSrcA = 0                              | Use the PC as the first ALU input.                                                                                              |

|                               | A            | ALUSICA = 1                              | Register A is the first ALU input.                                                                                              |

|                               | В            | ALUSrcB = 00                             | Register B is the second ALU input.                                                                                             |

| SRC2                          | 4            | ALUSrcB = 01                             | Use 4 as the second ALU input.                                                                                                  |

|                               | Extend       | ALUS(cB = 10                             | Use output of the sign extension unit as the second ALU input.                                                                  |

|                               | Extshft      | ALUSrcB = 11                             | Use the output of the shift-by-two unit as the second ALU input.                                                                |

| Register<br>control<br>Memory | Read         |                                          | Read two registers using the rs and rt fields of the IR as the register<br>numbers and putting the data into registers A and B. |

|                               | Write ALU    | RegWrite,<br>RegDst = 1,<br>MemtoReg = 0 | Write a register using the rd field of the IR as the register number and<br>the contents of the ALUOut as the data.             |

|                               | Write MDR    | RegWrite,<br>RegDst = 0,<br>MemtoReg = 1 | Write a register using the rt field of the IR as the register number and<br>the contents of the MDR as the data.                |

|                               | Read PC      | MemRead,<br>lorD = 0                     | Read memory using the PC as address; write result into IR (and the MDR)                                                         |

|                               | Read ALU     | MemRead,<br>lorD = 1                     | Read memory using the ALUOut as address; write result into MDR.                                                                 |

|                               | Write ALU    | MemWrite,<br>lorD = 1                    | Write memory using the ALUOut as address, contents of B as the<br>data.                                                         |

| PC write control              | ALU          | PCSource = 00<br>PCWrite                 | Write the output of the ALU into the PC.                                                                                        |

|                               | ALUOut-cond  | PCSource = 01,<br>PCWriteCond            | If the Zero output of the ALU is active, write the PC with the contents<br>of the register ALUOut.                              |

|                               | jump address | PCSource = 10,<br>PCWrite                | Write the PC with the jump address from the instruction.                                                                        |

|                               | Seq          | AddrCtl = 11                             | Choose the next microinstruction sequentially.                                                                                  |

| Sequencing                    | Fetch        | AddrCtl = 00                             | Go to the first microinstruction to begin a new instruction.                                                                    |

|                               | Dispatch 1   | AddrCtl = 01                             | Dispatch using the ROM 1.                                                                                                       |

|                               | Dispatch 1   | Addreal = 01                             | Dispatch using the ROM 2                                                                                                        |

## Maximally vs. Minimally Encoded No encoding: 1 bit for each datapath operation faster, requires more memory (logic) used for Vax 780 — an astonishing 400K of memory! Lots of encoding: send the microinstructions through logic to get control signals uses less memory, slower Historical context of CISC: Too much logic to put on a single chip with everything else Use a ROM (or even RAM) to hold the microcode It's easy to add new instructions

16

## Microcode: Trade-offs

- Distinction between specification and implementation is blurred

Specification Advantages:

- Easy to design and write

- Design architecture and microcode in parallel

- Design architecture and microcode in paralle

- Implementation (off-chip ROM) Advantages

- Easy to change since values are in memory

- Can emulate other architectures

- Can make use of internal registers

- Implementation Disadvantages, SLOWER now that:

- Control is implemented on same chip as processor

ROM is no longer faster than RAM

- ROW IS no longer faster than RAW

- No need to go back and make changes

17

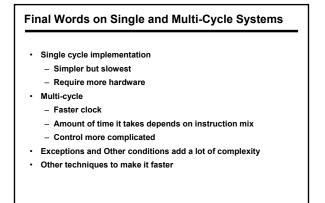

Conclusions on Chapter 5

Control is the most complex part

Can be hard-wired, ROM-based, or micro-programmed

Simpler instructions also lead to simple control

Just because machine is micro-programmed, we should not

add complicated instructions

Sometimes simple instructions are more effective than a

single complex instruction

More complex instructions may have to be maintained for

compatibility reasons