## Memories: Design Objectives

- Provide adequate storage capacity

- Four ways to approach this goal

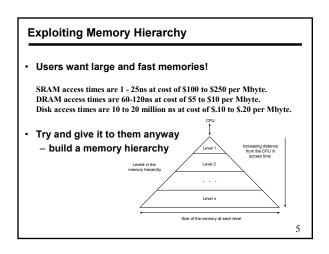

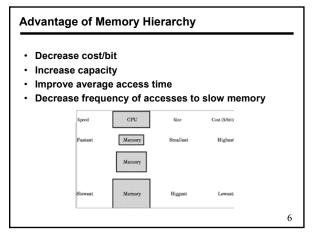

- Use of number of different memory devices with different cost/performance ratios

- Automatic space-allocation methods in hierarchy

2

- Development of virtual-memory concept

- Design of communication links

### **Memory Hierarchy and Access Time**

- ti is time for access at level i

- on-chip cache, off-chip cache, main memory, disk, tape

- N accesses

- ni satisfied at level i

- a higher level can always satisfy any access that is

- satisfied by a lower level - N = n1 + n2 + n3 + n4 + n5

- Hit Ratio

- number of accesses satisfied/number of accesses made

- Could be confusing

- For example for level 3 is it n3/N or (n1+n2+n3)/N or n3/(Nn1-n2)

- We will take the second definition

11

# Average Access Time ti is time for access at level i ni satisfied at level i hi is hit ratio at level i hi is hit ratio at level i hi is (n1 + n2 + ... + ni) /N We will also assume that data are transferred from level i+1 to level i before satisfying the request Total time = n1\*t1 + n2\*(t1+t2) + n3\*(t1+t2+t3) + n4\* (t1+t2+t3+t4) + n5\*(t1+t2+t3+t4+t5) Average time = Total time/N t(avr) = t1+t2\*(l-h1)+t3\*(1-h2)+t4\*(1-h3)+t5\*(1-h4) Total Cost = C1\*S1+C2\*S2+C3\*S3+C4\*S4+C5\*S5

8

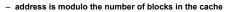

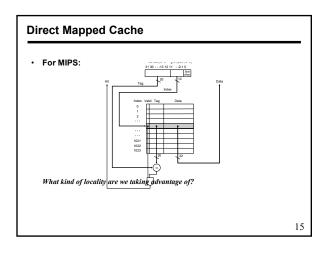

# **Direct Mapped Cache**

Mapping:

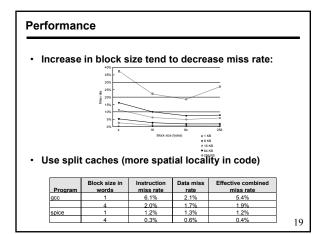

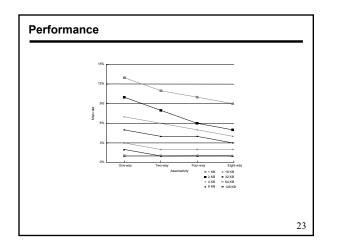

# Performance

· Simplified model:

execution time=(execution cycles + stall cycles)\*cct • stall cycles= #of instructions\*miss ratio\*miss penalty • Two ways of improving performance: – decreasing the miss ratio – decreasing the miss penalty What happens if we increase block size?

### Decreasing miss penalty with multilevel caches

· Add a second level cache:

- often primary cache is on the same chip as the processor

- use SRAMs to add another cache above primary memory (DRAM)

- miss penalty goes down if data is in 2nd level cache

Example:

CPI of 1.0 on a 500Mhz machine with a 5% miss rate, 200ns DRAM access

Adding 2nd level cache with 20ns access time decreases miss rate to 2%

Using multilevel caches:

- try and optimize the hit time on the 1st level cache

- try and optimize the miss rate on the 2nd level cache

20