| 31 |         | 26 25 |       | 21 | 20  |       | 16 | 15 | 11     | 10      | 6      | 5   |            |

|----|---------|-------|-------|----|-----|-------|----|----|--------|---------|--------|-----|------------|

|    | LW      |       | REG 1 |    |     | REG 2 |    |    | LOAD A | DDRESS  |        |     | OFFSE      |

| 31 |         | 26 25 |       | 21 | 20  |       | 16 | 15 | 11     | 10      | 6      | 5   |            |

|    | SW      |       | REG 1 |    |     | REG 2 |    |    | STORE  | ADDRESS |        |     | OFFSE      |

| 31 |         | 26 25 |       | 21 | 20  |       | 16 | 15 | 11     | 10      | 6      | 5   |            |

|    | R-TYPE  |       | REG 1 |    |     | REG 2 |    |    | DST    | SHIFT A | MOUNT  | ADI | )/AND/OR/S |

| 31 | :       | 26 25 |       | 21 | 20  |       | 16 | 15 | 11     | 10      | 6      | 5   |            |

|    | BEQ/BNE |       | REG 1 |    |     | REG 2 |    |    | BRANC  | HADDRE  | ss     |     | OFFSE      |

| 31 |         | 26 25 |       | 21 | 20  |       | 16 | 15 | 11     | 10      | 6      | 5   |            |

|    | JUMP    |       |       |    | JUM | Р     |    |    |        |         | ADDRES | s   |            |

| Operation                   | n for Each li               | nstruction                     |                             |                 |

|-----------------------------|-----------------------------|--------------------------------|-----------------------------|-----------------|

| LW:                         | SW:                         | R-Type:                        | BR-Type:                    | JMP-Type:       |

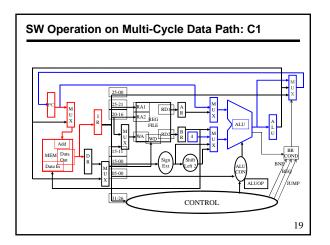

| 1. READ INST                | 1. READ INST                | 1. READ INST                   | 1. READ INST                | 1. READ<br>INST |

| 2. READ REG 1<br>READ REG 2 | 2. READ REG 1<br>READ REG 2 | 2. READ REG 1<br>READ REG 2    | 2. READ REG 1<br>READ REG 2 | 2.              |

| 3. ADD REG 1 +<br>OFFSET    | 3. ADD REG 1 +<br>OFFSET    | 3. OPERATE on<br>REG 1 / REG 2 | 3. SUB REG 2<br>from REG 1  | 3.              |

| 4. READ MEM                 | 4. WRITE MEM                | 4.                             | 4.                          | 4.              |

| 5. WRITE REG2               | 5.                          | 5. WRITE DST                   | 5.                          | 5.              |

|                             |                             |                                |                             | 4               |

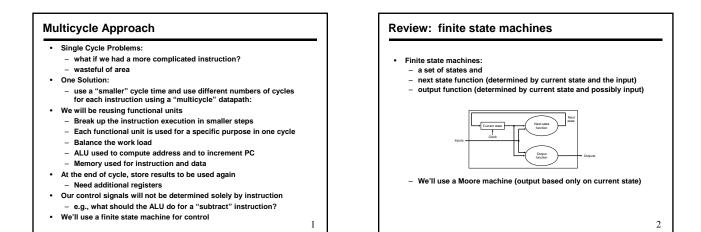

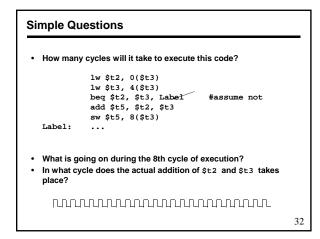

### **Five Execution Steps**

- Instruction Fetch

- Instruction Decode and Register Fetch

- Execution, Memory Address Computation, or Branch Completion

- Memory Access or R-type instruction completion

- Write-back step

**INSTRUCTIONS TAKE FROM 3 - 5 CYCLES!**

| <ul> <li>Use PC to get instruction and put it in the Instruction Register.</li> <li>Increment the PC by 4 and put the result back in the PC.</li> <li>Can be described succinctly using RTL "Register-Transfer Language"         IR = Memory[PC];         PC = PC + 4;     </li> <li>Can we figure out the values of the control signals?</li> </ul> | ер   | 1: Instruction Fetch                                  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------|--|

| PC = PC + 4;                                                                                                                                                                                                                                                                                                                                         | Inci | rement the PC by 4 and put the result back in the PC. |  |

| Can we figure out the values of the control signals?                                                                                                                                                                                                                                                                                                 |      |                                                       |  |

|                                                                                                                                                                                                                                                                                                                                                      | Can  | we figure out the values of the control signals?      |  |

| What is the advantage of updating the PC now?                                                                                                                                                                                                                                                                                                        | Who  | at is the advantage of updating the PC now?           |  |

|                                                                                                                                                                                                                                                                                                                                                      |      |                                                       |  |

|                                                                                                                                                                                                                                                                                                                                                      |      |                                                       |  |

|                                                                                                                                                                                                                                                                                                                                                      |      |                                                       |  |

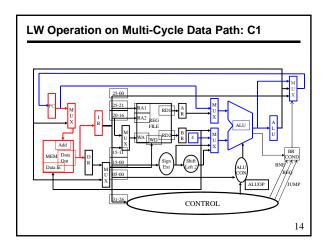

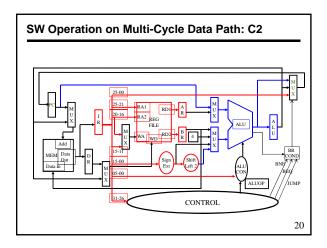

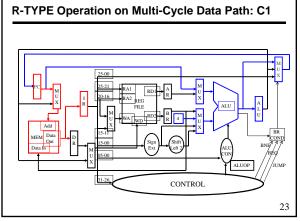

#### Step 2: Instruction Decode and Register Fetch

Read registers rs and rt in case we need them

Compute the branch address in case the instruction is a branch

RTL:

A = Reg[IR[25-21]];

B = Reg[IR[20-16]];

ALUOut = PC + (sign-extend(IR[15-0]) << 2);</li>

We aren't setting any control lines based on the instruction type (we are busy "decoding" it in our control logic)

8

10

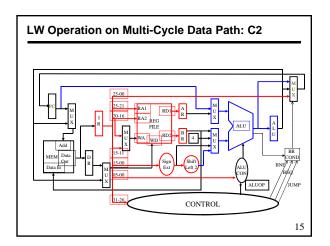

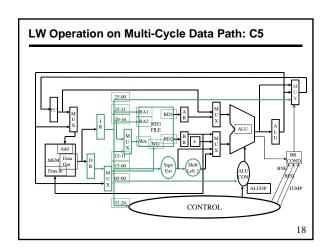

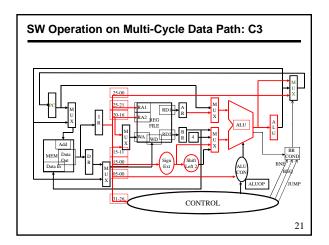

- Step 3 (instruction dependent)

ALU is performing one of three functions, based on instruction type

Memory Reference:

ALUOut = A + sign-extend(IR[15-0]);

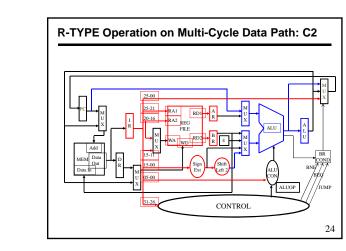

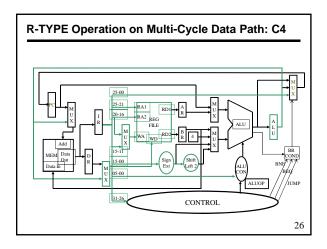

R-type:

ALUOut = A op B;

ALUOut = A op B;

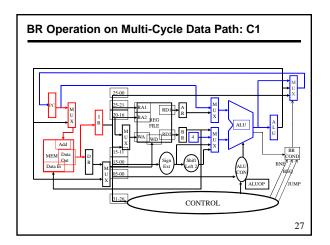

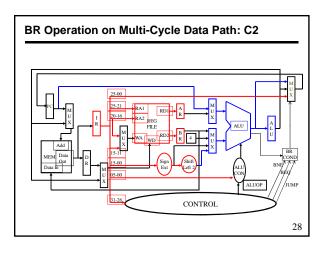

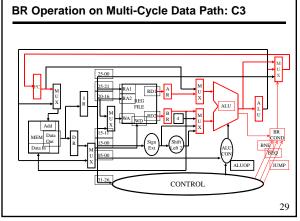

- Branch:

if (A==B) PC = ALUOut;

9

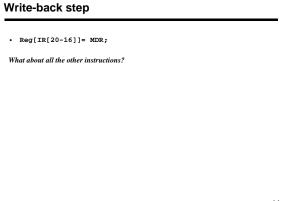

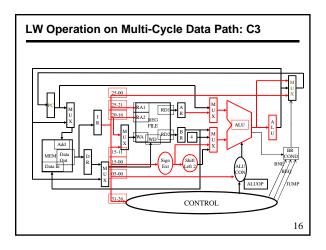

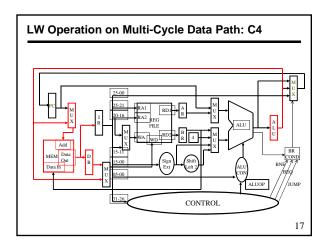

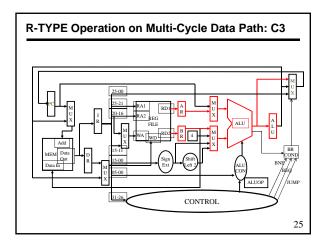

# Step 4 (R-type or memory-access)

- Loads and stores access memory

MDR = Memory[ALUOut];

- or Memory[ALUOut] = B;

- R-type instructions finish

Reg[IR[15-11]] = ALUOut;

The write actually takes place at the end of the cycle on the edge

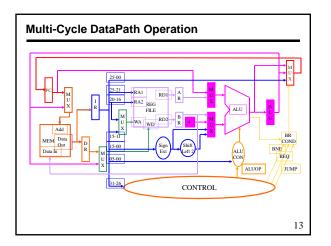

| Step name                                                     | Action for R-type<br>instructions | Action for memory-reference<br>instructions                                | Action for<br>branches         | Action for<br>jumps              |

|---------------------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------|--------------------------------|----------------------------------|

| Instruction fetch                                             |                                   | IR = Memory[PC]<br>PC = PC + 4                                             |                                |                                  |

| Instruction<br>decode/register fetch                          |                                   | A = Reg [IR[25-21]<br>B = Reg [IR[20-16]<br>ALUOut = PC + (sign-extend (IF |                                |                                  |

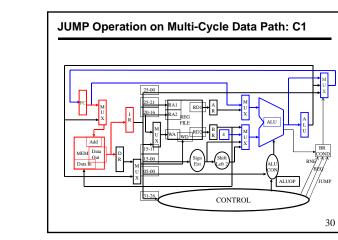

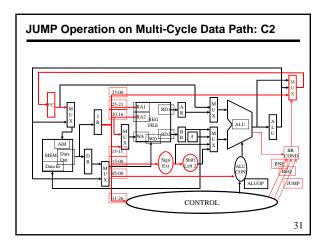

| Execution, address<br>computation, branch/<br>iump.completion | ALUOut = A op B                   | ALUOut = A + sign-extend<br>(IR[15-0])                                     | if (A ==B) then<br>PC = ALUOut | PC = PC [31-28]<br>(IR[25-0]<<2) |

| Memory access or R-type<br>completion                         | Reg [IR[15-11]] =<br>ALUOut       | Load: MDR = Memory[ALUOut]<br>or<br>Store: Memory [ALUOut] = B             |                                |                                  |

| Memory read completion                                        |                                   | Load: Reg[IR[20-16]] = MDR                                                 |                                |                                  |

11

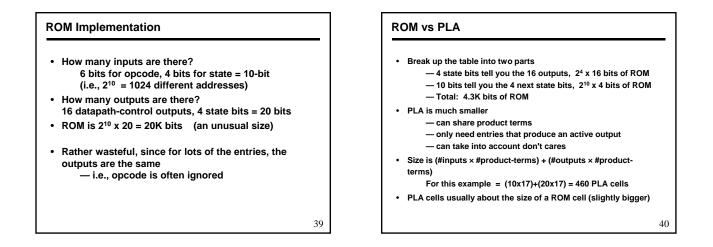

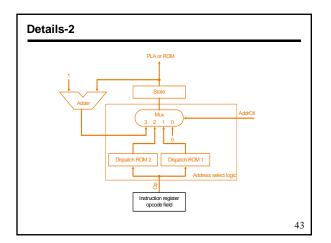

|              | lispatch ROM1 |             |              | Dispatch ROM2 | M2              |  |

|--------------|---------------|-------------|--------------|---------------|-----------------|--|

| Op           | Opcode name   | Value       | Op           | Opcode name   | Value           |  |

| 000000       | R-format      | 0110        | 100011       | lw            | 0011            |  |

| 000010       | jmp           | 1001        | 101011       | SW            | 0101            |  |

| 000100       | beq           | 1000        |              |               |                 |  |

| 100011       | lw            | 0010        |              |               |                 |  |

| 101011       | SW            | 0010        |              |               |                 |  |

| State number |               | Address-co  | ntrol action | 1             | /alue of AddrCt |  |

| 0            | Use incremen  |             | 3            |               |                 |  |

| 1            | Use dispatch  |             | 1            |               |                 |  |

| 2            | Use dispatch  |             | 2            |               |                 |  |

| 3            | Use incremen  |             | 3            |               |                 |  |

| 4            | Replace state |             | 0            |               |                 |  |

| 5            | Replace state |             | 0            |               |                 |  |

| 6            | Use incremen  | ted state   |              | 3             |                 |  |

| 7            | Replace state | number by 0 |              |               | 0               |  |

| 8            | Replace state | number by 0 |              |               | 0               |  |

| 9            | Replace state | number by 0 |              |               | 0               |  |

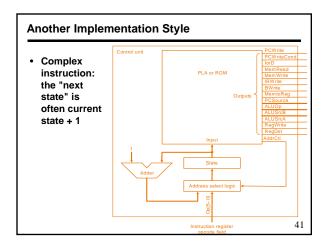

| – app    |           | e if hu | ndred    | ds of opc   |            | odes, cycl                  |            |

|----------|-----------|---------|----------|-------------|------------|-----------------------------|------------|

| Label    | ALU       |         | SRC2     | Register    | Memory     | PCWrite<br>control          | Sequencing |

| Fetch    | Add       | PC      | 4        |             | Read PC    | ALU                         | Seq        |

|          | Add       | PC      | Extshft  | Read        |            |                             | Dispatch 1 |

| Mem1     | Add       | А       | Extend   |             |            |                             | Dispatch 2 |

| LW2      |           |         |          |             | Read ALU   |                             | Seq        |

|          |           |         |          | Write MDR   |            |                             | Fetch      |

| SW2      |           |         |          |             | Write ALU  |                             | Fetch      |

| Rformat1 | Func code | А       | в        |             |            |                             | Sea        |

|          |           |         |          | Write ALU   |            |                             | Fetch      |

| BEQ1     | Subt      | А       | в        |             |            | ALUOut-cond                 | Fetch      |

| JUMP1    |           |         |          |             |            | Jump address                | Fetch      |

|          |           | entatio | ons of i | the same of | urchitectu | Jump address<br>re have the |            |

| Field name       | Value        | Signals active | Comment                                                                  |      |

|------------------|--------------|----------------|--------------------------------------------------------------------------|------|

| There have       | Add          | ALUOp = 00     | Cause the ALLI to add                                                    |      |

| ALU control      | Subt         | ALUOp = 01     | Cause the ALU to subtract: this implements the compare for               |      |

|                  |              |                | branches.                                                                |      |

|                  | Func code    | ALUOp = 10     | Use the instruction's function code to determine ALU control.            |      |

| SRC1             | PC           | ALUSrcA = 0    | Use the PC as the first ALU input.                                       |      |

|                  | A            | ALUSrcA = 1    | Register A is the first ALU input.                                       |      |

|                  | В            | ALUSrcB = 00   | Register B is the second ALU input.                                      |      |

| SRC2             | 4            | ALUSrcB = 01   | Use 4 as the second ALU input.                                           |      |

|                  | Extend       | ALUSrcB = 10   | Use output of the sign extension unit as the second ALU input.           |      |

|                  | Extshft      | ALUSrcB = 11   | Use the output of the shift-by-two unit as the second ALU input.         |      |

|                  | Read         |                | Read two registers using the rs and rt fields of the IR as the register  |      |

|                  |              |                | numbers and putting the data into registers A and B.                     |      |

|                  | Write ALU    | RegWrite,      | Write a register using the rd field of the IR as the register number and |      |

| Register         |              | RegDst = 1,    | the contents of the ALUOut as the data.                                  |      |

| control          |              | MemtoReg = 0   |                                                                          |      |

|                  | Write MDR    | RegWrite,      | Write a register using the rt field of the IR as the register number and |      |

|                  |              | RegDst = 0,    | the contents of the MDR as the data.                                     |      |

|                  |              | MemtoReg = 1   |                                                                          |      |

|                  | Read PC      | MemRead,       | Read memory using the PC as address; write result into IR (and           |      |

|                  |              | lorD = 0       | the MDR).                                                                |      |

| Memory           | Read ALU     | MemRead,       | Read memory using the ALUOut as address; write result into MDR.          |      |

|                  |              | lorD = 1       |                                                                          |      |

|                  | Write ALU    | MemWrite,      | Write memory using the ALUOut as address, contents of B as the           |      |

|                  |              | lorD = 1       | data.                                                                    |      |

|                  | ALU          | PCSource = 00  | Write the output of the ALU into the PC.                                 |      |

|                  |              | PCWrite        |                                                                          |      |

| PC write control | ALUOut-cond  | PCSource = 01, | If the Zero output of the ALU is active, write the PC with the contents  |      |

|                  |              | PCWriteCond    | of the register ALUOut.                                                  |      |

|                  | jump address | PCSource = 10, | Write the PC with the jump address from the instruction.                 |      |

|                  |              | PCWrite        |                                                                          |      |

|                  | Seq          | AddrCtl = 11   | Choose the next microinstruction sequentially.                           |      |

| Sequencing       | Fetch        | AddrCtl = 00   | Go to the first microinstruction to begin a new instruction.             |      |

|                  | Dispatch 1   | AddrCtl = 01   | Dispatch using the ROM 1.                                                | - 40 |

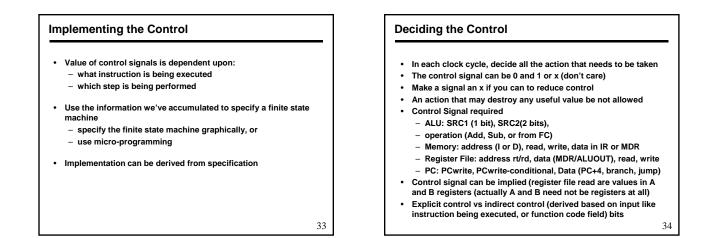

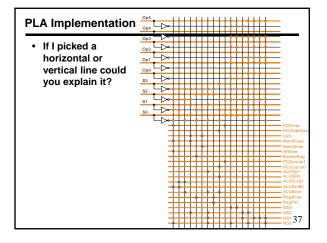

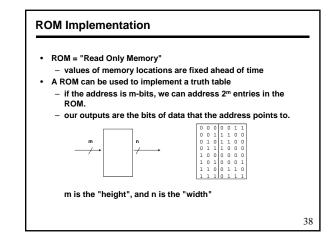

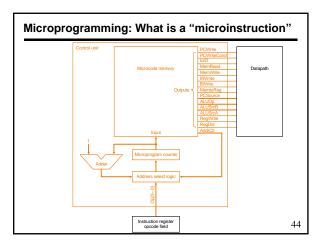

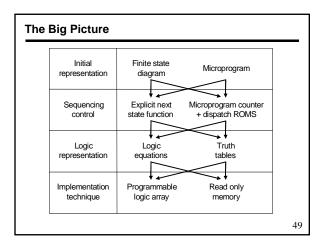

#### Maximally vs. Minimally Encoded

- No encoding:

- 1 bit for each datapath operation

- faster, requires more memory (logic)

- used for Vax 780 an astonishing 400K of memory!

- · Lots of encoding:

- send the microinstructions through logic to get control signals

- uses less memory, slower

- Historical context of CISC:

- Too much logic to put on a single chip with everything else

- Use a ROM (or even RAM) to hold the microcode

- It's easy to add new instructions

47

### Microcode: Trade-offs

- Distinction between specification and implementation is blurred

- Specification Advantages:

- Easy to design and write

- Design architecture and microcode in parallel

- Implementation (off-chip ROM) Advantages

- Easy to change since values are in memory

- Can emulate other architectures

- Can make use of internal registers

- Implementation Disadvantages, SLOWER now that:

- Control is implemented on same chip as processor

- ROM is no longer faster than RAM

- No need to go back and make changes

48

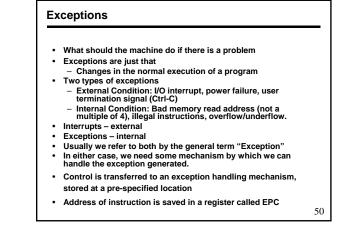

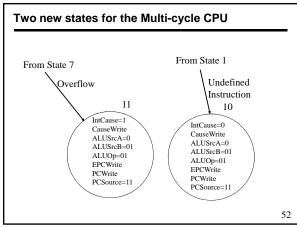

#### How Exceptions are Handled We need two special registers EPC: 32 bit register to hold address of current instruction From State 7 Cause: 32 bit register to hold information about the type of exception that has occurred. Overflow Simple Exception Types Undefined Instruction 11 Arithmetic Overflow IntCause=1 Another type is Vectored Interrupts CauseWrite - Do not need cause register ALUSrcA=0 ALUSrcB=01 Appropriate exception handler jumped to from a vector ALUOp=01 EPCWrite PCWrite PCSource=11 51

## Vectored Interrupts/Exceptions

- Address of exception handler depends on the problem

- Undefined Instruction C0 00 00 00

- Arithmetic Overflow C0 00 00 20

- Addresses are separated by a fixed amount, 32 bytes in MIPS

- PC is transferred to a register called EPC

- If interrupts are not vectored, then we need another register to store the cause of problem

- In what state what exception can occur?

53

### Final Words on Single and Multi-Cycle Systems

- Single cycle implementation

- Simpler but slowest

- Require more hardware

- Multi-cycle

- Faster clock

- Amount of time it takes depends on instruction mix

- Control more complicated

- · Exceptions and Other conditions add a lot of complexity

- Other techniques to make it faster