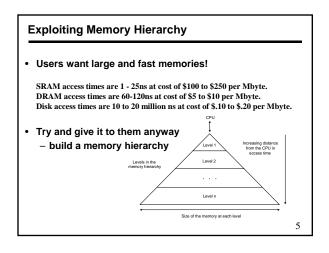

# Memory Hierarchy and Access Time

- ti is time for access at level i

- on-chip cache, off-chip cache, main memory, disk, tape

- N accesses

- ni satisfied at level i

- a higher level can always satisfy any access that is satisfied by a lower level

N = n1 + n2 + n3 + n4 + n5

- Hit Ratio

- number of accesses satisfied/number of accesses made

- Could be confusing

For example for level 3 is it n3/N or (n1+n2+n3)/N or n3/(N-

- n1-n2)

- We will take the second definition

11

# Average Access Time

- ti is time for access at level i

- ni satisfied at level i

- hi is hit ratio at level i

- hi = (n1 + n2 + ...+ ni) /N

- We will also assume that data are transferred from level i+1 to level i before satisfying the request

- Total time = n1\*t1 + n2\*(t1+t2) + n3\*(t1+t2+t3) + n4\* (t1+t2+t3+t4) + n5\*(t1+t2+t3+t4+t5)

- Average time = Total time/N

- t(avr) = t1+t2\*(I-h1)+t3\*(1-h2)+t4\*(1-h3)+t5\*(1-h4)

- Total Cost = C1\*S1+C2\*S2+C3\*S3+C4\*S4+C5\*S5

- 12

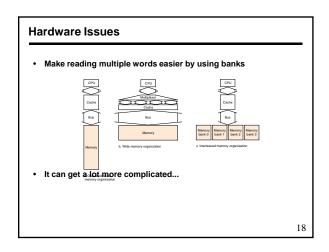

### Decreasing miss penalty with multilevel caches

Add a second level cache:

- often primary cache is on the same chip as the processor

- use SRAMs to add another cache above primary memory (DRAM)

- miss penalty goes down if data is in 2nd level cache

Example:

CPI of 1.0 on a 500Mhz machine with a 5% miss rate, 200ns DRAM access

Adding 2nd level cache with 20ns access time decreases miss rate to 2%

Using multilevel caches:

- try and optimize the hit time on the 1st level cache

- try and optimize the miss rate on the 2nd level cache

# **Replacement Policies**

- Replacement Policies in Multi-way Set Associative caches

- Random: Replace any line arbitrarily - Least Recently Used (LRU): Find the least recently used line to

- replace

- Keep Most Recently Used (MRU): Keep the last used line in the set and replace any other randomly

- LRU performs the best

- MRU does equally well

### LRU Scheme

- We explain LRU with an example of a 4-way set associative cache

- Associate a 2-bit counter with each line (log k bit for k-way cache)

- · Initially all lines are invalid

- For a miss bring a new line in an invalid line, make it valid, set its counter to zero, increment all other counters

- If no invalid line, replace the line with counter value = 3, set its counter to zero, increment all other counters

- · For a hit, set the accessed line's counter to zero and increment counters of those lines whose values is smaller than the accessed line Try this algorithm for an examples where lines read are 0, 64, 128, 64,

- 192, 256, 128, 0, 256, 192, 64...

- There are 64 lines in each cache and it is 4-way set associative

# 32

34

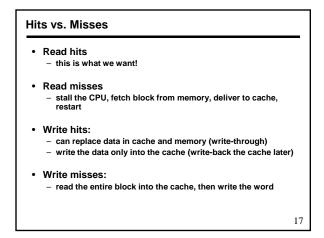

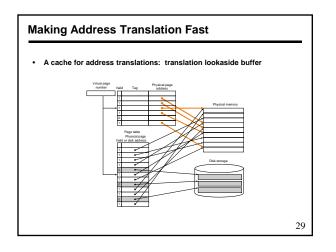

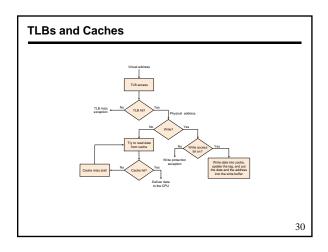

### Reading or Writing a Memory word

- Check the address in TLB

- If not there, get the physical translation and also store the entry in TLB Penalty 40-50 cycles

- If page itself is not present, page fault occurs

- Read the page, update page table and TLB Penalty 100's of thousands cycles

- · Once physical address is there If there, perform read or write in cache If cache miss

- Read the line in cache for read

- May need to replace a dirty or clean line

- · Penalty 20-40 cycles

- For Write read the line if write allocate, else write around

- If cache hit read or write in cache

- Also write in main memory if write through

33

31

# A Big Example

- Instruction Frequency: LW(20%), SW(10%), R(50%), BR(15%), J(5%)

- Branch Penalty: 3 cycles on 20% mis-predictions = 15\*0.20\*3 = 9 cycles Data Cache 1: Miss rate 10% (of load/store), write back, write around, 50% dirty replacement, penalty for reading or writing a line 20 cycles Load penalty = 20\*0.10\*0.50\*20 + 20\*0.10\*0.50\*(20+20) = 60 cycles Store Penalty = 0 (because of write around, otherwise will be 30)

- Data Cache 2: Miss rate 5% (of load/store), write back, write allocation, 50% dirty replacement, penalty for reading or writing a line 100 cycles Load penalty = 20\*0.05\*0.5\*100 + 20\*0.05\*0.5\*(100+100) = 150 cycles

- Store Penalty = 10\*0.05\*0.5\*100 + 10\*0.05\*0.5\*(100+100) = 75 cycles TLB: Miss Rate 2% (of load/store), Miss Penalty 100 cycles

- Total Penalty = (20+10)\*0.02\*100 = 60 cycles

- Page faults: 0.01% (of load/store), Penalty 300,000 cycles Total Penalty = (20+10)\*0.0001\*300,000 = 900 cycles

- Total Time = 100+9+60+150+75+60+900 = 1354 cycles, or CPI=13.54 Notice that miss rates can be spacified per instruction or per load/store

# Misses and Replacement Policies

3 C Misses

•

- Compulsory: Miss will have to occur on first read (or write) - Capacity: A line is replaced and then brought back

- Conflict: a miss occurs as some other line is occupying that line Example Suppose we read line a first time (no line is in cache), then

- read line b that replaces line a, and then read line a again The first and second misses are compulsory, second miss is also

- capacity and conflict, and the third miss is capacity (and also conflict) The terminology can be confusing here

- The first read is always classified as compulsory

- The replacement and read back is conflict if there was place in cache elsewhere but you had to bring it at that place due to mapping

- If there was no place at all then it is capacity miss (like cache is full in a fully associative cache)

35

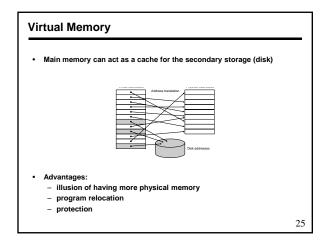

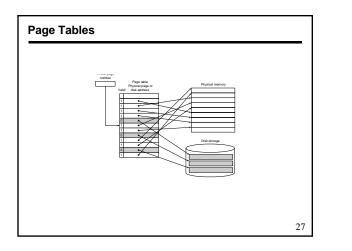

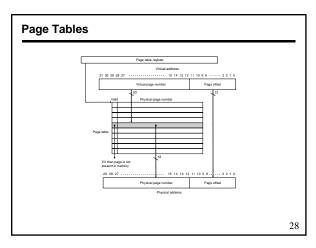

Virtual Memory: Other Translation Schemes · In a single-level translation 32 bit virtual address 4KB Page size (12 bit address in each page) Leaves 20-bit page address => 1 Million Pages =>4MB for Table One alternate is to only have a limited size page table with Hi and Lo Check But program use many addresses segments Alternate is to have a two level page table Divide page addresses in two parts of 10 bits each There are 1K tables of 1K entries each (total is still 1M entries) Most significant 10 bits points to a table (with 1K entries, each 4 bytes long, a total of 4KB that fits in a page) that contains the address of that part of table Least significant 10 bits are used to access a particular entry in the selected table We only need to keep the first table (pointing to real tables) and some of the second level tables in memory

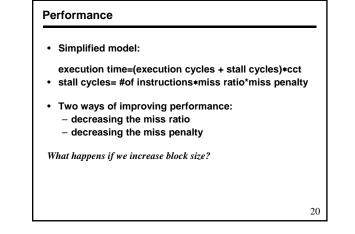

# Some Issues

- Processor speeds continue to increase very fast

\_\_\_\_\_much faster than either DRAM or disk access times

- Design challenge: dealing with this growing disparity

- Trends:

- synchronous SRAMs (provide a burst of data)

- redesign DRAM chips to provide higher bandwidth or processing

- restructure code to increase locality

use prefetching (make cache visible to ISA)

38