## **Combinational Circuits & Sequential Circuits**

Two main classes of circuits:

- 1. Combinational circuits

- Circuits without memory

- Outputs depend only on current input values

- 2. Sequential Circuits (also called Finite State Machine)

- Circuits with memory

- Memory elements to store the state of the circuit

- The state represents the input sequence in the past

- Outputs depend on both circuit state and current inputs

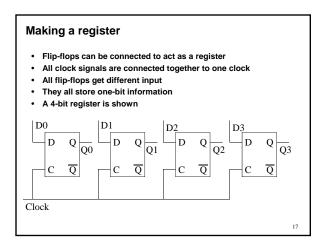

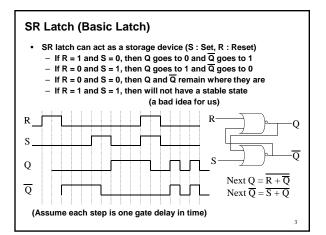

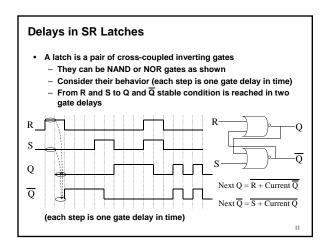

## Latches, Flip-Flops and Registers These are devices to store information. Latches and Flip-Flops – single bit Registers – multiple bits Basic structure for storing a bit: a pair of cross-coupled inverters maintain a binary state indefinitely Not useful as it lacks some practical means for changing its state Usually constructed by two cross-coupled NOR (or NAND) gates to provide some control signals.

## JK Flip-Flop Combines the behaviors of SR and T Flip-Flops It behaves as the SR flip-flop where J=S and K=R (except J=K=1) ٠ • If J=K=1, it toggles its state like the T flip-flop J κ Next Q 0 0 Q $D = J.\overline{Q} + K'.Q$ 0 0 1 1 0 1 D Q Q 1 Q С ( Q С Κ Q Graphical Symbol

- Circuit timing is a very important consideration in the design of any electronic systems

- So far, we have ignore any timing problems

- We will consider the following timing issues: For Flip-flops:

- Set-up time

- Hold time

- Propagation delay

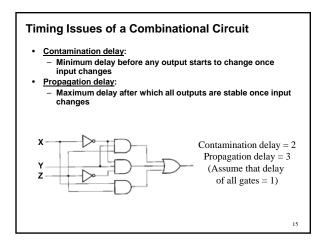

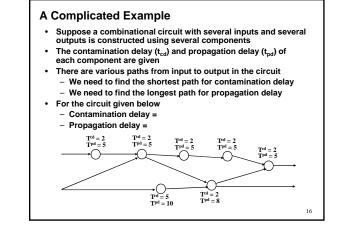

- For Combinational circuits:

- Contamination delay - Propagation delay

- For Sequential circuits:

- Combining the timing of FFs and combinational circuits

10

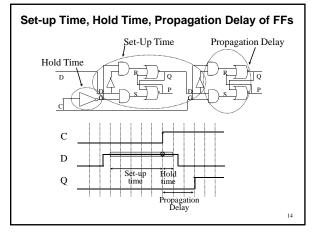

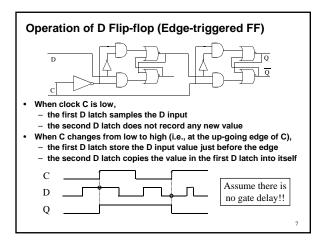

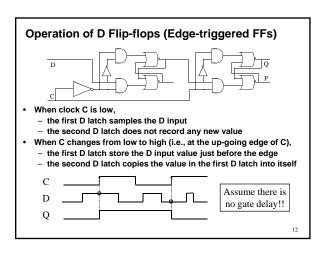

## **Timing Issues in D Flip-flops**

- Set-up time:

- Changes in input D propagate through many gates to the AND gates of the second D latch

- Therefore D should be stable (i.e., set up) for at least five gate delays before the clock changes from low to high

- Hold time:

- When clock changes from low to high, the first latch may still sample for one gate delay time.

- Therefore, D should remain stable (i.e., hold) for at least one gate delay even after clock changes

- Propagation delay:

- After clock changes from low to high, the value fetched by the second latch takes *three* gate delays to propagate to the output Q

13