## AVR072: Accessing 16-bit I/O Registers

## **Features**

- Routines for Accessing 16-bits I/O Registers

- Macros Included for AVR- and IAR Assembler

## **Description**

All mid- and high-range AVR devices include a 16-bit Timer and some also include a 10-bit A/D Converter. These I/O modules have 16-bit registers that can be accessed from the AVR core using the *in* and *out* instructions. Since the AVR microcontroller has an 8-bit I/O bus the access to the I/O Register must be performed in two instruction cycles. An interrupt can occur between the instructions. If the interrupt function accesses the same resources (16-bit Timer or ADC) the 16-bit I/O Register access must be made an atomic operation, i.e., an operation that cannot be interrupted.

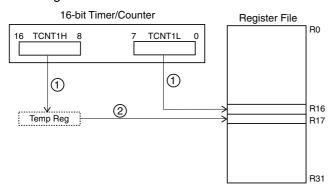

I/O modules with 16-bit Registers include a temporary register for the high byte (bit 15 to 8). Note that the 16-bit Timer (Timer1) has only one temporary register that is shared between all it's 16-bit register pairs. A 16-bit I/O read is normally done like this:

```

Cycle 1: in r16, TCNT1L ;Reading low byte into r16, this triggers the high ; byte to be latched in the temporary shadow ; register.

Cycle 2: in r17, TCNT1H ;Reading high byte from the temporary register.

```

Figure 1. 16-bit I/O Register Read<sup>(1)</sup>

Note: 1. Circled numbers indicate cycle number.

If an interrupt occurs between the two instructions for any of the operations, and the interrupt handler access any of the Timer1's low bytes, the temporary register might change it's value. Returning from the interrupt the AVR core now reads the corrupted value into register r17.

# 8-bit **AVR**® Microcontroller

## Application Note

Rev. 1493B-AVR-05/02

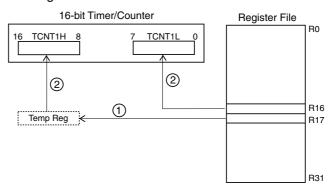

## A 16-bit I/O write is done as follow:

```

;r17 contains the high byte while r16 contains ;the low byte that is to be written.

Cycle 1: out TCNT1H, r17 ;Writing the high byte to the temporary register.

Cycle 2: out TCNT1L, r16 ;Writing both the low byte and the temporary ;register into the I/O Register.

```

Figure 2. 16-bit I/O Register Write<sup>(1)</sup>

Note: 1. Circled numbers indicate cycle number.

Note that the read and the write operation differ in the order the high and low I/O Register is accessed. If the order is reversed, the high value will be incorrectly read or written.

## Solution

To avoid the situations described above, the following macros for the AVR assembler and the IAR C compiler can be used

### **AVR Assembler Macros**

```

.macro outw

cli

out

@0, @1

@0-1, @2

out

sei

.endmacro

.macro

inw

cli

in

@1, @2-1

@0, @2

in

sei

.endmacro

.include "8515def.inc"

r17, r16, TCNT1H

; Reads the counter value (high, low, adr)

TCNT1H, r17, r16

; Writes the counter value (adr, high, low)

IAR C MACROS

#include <ina90.h>

#define outw( ADDRESS, VAL ) \

{\

CLI();

ADDRESS = VAL; \

_SEI();\

#define inw( ADDRESS, VAL ) \

CLI();

VAL = ADDRESS; \

SEI();\

#include <io8515.h>

```

## Usage

Usage

####

## **Notes**

Notes: 1. The outw and the inw macros uses four instruction cycles which is the same amount of cycles as the ret instruction uses. Doing so the macros will not increase the worst case interrupt response time.

2. The macros will not work for setting the EEPROM address since the address can not be changed during write operation. This will lead to corruption of the data written.

## **Atmel Headquarters**

Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 487-2600

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

## Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

## **Atmel Operations**

## Memory

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 2-40-18-18-18 FAX (33) 2-40-18-19-60

### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4-42-53-60-00 FAX (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland TEL (44) 1355-803-000 FAX (44) 1355-242-743

#### RF/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany TEL (49) 71-31-67-0 FAX (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-76-58-30-00 FAX (33) 4-76-58-34-80

e-mail

literature@atmel.com

Web Site http://www.atmel.com

## © Atmel Corporation 2002.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

ATMEL® and AVR® are the registered trademarks of Atmel.

Other terms and product names may be the trademarks of others.