# Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC Wrapper v1.4

# **Getting Started Guide**

UG340 March 24, 2008

Xilinx is disclosing this Specification to you solely for use in the development of designs to operate on Xilinx FPGAs. Except as stated herein, none of the Specification may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Any unauthorized use of this Specification may violate copyright laws, trademark laws, the laws of privacy and publicity, and communications regulations and statutes.

Xilinx does not assume any liability arising out of the application or use of the Specification; nor does Xilinx convey any license under its patents, copyrights, or any rights of others. You are responsible for obtaining any rights you may require for your use or implementation of the Specification. Xilinx reserves the right to make changes, at any time, to the Specification as deemed desirable in the sole discretion of Xilinx. Xilinx assumes no obligation to correct any errors contained herein or to advise you of any correction if such be made. Xilinx will not assume any liability for the accuracy or correctness of any engineering or technical support or assistance provided to you in connection with the Specification.

THE SPECIFICATION IS PROVIDED "AS IS" WITH ALL FAULTS, AND THE ENTIRE RISK AS TO ITS FUNCTION AND IMPLEMENTATION IS WITH YOU. YOU ACKNOWLEDGE AND AGREE THAT YOU HAVE NOT RELIED ON ANY ORAL OR WRITTEN INFORMATION OR ADVICE, WHETHER GIVEN BY XILINX, OR ITS AGENTS OR EMPLOYEES. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE SPECIFICATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND NONINFRINGEMENT OF THIRD-PARTY RIGHTS.

IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOST DATA AND LOST PROFITS, ARISING FROM OR RELATING TO YOUR USE OF THE SPECIFICATION, EVEN IF YOU HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. THE TOTAL CUMULATIVE LIABILITY OF XILINX IN CONNECTION WITH YOUR USE OF THE SPECIFICATION, WHETHER IN CONTRACT OR TORT OR OTHERWISE, WILL IN NO EVENT EXCEED THE AMOUNT OF FEES PAID BY YOU TO XILINX HEREUNDER FOR USE OF THE SPECIFICATION. YOU ACKNOWLEDGE THAT THE FEES, IF ANY, REFLECT THE ALLOCATION OF RISK SET FORTH IN THIS AGREEMENT AND THAT XILINX WOULD NOT MAKE AVAILABLE THE SPECIFICATION TO YOU WITHOUT THESE LIMITATIONS OF LIABILITY.

The Specification is not designed or intended for use in the development of on-line control equipment in hazardous environments requiring fail-safe controls, such as in the operation of nuclear facilities, aircraft navigation or communications systems, air traffic control, life support, or weapons systems ("High-Risk Applications"). Xilinx specifically disclaims any express or implied warranties of fitness for such High-Risk Applications. You represent that use of the Specification in such High-Risk Applications is fully at your risk.

© 2006-2008 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

#### Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC Wrapper Getting Started Guide

The following table shows the revision history for this document.

|          | Version | Revision                                                                  |

|----------|---------|---------------------------------------------------------------------------|

| 10/23/06 | 1.1     | Initial Xilinx release.                                                   |

| 2/15/07  | 2.1     | Update for version 1.2 of the core; Xilinx tools 9.1i.                    |

| 5/5/07   | 3.1     | Update for version 1.3 of the core; early access only version.            |

| 8/8/07   | 4.1     | Update for full version 1.3 release of the core.                          |

| 3/24/08  | 5.1     | Update to core version 1.4; Xilinx tools 10.1; Virtex-5 FPGA FXT support. |

# Table of Contents

| Schedule of Figures                                                                                                                      | 7         |

|------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Preface: About This Guide                                                                                                                |           |

| Contents                                                                                                                                 | q         |

| Conventions                                                                                                                              |           |

| Typographical                                                                                                                            |           |

| Online Document                                                                                                                          |           |

| Chapter 1: Introduction                                                                                                                  |           |

| System Requirements                                                                                                                      | 13        |

| About the Ethernet MAC Wrapper Core                                                                                                      |           |

| Designs Using RocketIO Transceivers                                                                                                      |           |

| Recommended Design Experience                                                                                                            |           |

| Additional Resources                                                                                                                     |           |

|                                                                                                                                          |           |

| Technical Support                                                                                                                        |           |

| Feedback                                                                                                                                 |           |

| Ethernet MAC Wrapper                                                                                                                     |           |

| Document                                                                                                                                 | 14        |

| Chapter 2: Quick Start Example Design                                                                                                    |           |

| Overview                                                                                                                                 | 15        |

| Generating the Ethernet MAC Wrapper                                                                                                      |           |

| Implementing the Example Design                                                                                                          |           |

| Running the Simulation                                                                                                                   |           |

| Functional Simulation                                                                                                                    |           |

| Timing Simulation                                                                                                                        |           |

| What's Next?                                                                                                                             |           |

|                                                                                                                                          |           |

| Chapter 3: Customizing the Core                                                                                                          |           |

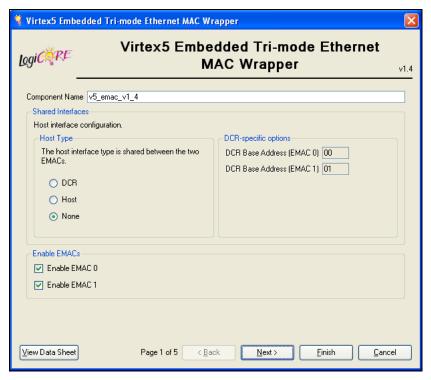

| Ethernet MAC Wrapper Screens                                                                                                             |           |

| Core Configuration Options: Screen 1                                                                                                     | 22        |

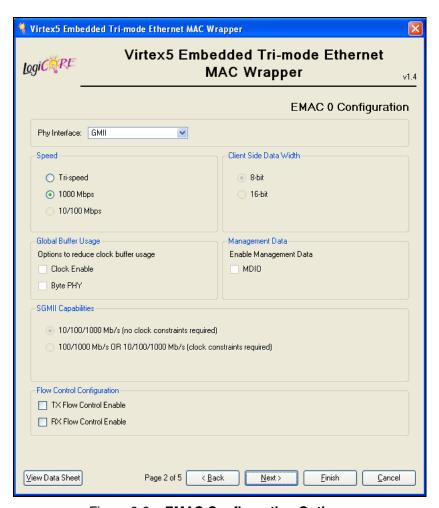

| EMAC Configuration Options: Screen 2                                                                                                     |           |

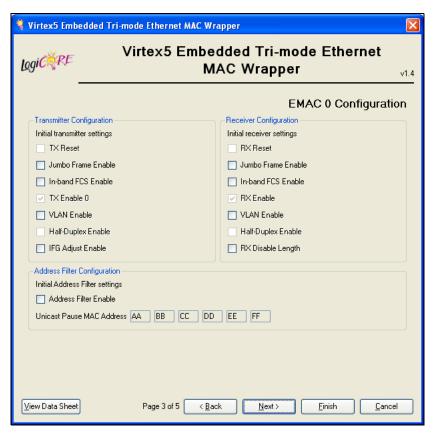

| EMAC Configuration: Screen 3                                                                                                             |           |

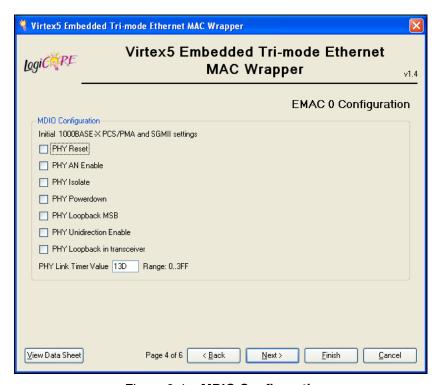

| MDIO/ EMAC Configuration. Screen 4                                                                                                       | <i></i> / |

| Chapter 4: Detailed Example Design                                                                                                       |           |

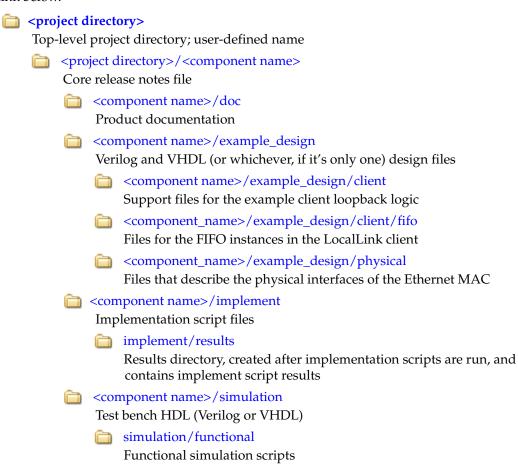

| Directory Structure and File Descriptions                                                                                                | 29        |

| <pre><pre><pre><pre><pre><pre><pre><pre></pre></pre></pre></pre></pre></pre></pre></pre>                                                 |           |

| <pre><pre><pre><pre><pre><pre><pre><pre></pre></pre></pre></pre></pre></pre></pre></pre>                                                 |           |

| <component name="">/doc</component>                                                                                                      |           |

| <pre><component name="">/example_design</component></pre>                                                                                |           |

| <pre><component name="">/example_design/client</component></pre> <pre><component_name>/example_design/client/fifo</component_name></pre> |           |

| <pre><component_name>/example_design/physical</component_name></pre>                                                                     |           |

| <pre><component name="">/implement</component></pre>                                                                                     |           |

| implement/results                                                                                                                        | 34        |

| <pre><component name="">/simulation</component></pre>                                                                                    | 34        |

|     | simulation/functional                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|     | Implementation and Test Scripts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

|     | Setting up for Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                              |

|     | VImplementation Scripts for Timing Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

|     | Test Scripts For Timing Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                              |

|     | Test Scripts For Functional Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                              |

|     | Example Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                              |

|     | HDL Example Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                              |

|     | 10 Mbps, 100 Mbps, 1 Gbps Ethernet FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                              |

|     | Address Swap Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

|     | Physical Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                              |

|     | Demonstration Test Bench                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                              |

|     | Test Bench Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                              |

|     | Changing the Test Bench                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                              |

| ۸nn | andix A. Haing the Client Side FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

| App | endix A: Using the Client Side FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

|     | Overview of LocalLink Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 47                                                                                           |

|     | Receive FIFO Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48                                                                                           |

|     | LocalLink Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

|     | Transmit FIFO Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 49                                                                                           |

|     | LocalLink Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

|     | Clock Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50                                                                                           |

|     | User Interface Data Width Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                              |

|     | Oser Interface Data Width Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 50                                                                                           |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

| App | endix B: Ethernet MAC Clocking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                              |

| App | endix B: Ethernet MAC Clocking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51                                                                                           |

| App | Single-Speed Clocking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |

| App | Single-Speed Clocking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 51                                                                                           |

| App | Single-Speed Clocking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 51<br>53                                                                                     |

| App | Single-Speed Clocking  1000Base-X PCS/PMA: Virtex-5 LXT and SXT Devices.  1000Base-X PCS/PMA: Virtex-5 FXT Devices.  PCS/PMA in Overclocking Mode: Virtex-5 LXT, SXT, and FXT Devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 51<br>53<br>54                                                                               |

| App | Single-Speed Clocking  1000Base-X PCS/PMA: Virtex-5 LXT and SXT Devices  1000Base-X PCS/PMA: Virtex-5 FXT Devices  PCS/PMA in Overclocking Mode: Virtex-5 LXT, SXT, and FXT Devices  GMII/RGMII at 1000 Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 51<br>53<br>54<br>55                                                                         |

| App | Single-Speed Clocking  1000Base-X PCS/PMA: Virtex-5 LXT and SXT Devices  1000Base-X PCS/PMA: Virtex-5 FXT Devices  PCS/PMA in Overclocking Mode: Virtex-5 LXT, SXT, and FXT Devices  GMII/RGMII at 1000 Mbps  Multi-Speed Clocking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 51<br>53<br>54<br>55<br>55                                                                   |

| App | Single-Speed Clocking  1000Base-X PCS/PMA: Virtex-5 LXT and SXT Devices  1000Base-X PCS/PMA: Virtex-5 FXT Devices  PCS/PMA in Overclocking Mode: Virtex-5 LXT, SXT, and FXT Devices  GMII/RGMII at 1000 Mbps  Multi-Speed Clocking  SGMII at Multiple Speeds: Virtex-5 LXT and SXT Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 51<br>53<br>54<br>55<br>55<br>56                                                             |

| App | Single-Speed Clocking  1000Base-X PCS/PMA: Virtex-5 LXT and SXT Devices  1000Base-X PCS/PMA: Virtex-5 FXT Devices  PCS/PMA in Overclocking Mode: Virtex-5 LXT, SXT, and FXT Devices  GMII/RGMII at 1000 Mbps  Multi-Speed Clocking  SGMII at Multiple Speeds: Virtex-5 LXT and SXT Devices  SGMII at Multiple Speeds: Virtex-5 FXT Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 51<br>53<br>54<br>55<br>55<br>56<br>57                                                       |

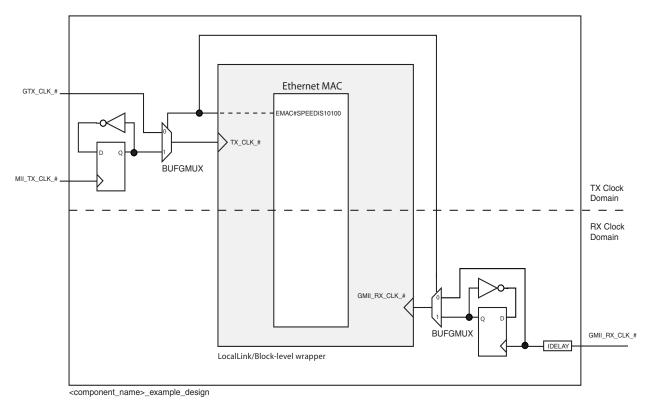

| App | Single-Speed Clocking  1000Base-X PCS/PMA: Virtex-5 LXT and SXT Devices  1000Base-X PCS/PMA: Virtex-5 FXT Devices  PCS/PMA in Overclocking Mode: Virtex-5 LXT, SXT, and FXT Devices  GMII/RGMII at 1000 Mbps  Multi-Speed Clocking  SGMII at Multiple Speeds: Virtex-5 LXT and SXT Devices  SGMII at Multiple Speeds: Virtex-5 FXT Devices  GMII/MII/RGMII at Multiple Speeds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 51<br>53<br>54<br>55<br>55<br>56<br>57<br>58                                                 |

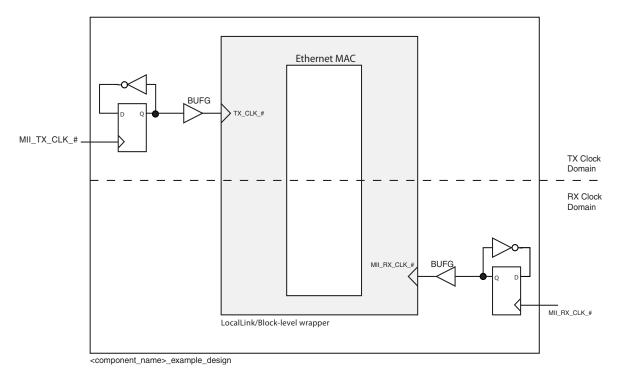

| App | Single-Speed Clocking  1000Base-X PCS/PMA: Virtex-5 LXT and SXT Devices  1000Base-X PCS/PMA: Virtex-5 FXT Devices  PCS/PMA in Overclocking Mode: Virtex-5 LXT, SXT, and FXT Devices  GMII/RGMII at 1000 Mbps  Multi-Speed Clocking  SGMII at Multiple Speeds: Virtex-5 LXT and SXT Devices  SGMII at Multiple Speeds: Virtex-5 FXT Devices  GMII/MII/RGMII at Multiple Speeds  GMII/MII at Multiple Speeds with Clock Enable                                                                                                                                                                                                                                                                                                                                                                                                                                           | 51<br>53<br>54<br>55<br>55<br>56<br>57<br>58<br>60                                           |

| App | Single-Speed Clocking  1000Base-X PCS/PMA: Virtex-5 LXT and SXT Devices  1000Base-X PCS/PMA: Virtex-5 FXT Devices  PCS/PMA in Overclocking Mode: Virtex-5 LXT, SXT, and FXT Devices  GMII/RGMII at 1000 Mbps  Multi-Speed Clocking  SGMII at Multiple Speeds: Virtex-5 LXT and SXT Devices  SGMII at Multiple Speeds: Virtex-5 FXT Devices  GMII/MII/RGMII at Multiple Speeds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 51<br>53<br>54<br>55<br>55<br>56<br>57<br>58<br>60<br>61                                     |

|     | Single-Speed Clocking  1000Base-X PCS/PMA: Virtex-5 LXT and SXT Devices  1000Base-X PCS/PMA: Virtex-5 FXT Devices  PCS/PMA in Overclocking Mode: Virtex-5 LXT, SXT, and FXT Devices  GMII/RGMII at 1000 Mbps  Multi-Speed Clocking  SGMII at Multiple Speeds: Virtex-5 LXT and SXT Devices  SGMII at Multiple Speeds: Virtex-5 FXT Devices  GMII/MII/RGMII at Multiple Speeds  GMII/MII at Multiple Speeds with Clock Enable  RGMII at Multiple Speeds with Clock Enable  GMII/MII at Multiple Speeds with Byte PHY                                                                                                                                                                                                                                                                                                                                                    | 51<br>53<br>54<br>55<br>55<br>56<br>57<br>58<br>60<br>61                                     |

|     | Single-Speed Clocking  1000Base-X PCS/PMA: Virtex-5 LXT and SXT Devices  1000Base-X PCS/PMA: Virtex-5 FXT Devices  PCS/PMA in Overclocking Mode: Virtex-5 LXT, SXT, and FXT Devices  GMII/RGMII at 1000 Mbps  Multi-Speed Clocking  SGMII at Multiple Speeds: Virtex-5 LXT and SXT Devices  SGMII at Multiple Speeds: Virtex-5 FXT Devices  GMII/MII/RGMII at Multiple Speeds  GMII/MII at Multiple Speeds with Clock Enable  RGMII at Multiple Speeds with Clock Enable  GMII/MII at Multiple Speeds with Byte PHY  endix C: Constraining the Example Design                                                                                                                                                                                                                                                                                                          | 51<br>53<br>54<br>55<br>56<br>57<br>58<br>60<br>61<br>61                                     |

|     | Single-Speed Clocking  1000Base-X PCS/PMA: Virtex-5 LXT and SXT Devices.  1000Base-X PCS/PMA: Virtex-5 FXT Devices.  PCS/PMA in Overclocking Mode: Virtex-5 LXT, SXT, and FXT Devices.  GMII/RGMII at 1000 Mbps.  Multi-Speed Clocking.  SGMII at Multiple Speeds: Virtex-5 LXT and SXT Devices.  SGMII at Multiple Speeds: Virtex-5 FXT Devices.  GMII/MII/RGMII at Multiple Speeds.  GMII/MII at Multiple Speeds with Clock Enable.  RGMII at Multiple Speeds with Clock Enable.  GMII/MII at Multiple Speeds with Byte PHY.  endix C: Constraining the Example Design  Block Level Constraints                                                                                                                                                                                                                                                                      | 51<br>53<br>54<br>55<br>56<br>57<br>58<br>60<br>61<br>61                                     |

|     | Single-Speed Clocking  1000Base-X PCS/PMA: Virtex-5 LXT and SXT Devices.  1000Base-X PCS/PMA: Virtex-5 FXT Devices.  PCS/PMA in Overclocking Mode: Virtex-5 LXT, SXT, and FXT Devices.  GMII/RGMII at 1000 Mbps  Multi-Speed Clocking.  SGMII at Multiple Speeds: Virtex-5 LXT and SXT Devices.  SGMII at Multiple Speeds: Virtex-5 FXT Devices.  GMII/MII/RGMII at Multiple Speeds  GMII/MII at Multiple Speeds with Clock Enable.  RGMII at Multiple Speeds with Clock Enable.  GMII/MII at Multiple Speeds with Byte PHY.  Pendix C: Constraining the Example Design  Block Level Constraints  PCS/PMA/SGMII Clock Constraints.                                                                                                                                                                                                                                     | 51<br>53<br>54<br>55<br>56<br>57<br>58<br>60<br>61<br>61                                     |

|     | Single-Speed Clocking  1000Base-X PCS/PMA: Virtex-5 LXT and SXT Devices. 1000Base-X PCS/PMA: Virtex-5 FXT Devices. PCS/PMA in Overclocking Mode: Virtex-5 LXT, SXT, and FXT Devices. GMII/RGMII at 1000 Mbps.  Multi-Speed Clocking. SGMII at Multiple Speeds: Virtex-5 LXT and SXT Devices. SGMII at Multiple Speeds: Virtex-5 FXT Devices. GMII/MII/RGMII at Multiple Speeds. GMII/MII at Multiple Speeds with Clock Enable. RGMII at Multiple Speeds with Clock Enable. GMII/MII at Multiple Speeds with Byte PHY.  endix C: Constraining the Example Design  Block Level Constraints. PCS/PMA/SGMII Clock Constraints. GMII/RGMII 1000 Mbps Clock Constraints                                                                                                                                                                                                      | 51<br>53<br>54<br>55<br>55<br>56<br>57<br>58<br>60<br>61<br>61<br>63<br>63<br>64             |

|     | Single-Speed Clocking  1000Base-X PCS/PMA: Virtex-5 LXT and SXT Devices 1000Base-X PCS/PMA: Virtex-5 FXT Devices PCS/PMA in Overclocking Mode: Virtex-5 LXT, SXT, and FXT Devices GMII/RGMII at 1000 Mbps  Multi-Speed Clocking  SGMII at Multiple Speeds: Virtex-5 LXT and SXT Devices SGMII at Multiple Speeds: Virtex-5 FXT Devices GMII/MII/RGMII at Multiple Speeds GMII/MII at Multiple Speeds with Clock Enable RGMII at Multiple Speeds with Clock Enable GMII/MII at Multiple Speeds with Byte PHY  Pendix C: Constraining the Example Design  Block Level Constraints PCS/PMA/SGMII Clock Constraints GMII/RGMII 1000 Mbps Clock Constraints GMII/RGMII 1000 Mbps Clock Constraints                                                                                                                                                                          | 51<br>53<br>54<br>55<br>56<br>57<br>58<br>60<br>61<br>61<br>63<br>64<br>65                   |

|     | Single-Speed Clocking  1000Base-X PCS/PMA: Virtex-5 LXT and SXT Devices  1000Base-X PCS/PMA: Virtex-5 FXT Devices  PCS/PMA in Overclocking Mode: Virtex-5 LXT, SXT, and FXT Devices  GMII/RGMII at 1000 Mbps  Multi-Speed Clocking  SGMII at Multiple Speeds: Virtex-5 LXT and SXT Devices  SGMII at Multiple Speeds: Virtex-5 FXT Devices  GMII/MII/RGMII at Multiple Speeds  GMII/MII at Multiple Speeds with Clock Enable  RGMII at Multiple Speeds with Clock Enable  GMII/MII at Multiple Speeds with Byte PHY  Pendix C: Constraining the Example Design  Block Level Constraints  PCS/PMA/SGMII Clock Constraints  GMII/RGMII 1000 Mbps Clock Constraints  GMII/RGMII 1000 Mbps Clock Constraints  GMII/MII/RGMII 10/100/1000 Mbps Clock Constraints  GMII/MII/RGMII 10/100/1000 Mbps Clock Constraints  GMII/MII/RGMII 10/100/1000 Mbps Clock Constraints      | 51<br>53<br>54<br>55<br>55<br>56<br>57<br>58<br>60<br>61<br>61<br>63<br>64<br>65<br>66       |

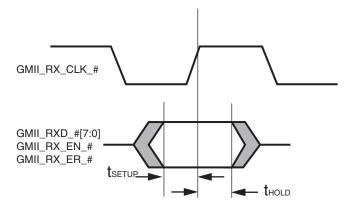

|     | Single-Speed Clocking  1000Base-X PCS/PMA: Virtex-5 LXT and SXT Devices.  1000Base-X PCS/PMA: Virtex-5 FXT Devices.  PCS/PMA in Overclocking Mode: Virtex-5 LXT, SXT, and FXT Devices.  GMII/RGMII at 1000 Mbps  Multi-Speed Clocking.  SGMII at Multiple Speeds: Virtex-5 LXT and SXT Devices.  SGMII at Multiple Speeds: Virtex-5 FXT Devices.  GMII/MII/RGMII at Multiple Speeds.  GMII/MII at Multiple Speeds with Clock Enable.  RGMII at Multiple Speeds with Clock Enable.  RGMII/MII at Multiple Speeds with Byte PHY.  Pendix C: Constraining the Example Design  Block Level Constraints.  PCS/PMA/SGMII Clock Constraints.  GMII/RGMII 1000 Mbps Clock Constraints.  GMII/RGMII 100100/1000 Mbps Clock Constraints.  GMII/MII/RGMII 10/100/1000 Mbps Clock Constraints.  GMII/MII/RGMII 10/LOC/1000 Mbps Clock Constraints.  GMII IDELAY_VALUE Constraints. | 51<br>53<br>54<br>55<br>56<br>57<br>58<br>60<br>61<br>61<br>63<br>63<br>64<br>65<br>66       |

|     | Single-Speed Clocking  1000Base-X PCS/PMA: Virtex-5 LXT and SXT Devices  1000Base-X PCS/PMA: Virtex-5 FXT Devices  PCS/PMA in Overclocking Mode: Virtex-5 LXT, SXT, and FXT Devices  GMII/RGMII at 1000 Mbps  Multi-Speed Clocking  SGMII at Multiple Speeds: Virtex-5 LXT and SXT Devices  SGMII at Multiple Speeds: Virtex-5 FXT Devices  GMII/MII/RGMII at Multiple Speeds  GMII/MII at Multiple Speeds with Clock Enable  RGMII at Multiple Speeds with Clock Enable  GMII/MII at Multiple Speeds with Byte PHY  Pendix C: Constraining the Example Design  Block Level Constraints  PCS/PMA/SGMII Clock Constraints  GMII/RGMII 1000 Mbps Clock Constraints  GMII/RGMII 1000 Mbps Clock Constraints  GMII/MII/RGMII 10/100/1000 Mbps Clock Constraints  GMII/MII/RGMII 10/100/1000 Mbps Clock Constraints  GMII/MII/RGMII 10/100/1000 Mbps Clock Constraints      | 51<br>53<br>54<br>55<br>56<br>57<br>58<br>60<br>61<br>61<br>63<br>64<br>65<br>66<br>67<br>68 |

| GMII/MII Interface                             | 69 |

|------------------------------------------------|----|

| RGMII v2.0 Interface                           |    |

| Example Placement                              | 69 |

| GMII/RGMII IODELAY Controller Clock Constraint | 70 |

| Host Interface Clock Constraint                | 70 |

| DCR Interface Clock Constraint                 | 70 |

| Appendix D: SGMII Receiver Elastic Buffer      |    |

| SGMII Capabilities                             | 71 |

| FPGA Fabric Rx Elastic Buffer Requirement      | 71 |

| The RocketIO Rx Elastic Buffer                 | 73 |

| Jumbo Frame Reception                          | 74 |

# Schedule of Figures

| Chap             | ter 2: Quick Start Example Design                                            |    |

|------------------|------------------------------------------------------------------------------|----|

|                  | Figure 2-1: Default Example Design and Test Bench                            | 16 |

|                  | Figure 2-2: Virtex-5 Embedded Tri-Mode Ethernet MAC Wrapper Main Screen      | 17 |

| Cha              | ter 3: Customizing the Core                                                  |    |

|                  | Figure 3-1: Core Configuration Options                                       | 22 |

|                  | Figure 3-2: EMAC Configuration Options                                       |    |

|                  | Figure 3-3: EMAC Configuration Options                                       | 25 |

|                  | Figure 3-4: MDIO Configuration                                               |    |

| Cha <sub>l</sub> | ter 4: Detailed Example Design                                               |    |

|                  | Figure 4-1: HDL Example Design                                               | 39 |

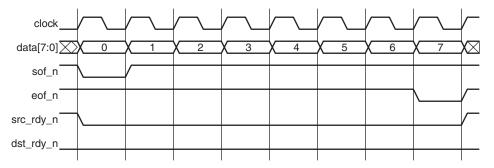

|                  | Figure 4-2: Frame Transfer across LocalLink Interface                        | 40 |

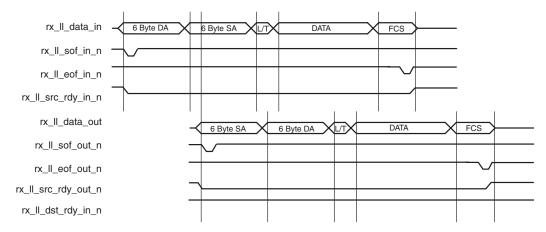

|                  | Figure 4-3: Modification of Frame Data by Address Swap Module                | 42 |

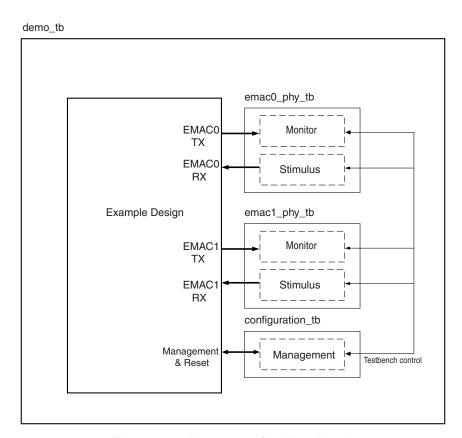

|                  | Figure 4-4: Demonstration Test Bench                                         | 43 |

| App              | endix A: Using the Client Side FIFO                                          |    |

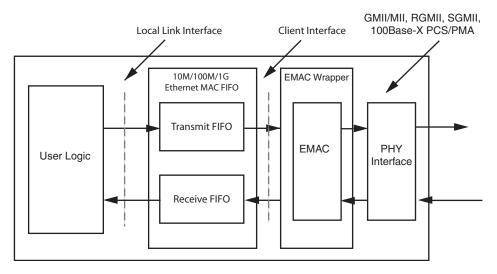

|                  | Figure A-1: Typical 10M/100M/1G Ethernet FIFO Implementation                 | 47 |

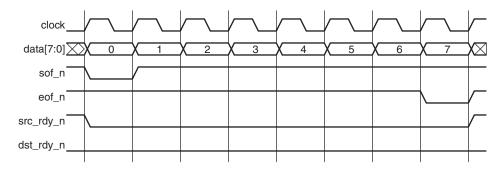

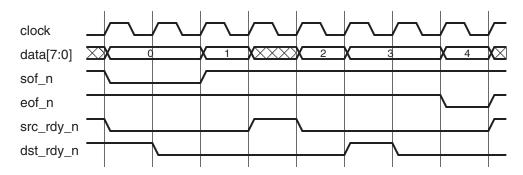

|                  | Figure A-2: Frame Transfer across LocalLink Interface                        | 48 |

|                  | Figure A-3: Frame Transfer with Flow Control                                 | 48 |

| App              | endix B: Ethernet MAC Clocking                                               |    |

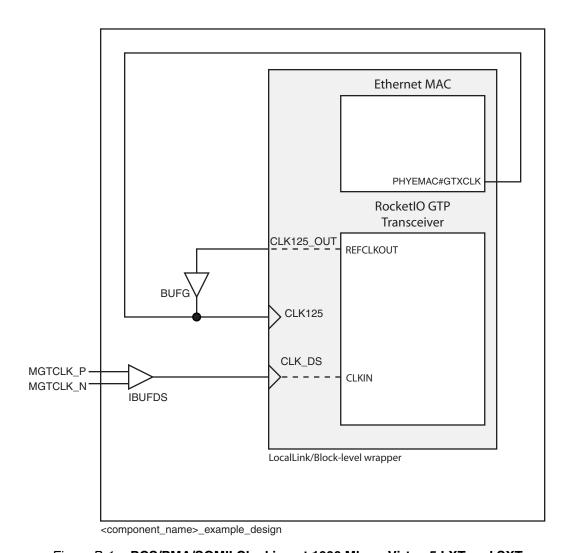

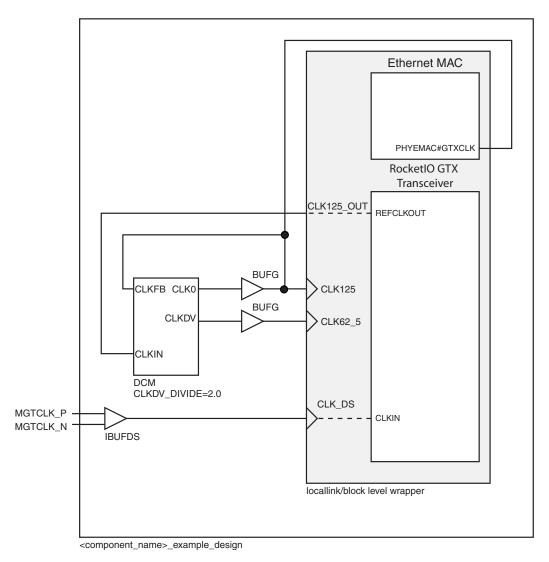

|                  | Figure B-1: PCS/PMA/SGMII Clocking at 1000 Mbps: Virtex-5 LXT and SXT        | 52 |

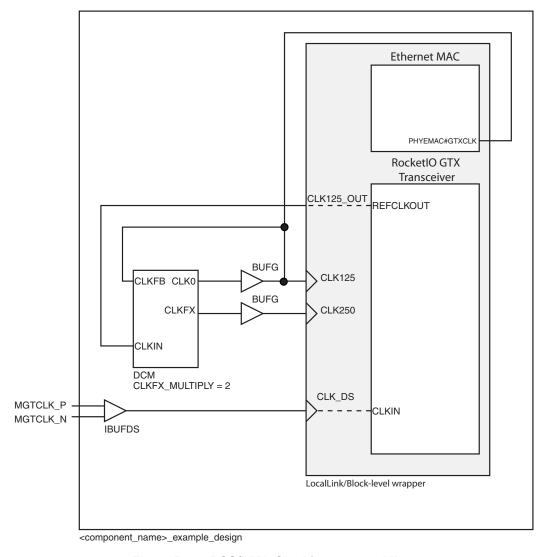

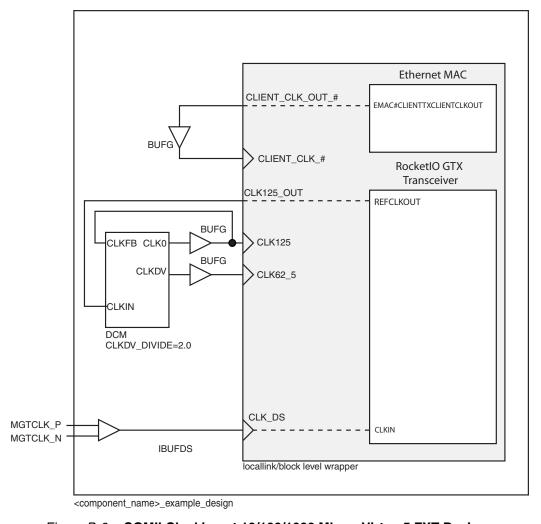

|                  | Figure B-2: PCS/PMA/SGMII Clocking at 1000 Mbps: Virtex-5 FXT Devices        | 53 |

|                  | Figure B-3: PCS/PMA Clocking at 2000 Mbps                                    | 54 |

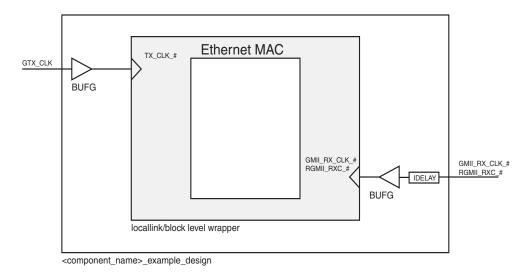

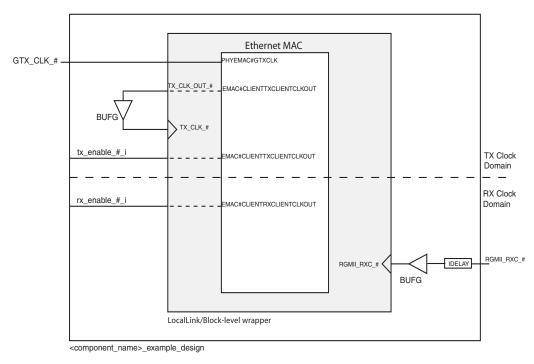

|                  | Figure B-4: GMII/RGMII Clocking at 1000 Mbps                                 | 55 |

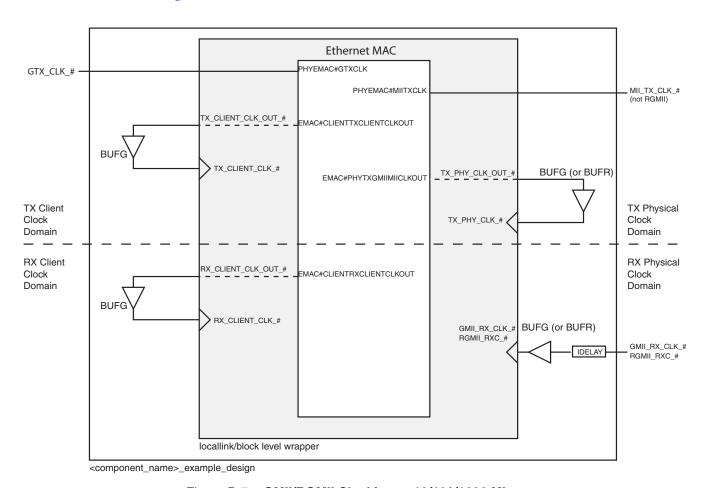

|                  | Figure B-5: SGMII Clocking at 10/100/1000 Mbps: Virtex-5 LXT and SXT Devices | 56 |

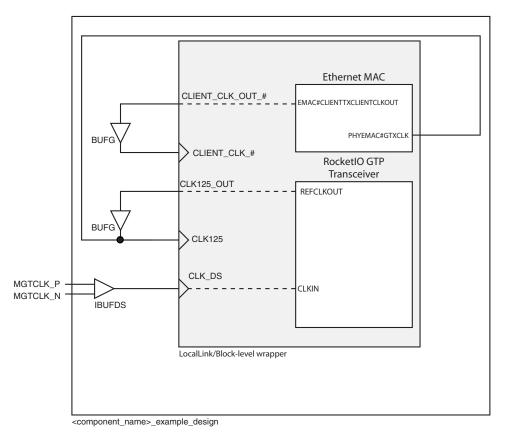

|                  | Figure B-6: SGMII Clocking at 10/100/1000 Mbps: Virtex-5 FXT Devices         | 57 |

|                  | Figure B-7: GMII/RGMII Clocking at 10/100/1000 Mbps                          | 58 |

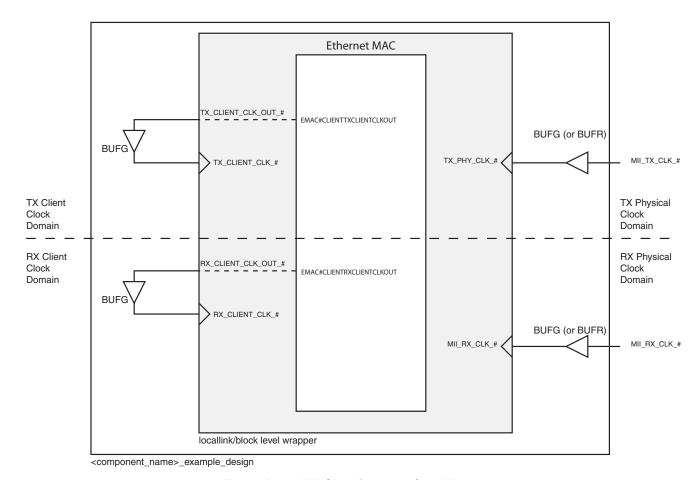

|                  | Figure B-8: MII Clocking at 10/100 Mbps                                      | 59 |

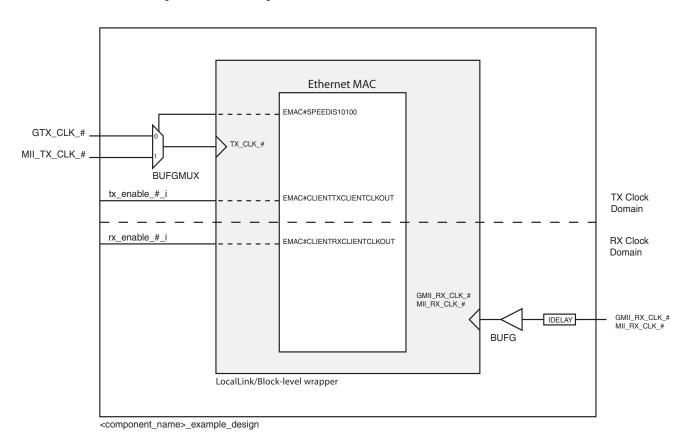

|                  | Figure B-9: GMII/MII Clocking at 10/100/1000 Mbps with Clock Enables         | 60 |

|                  | Figure B-10: RGMII Clocking at 10/100/1000 Mbps with Clock Enable            | 61 |

|                  | Figure B-11: GMII Clocking at 10/100/1000 Mbps with Byte PHY                 | 62 |

|                  | Figure B-12: MII Clocking at 10/100 Mbps with Byte PHY                       | 62 |

| Appendix C: Constraining the Example Design              |    |

|----------------------------------------------------------|----|

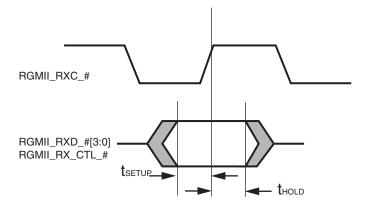

| Figure C-1: Input GMII Timing                            | 66 |

| Figure C-2: RGMII Input Timing                           | 67 |

| Appendix D: SGMII Receiver Elastic Buffer                |    |

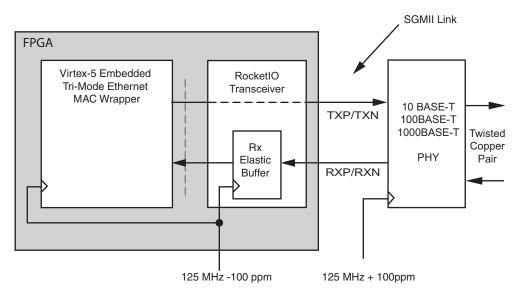

| Figure D-1: SGMII Implementation: Separate Clock Sources | 72 |

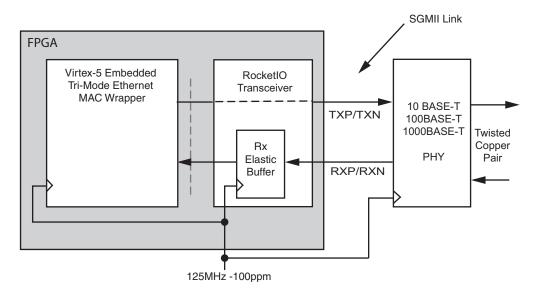

| Figure D-2: SGMII Implementation: Shared Clock Sources   | 73 |

# About This Guide

The Virtex-5<sup>TM</sup> FPGA Embedded Tri-Mode Ethernet MAC Wrapper Getting Started Guide provides information about generating an embedded Tri-Mode Ethernet MAC for Virtex-5 FPGA devices, customizing and simulating the wrapper files utilizing the provided example design, and running the design files through implementation using the Xilinx tools.

## **Contents**

This guide contains the following chapters:

- Preface, "About this Guide" introduces the organization and purpose of this guide and the conventions used in this guide.

- Chapter 1, "Introduction" describes the Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC wrapper and related information, including recommended design experience, additional resources, technical support, and submitting feedback to Xilinx.

- Chapter 2, "Quick Start Example Design," describes how to quickly generate the example design using the CORE Generator™ Graphical User Interface (GUI) software.

- Chapter 3, "Customizing the Core," describes the CORE Generator software customization options.

- Chapter 4, "Detailed Example Design," provides detailed information about the example design and demonstration test bench.

- Appendix A, "Using the Client Side FIFO," describes the operation of the example design client side FIFO.

- Appendix B, "Ethernet MAC Clocking," describes the provided clocking scheme for each interface.

- Appendix C, "Constraining the Example Design," describes the timing and placement constraints included with the example design.

- Appendix D, "SGMII Receiver Elastic Buffer," defines the SGMII capabilities for the core.

Preface: About This Guide

# **Conventions**

This document uses the following conventions. An example illustrates each convention.

# Typographical

The following typographical conventions are used in this document:

| Convention                      | Meaning or Use                                                                                               | Example                                                                                            |

|---------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Courier font                    | Messages, prompts, and program files that the system displays                                                | speed grade: - 100                                                                                 |

| Courier bold                    | Literal commands that you enter in a syntactical statement                                                   | ngdbuild design_name                                                                               |

| Italia fout                     | References to other manuals                                                                                  | See the <i>Development System Reference Guide</i> for more information.                            |

| Italic font                     | Emphasis in text                                                                                             | If a wire is drawn so that it overlaps the pin of a symbol, the two nets are <i>not</i> connected. |

| <text brackets="" in=""></text> | User-defined variable for directory names.                                                                   | <component_name></component_name>                                                                  |

| Square brackets []              | An optional entry or parameter. However, in bus specifications, such as <b>bus[7:0]</b> , they are required. | ngdbuild [option_name] design_name                                                                 |

|                                 | Also used with pipe symbol to indicate either one or the other.                                              | client_loopback_[8   16].v                                                                         |

| Braces { }                      | A list of items from which you must choose one or more                                                       | lowpwr ={on off}                                                                                   |

| Vertical bar                    | Separates items in a list of choices                                                                         | lowpwr ={on off}                                                                                   |

| Vertical ellipsis               | Repetitive material that has been omitted                                                                    | IOB #1: Name = QOUT' IOB #2: Name = CLKIN'                                                         |

| Horizontal ellipsis             | Repetitive material that has been omitted                                                                    | allow block block_name loc1 loc2 locn;                                                             |

# **Online Document**

The following conventions are used in this document:

| Convention            | Meaning or Use                                             | Example                                                                                                    |

|-----------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Blue text             | Cross-reference link to a location in the current document | See the section "Additional<br>Resources" for details.<br>See "Title Formats" in Chapter 1<br>for details. |

| Blue, underlined text | Hyperlink to a website (URL)                               | Go to <a href="http://www.xilinx.com">http://www.xilinx.com</a> for the latest speed files.                |

# Introduction

This chapter introduces the Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC (Ethernet MAC) wrapper and provides related information, including recommended design experience, additional resources, technical support, and submitting feedback to Xilinx. The Ethernet MAC wrapper supports Verilog HDL and VHDL.

# **System Requirements**

#### **Windows**

- Windows XP® Professional 32-bit/64-bit

- Windows Vista® Business 32-bit/64-bit

#### Linux

- Red Hat® Enterprise WS 4.0 32-bit/64-bit

- Red Hat Enterprise Desktop 5.0 32-bit/64-bit (with Workstation option)

- SUSE Linux Enterprise (SLE) v10.1 32-bit/64-bit

#### Software

• ISETM 10.1

# **About the Ethernet MAC Wrapper Core**

The Ethernet MAC wrapper is included in the latest IP Update on the Xilinx IP Center. For detailed information about the core, visit the Ethernet MAC wrapper product page. The Ethernet MAC wrapper is provided to all licensed Xilinx ISE customers free of charge and is generated using the Xilinx CORE Generator v10.1 or higher.

# **Designs Using RocketIO Transceivers**

RocketIO transceivers are defined by device family in the following way:

- For Virtex-5 LXT and SXT devices, RocketIO GTP transceivers

- For Virtex-5 FXT devices, RocketIO GTX transceivers

Throughout this guide, the term *RocketIO transceiver* is used to represent any or all of the RocketIO transceivers; select the RocketIO transceiver specific to the desired target device.

# **Recommended Design Experience**

Although the Ethernet MAC wrapper is fully verified, the challenge associated with implementing a complete design varies depending on the configuration and functionality of the application. For best results, previous experience building high performance, pipelined FPGA designs using Xilinx implementation software and user constraint files (UCF) is recommended. Contact your local Xilinx representative for a closer review and estimation for your specific requirements.

# **Additional Resources**

For additional details and updates, see the *Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC User Guide*, available from

www.xilinx.com/support/documentation/virtex-5\_user\_guides.htm.

# **Technical Support**

The fastest method for obtaining specific technical support for the Ethernet MAC wrapper is through the <a href="www.xilinx.com/support">www.xilinx.com/support</a> website. Questions are routed to a technical support team with specific expertise using the Ethernet MAC wrapper.

Xilinx provides technical support for use of this product as described in the *Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC Data Sheet, Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC Getting Started Guide,* and the *Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC User Guide.* Xilinx does not guarantee timing, functionality, or support of this product for designs that do not follow these guidelines.

## **Feedback**

Xilinx welcomes comments and suggestions about the Ethernet MAC wrapper and the supplied documentation.

# Ethernet MAC Wrapper

For comments or suggestions about the Ethernet MAC wrapper, please submit a webcase from <a href="https://www.xilinx.com/support">www.xilinx.com/support</a>. Be sure to include the following information:

- Product name

- Version number

- Explanation of your comments

#### **Document**

For comments or suggestions about this document, please submit a webcase from <a href="https://www.xilinx.com/support">www.xilinx.com/support</a>. Be sure to include the following information:

- Document title

- Document number

- Page number(s) to which your comments refer

- Explanation of your comments

# Quick Start Example Design

This chapter provides instructions for generating the Ethernet MAC wrapper using the CORE Generator GUI.

# **Overview**

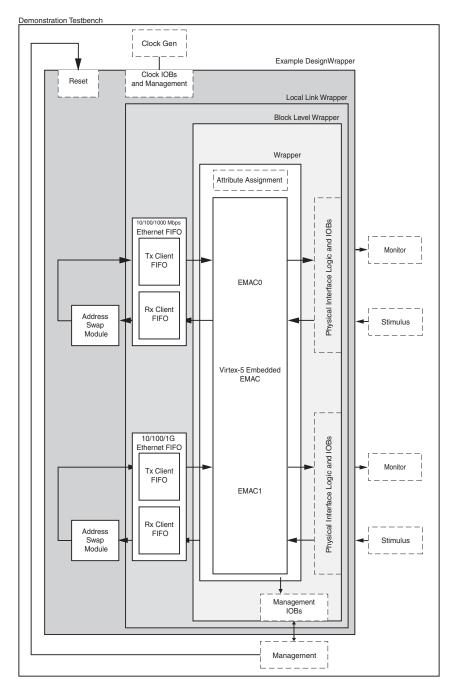

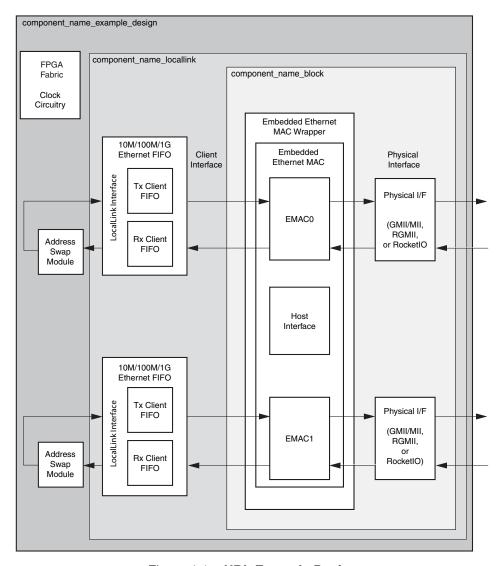

The Ethernet MAC wrapper consists of the following:

- A wrapper file that assigns the attributes of each Ethernet MAC to the values selected in the Core Generator GUI. In addition, unused inputs are tied low and unused outputs are disconnected.

- An example design with a three-level hierarchy:

- The block-level wrapper instantiates the Ethernet MAC wrapper and the interface logic for each of the selected physical interfaces.

- The LocalLink wrapper connects the transmit and receive client interfaces of each selected Ethernet MAC to a LocalLink FIFO.

- The example design wrapper connects the FIFOs so that data received at the client looped back to the transmitter. A small address-swap module is also instantiated to swap the source and destination addresses of the incoming frame. Clock management logic including DCMs and Global Clock Buffer instances, where required, is also included.

- A demonstration test bench to exercise the wrappers and the example design. This injects frames into the physical interface receiver of each selected Ethernet MAC and monitors the data that is output at the transmitter.

Figure 2-1 displays the example design and test bench provided with the Ethernet MAC wrapper. The example design has been tested with Xilinx ISE 10.1, Cadence® IUS v6.1, Mentor Graphics® ModelSim® 6.3c, and Synopsys® VCS 2006.06-SP1.

Figure 2-1: Default Example Design and Test Bench

# Generating the Ethernet MAC Wrapper

To generate the Ethernet MAC wrapper and example design, do the following:

- 1. Start the CORE Generator.

- For help starting and using the CORE Generator tool, the *CORE Generator Guide* at <a href="http://www.xilinx.com/support/software">http://www.xilinx.com/support/software</a> manuals.htm.

- 2. Choose File > New Project.

- 3. Set the following project options:

- From Target Architecture, select Virtex-5.

**Note**: If an unsupported silicon family or part is selected, the Ethernet MAC wrapper is not displayed in the taxonomy tree.

- For Design Entry, select either VHDL or Verilog; for Vendor, select Other.

- 4. After creating the project, locate the directory containing the Ethernet MAC wrapper in the taxonomy tree. The project appears under one of the following:

- Communications & Networking / Ethernet

- Communications & Networking / Networking

- Communications & Networking/Telecommunications

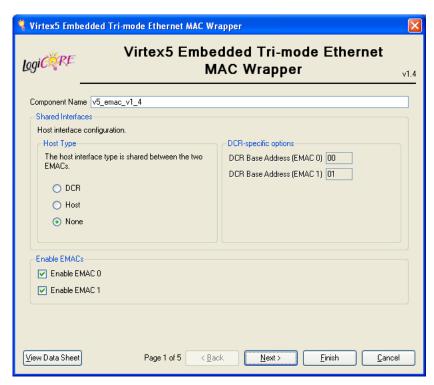

- 5. Double-click Virtex-5 Embedded Tri-Mode Ethernet MAC Wrapper. The initial customization screen appears.

Figure 2-2: Virtex-5 Embedded Tri-Mode Ethernet MAC Wrapper Main Screen

6. In the Component Name field, enter a name for the core instance, and then click Finish to generate the example design using the default values.

The wrapper and its supporting files, including the example design, are generated in your project directory. For a detailed description of the design example files and directories, see Chapter 4, "Detailed Example Design."

A functional simulation directory is created that contains scripts to simulate the example design using the structural hdl models. For more information see "Functional Simulation," page 18.

# Implementing the Example Design

The HDL example design can be processed using the Xilinx implementation toolset. The generated output files include several scripts to assist the user in running the Xilinx software.

Open a command prompt or shell in your project directory, then enter the following commands:

#### For Linux

```

% cd <component_name>/implement

% ./implement.sh

```

#### For Windows

```

ms-dos> cd <component_name>\implement

ms-dos> implement.bat

```

These commands execute a script that synthesizes, builds, maps, and place-and-routes the example design. The resulting files are placed in the results directory.

These commands start a script that synthesizes the HDL example design and builds the design. The script also maps and place-and-routes the example design. It then creates gate-level netlist HDL files in both VHDL and Verilog, along with associated timing information (SDF) files.

# **Running the Simulation**

#### **Functional Simulation**

To run the functional simulation you must have the Xilinx Simulation Libraries compiled for your system. For more information, see *Compiling Xilinx Simulation Libraries* (*COMPXLIB*) in the *Xilinx ISE Synthesis and Verification Design Guide*, which can be obtained from <a href="https://www.xilinx.com/support/software\_manuals.htm">www.xilinx.com/support/software\_manuals.htm</a>. In addition, use the following guidelines to determine the simulator required for your design:

#### Virtex-5 Devices

Virtex-5 device designs require either a Verilog LRM-IEEE 1364-2005 encryption-compliant simulator or a SWIFT-compliant simulator.

- For a Verilog LRM-IEEE 1364-2005 encryption-compliant simulator, ModelSim v6.3c is currently supported.

- For a SWIFT-compliant simulator, Cadence IUS v6.1 and Synopsys VCS 2006.06-SP1 are currently supported.

#### VHDL Simulation

#### To run a VHDL functional simulation:

- Launch the simulator and set the current directory to

<project\_dir>/<component\_name>/simulation/functional

- For ModelSim map the UNISIM library:

```

ModelSim> vmap unisim <path to compiled libraries>/unisim

```

• Launch the simulation script:

```

ModelSim> do simulate_mti.do

IUS> ./simulate ncsim.sh

```

The scripts compile the example design files and the demonstration test bench, add some relevant signals to a wave window, then run the simulation to completion. At this point, you can review the simulation transcript and waveform to observe the operation of the Ethernet MACs.

#### Verilog Simulation

#### To run a Verilog functional simulation:

- Launch the simulator and set the current directory to

<project\_dir>/<component\_name>/simulation/functional

- For ModelSim map the UNISIM library:

```

ModelSim> vmap unisims_ver <path to compiled libraries>/unisims_ver

```

Launch the simulation script:

```

ModelSim> do simulate_mti.do

IUS> ./simulate ncsim.sh

```

The scripts compile the example design files and the demonstration test bench, add some relevant signals to a wave window, then run the simulation to completion. At this point, you can review the simulation transcript and waveform to observe the operation of the Ethernet MACs.

# **Timing Simulation**

To run the gate-level simulation you must have the Xilinx Simulation Libraries compiled for your system. For more information, see *Compiling Xilinx Simulation Libraries* (*COMPXLIB*) in the *Xilinx ISE Synthesis and Verification Design Guide*, which can be obtained from <a href="http://www.xilinx.com/support/software\_manuals.htm">http://www.xilinx.com/support/software\_manuals.htm</a>.

In the simulation examples that follow, for directory; <component\_name</pre> is the component name as entered in the core customization dialog box.

#### VHDL Simulation

#### To run a VHDL timing simulation:

- Launch the simulator and set the current directory to

<project\_dir>/<component\_name>/simulation/timing

- For ModelSim map the SIMPRIM library:

```

ModelSim> vmap simprim <path to compiled libraries>/simprim

```

• Launch the simulation script:

```

ModelSim> do simulate_mti.do

IUS> ./simulate ncsim.sh

```

The scripts compile the gate-level model and the demonstration test bench, add some relevant signals to a wave window, then run the simulation to completion. At this point, you can review the simulation transcript and waveform to observe the operation of the Ethernet MACs.

#### **Verilog Simulation**

#### To run a Verilog timing simulation:

- For ModelSim map the SIMPRIM library:

```

ModelSim> vmap simprims_ver <path to

compiled_libraries>/simprims_ver

```

• Launch the simulation script:

```