# **ISE In-Depth Tutorial**

10.1

Xilinx is disclosing this Document and Intellectual Property (hereinafter "the Design") to you for use in the development of designs to operate on, or interface with Xilinx FPGAs. Except as stated herein, none of the Design may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Any unauthorized use of the Design may violate copyright laws, trademark laws, the laws of privacy and publicity, and communications regulations and statutes.

Xilinx does not assume any liability arising out of the application or use of the Design; nor does Xilinx convey any license under its patents, copyrights, or any rights of others. You are responsible for obtaining any rights you may require for your use or implementation of the Design. Xilinx reserves the right to make changes, at any time, to the Design as deemed desirable in the sole discretion of Xilinx. Xilinx assumes no obligation to correct any errors contained herein or to advise you of any correction if such be made. Xilinx will not assume any liability for the accuracy or correctness of any engineering or technical support or assistance provided to you in connection with the Design.

THE DESIGN IS PROVIDED "AS IS" WITH ALL FAULTS, AND THE ENTIRE RISK AS TO ITS FUNCTION AND IMPLEMENTATION IS WITH YOU. YOU ACKNOWLEDGE AND AGREE THAT YOU HAVE NOT RELIED ON ANY ORAL OR WRITTEN INFORMATION OR ADVICE, WHETHER GIVEN BY XILINX, OR ITS AGENTS OR EMPLOYEES. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DESIGN, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND NONINFRINGEMENT OF THIRD-PARTY RIGHTS.

IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOST DATA AND LOST PROFITS, ARISING FROM OR RELATING TO YOUR USE OF THE DESIGN, EVEN IF YOU HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. THE TOTAL CUMULATIVE LIABILITY OF XILINX IN CONNECTION WITH YOUR USE OF THE DESIGN, WHETHER IN CONTRACT OR TORT OR OTHERWISE, WILL IN NO EVENT EXCEED THE AMOUNT OF FEES PAID BY YOU TO XILINX HEREUNDER FOR USE OF THE DESIGN. YOU ACKNOWLEDGE THAT THE FEES, IF ANY, REFLECT THE ALLOCATION OF RISK SET FORTH IN THIS AGREEMENT AND THAT XILINX WOULD NOT MAKE AVAILABLE THE DESIGN TO YOU WITHOUT THESE LIMITATIONS OF LIABILITY.

The Design is not designed or intended for use in the development of on-line control equipment in hazardous environments requiring fail-safe controls, such as in the operation of nuclear facilities, aircraft navigation or communications systems, air traffic control, life support, or weapons systems ("High-Risk Applications"). Xilinx specifically disclaims any express or implied warranties of fitness for such High-Risk Applications. You represent that use of the Design in such High-Risk Applications is fully at your risk.

Copyright © 1995-2007 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. PowerPC is a trademark of IBM, Inc. All other trademarks are the property of their respective owners.

# **About This Tutorial**

# **About the In-Depth Tutorial**

This tutorial gives a description of the features and additions to Xilinx<sup>®</sup> ISE<sup>TM</sup> 10.1. The primary focus of this tutorial is to show the relationship among the design entry tools, Xilinx and third-party tools, and the design implementation tools.

This guide is a learning tool for designers who are unfamiliar with the features of the ISE software or those wanting to refresh their skills and knowledge.

You may choose to follow one of the three tutorial flows available in this document. For information about the tutorial flows, see "Tutorial Flows."

# **Tutorial Contents**

This guide covers the following topics.

- Chapter 1, "Overview of ISE and Synthesis Tools," introduces you to the ISE primary user interface, Project Navigator, and the synthesis tools available for your design.

- **Chapter 2**, "HDL-Based Design," guides you through a typical HDL-based design procedure using a design of a runner's stopwatch.

- Chapter 3, "Schematic-Based Design," explains many different facets of a schematic-based ISE design flow using a design of a runner's stopwatch. This chapter also shows how to use ISE accessories such as StateCAD, CORE Generator™, and ISE Text Editor.

- **Chapter 4**, "Behavioral Simulation," explains how to simulate a design before design implementation to verify that the logic that you have created is correct.

- Chapter 5, "Design Implementation," describes how to Translate, Map, Place, Route (Fit for CPLDs), and generate a Bit file for designs.

- Chapter 6, "Timing Simulation," explains how to perform a timing simulation using the block and routing delay information from the routed design to give an accurate assessment of the behavior of the circuit under worst-case conditions.

- **Chapter 7**, "iMPACT Tutorial" explains how to program a device with a newly created design using the IMPACT configuration tool.

# **Tutorial Flows**

This document contains three tutorial flows. In this section, the three tutorial flows are outlined and briefly described, in order to help you determine which sequence of chapters applies to your needs. The tutorial flows include:

- HDL Design Flow

- Schematic Design Flow

- Implementation-only Flow

# **HDL Design Flow**

The HDL Design flow is as follows:

- Chapter 2, "HDL-Based Design"

- Chapter 4, "Behavioral Simulation"

Note that although behavioral simulation is optional, it is strongly recommended in this tutorial flow.

- Chapter 5, "Design Implementation"

- Chapter 6, "Timing Simulation"

Note that although timing simulation is optional, it is strongly recommended in this tutorial flow.

- Chapter 7, "iMPACT Tutorial"

# Schematic Design Flow

The Schematic Design flow is as follows:

- Chapter 3, "Schematic-Based Design"

- Chapter 4, "Behavioral Simulation"

Note that although behavioral simulation is optional, it is strongly recommended in this tutorial flow.

- Chapter 5, "Design Implementation"

- Chapter 6, "Timing Simulation"

Note that although timing simulation is optional, it is strongly recommended.

- Chapter 7, "iMPACT Tutorial"

# Implementation-only Flow

The Implementation-only flow is as follows:

- Chapter 5, "Design Implementation"

- Chapter 6, "Timing Simulation"

Note that although timing simulation is optional, it is strongly recommended in this tutorial flow.

- Chapter 7, "iMPACT Tutorial"

# **Additional Resources**

To find additional documentation, see the Xilinx website at:

http://www.xilinx.com/literature.

To search the Answer Database of silicon, software, and IP questions and answers, or to create a technical support WebCase, see the Xilinx website at:

http://www.xilinx.com/support.

# **Table of Contents**

| Preface: About This Tutor    | ial                   |

|------------------------------|-----------------------|

| About the In-Depth Tutorial  | 3                     |

| <del>-</del>                 | 3                     |

|                              |                       |

|                              |                       |

| O                            |                       |

| · ·                          |                       |

| •                            | 4                     |

| Additional Resources         | 5                     |

| Chapter 1: Overview of ISI   | E and Synthesis Tools |

| -                            | _ d                   |

|                              |                       |

|                              |                       |

|                              |                       |

|                              |                       |

| <u> </u>                     |                       |

|                              |                       |

|                              |                       |

| Transcript Window            |                       |

| <u>-</u>                     | ce                    |

| Error Navigation to Ansv     | ver Record            |

| Workspace                    |                       |

| Design Summary               |                       |

| Text Editor                  |                       |

|                              | m Editor              |

|                              |                       |

| Using Revision Control Featu | ures 17               |

| Using Snapshots              |                       |

| Creating a Snapshot          |                       |

|                              |                       |

| _ ·                          |                       |

|                              |                       |

|                              |                       |

|                              |                       |

|                              | e Control             |

| 1 0                          |                       |

| 1 0 0                        |                       |

|                              |                       |

|                              |                       |

| •                            |                       |

|                              |                       |

|                              |                       |

|                              | / (XST)               |

| Dragons Drangetics           | 20                    |

## Chapter 2: HDL-Based Design Chapter 3: Schematic-Based Design

|         | Creating a New Project: Using a Tcl Script                    |    |

|---------|---------------------------------------------------------------|----|

|         | topping the Tutorial                                          |    |

|         | gn Description                                                |    |

|         | nputs                                                         |    |

|         | Outputs                                                       |    |

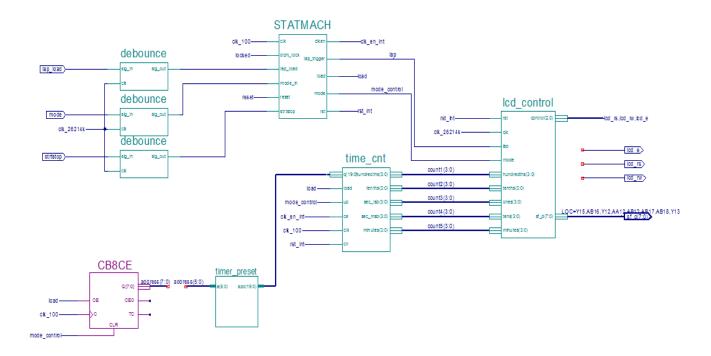

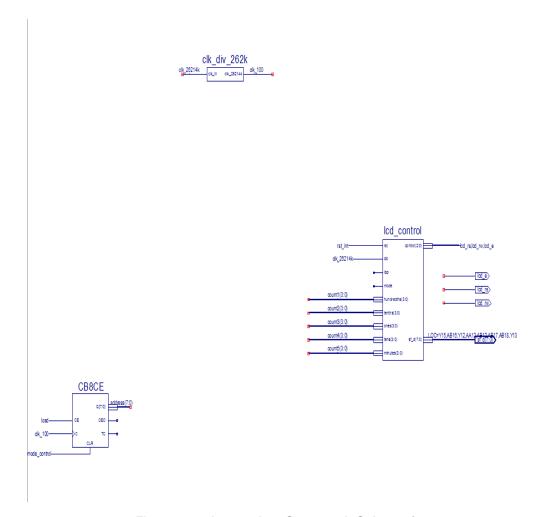

| F       | Functional Blocks                                             | 54 |

| Desig   | gn Entry                                                      | 55 |

|         | Opening the Schematic File in the Xilinx Schematic Editor     |    |

|         | Manipulating the Window View                                  |    |

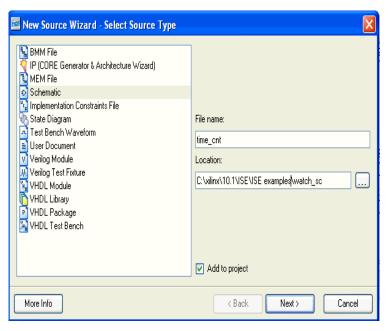

|         | Creating a Schematic-Based Macro                              |    |

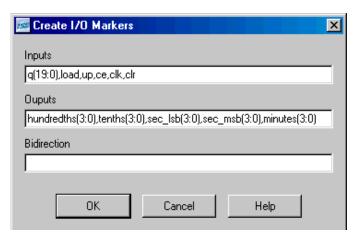

|         | Defining the time_cnt Schematic                               |    |

|         | Adding I/O Markers                                            |    |

|         | Adding Schematic Components                                   |    |

|         | Correcting Mistakes                                           |    |

|         | Drawing Wires                                                 |    |

|         | Adding Buses                                                  |    |

|         | Adding Bus Taps                                               |    |

|         | Adding Net Names.                                             |    |

|         | Checking the Schematic                                        |    |

|         | Saving the Schematic                                          |    |

| (       | Creating and Placing the time_cnt Symbol                      |    |

|         | Creating the time_cnt symbol                                  |    |

|         | Placing the time_cnt Symbol                                   |    |

| (       | Creating a CORE Generator Module                              | 66 |

|         | Creating a CORE Generator Module                              |    |

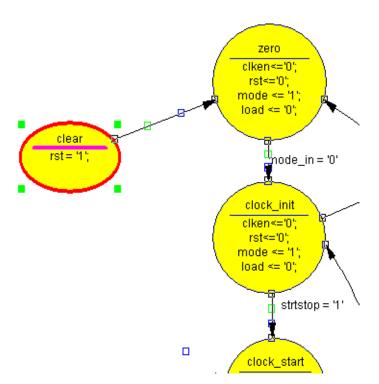

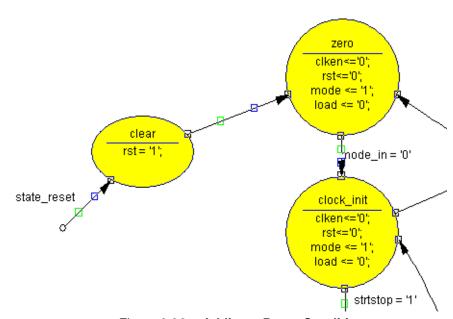

| (       | Creating a State Machine Module                               |    |

| •       | Adding New States                                             |    |

|         | Adding a Transition                                           |    |

|         | Adding a State Action.                                        |    |

|         | Adding a State Machine Reset Condition                        |    |

|         | Creating the State Machine HDL output file.                   |    |

| (       | Creating the State Machine Symbol                             |    |

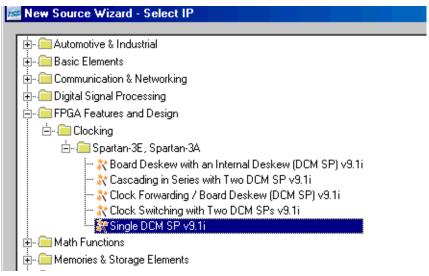

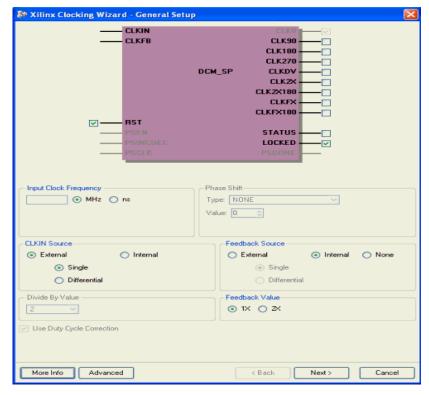

|         | Creating a DCM Module                                         |    |

| •       | Using the Clocking Wizard                                     |    |

| (       | Creating the dcm1 Symbol                                      |    |

|         | Creating an HDL-Based Module                                  |    |

| •       | Using the New Source Wizard and ISE Text Editor               |    |

|         | Using the Language Templates.                                 |    |

|         | Adding a Language Templates.                                  |    |

| (       | Creating the debounce Symbol                                  |    |

|         | Placing the statmach, timer_preset, dcm1 and debounce Symbols |    |

|         |                                                               |    |

|         | Changing Instance Names                                       |    |

|         | Hierarchy Push/Pop                                            |    |

| 3       | Specifying Device Inputs/Outputs                              |    |

|         | Adding Input Pins                                             |    |

| ,       | Adding I/O Markers and Net Names                              |    |

|         | Assigning Pin Locations                                       |    |

| (       | ompleung the schematic                                        | oJ |

| ıpter 4 | 4: Behavioral Simulation                                      |    |

| Over    | view of Behavioral Simulation Flow                            | 89 |

|         | elSim Setup                                                   |    |

| 141000  | ·19111 Oup                                                    | J  |

| ModelSim PE and SE                                           |

|--------------------------------------------------------------|

| ModelSim Xilinx Edition                                      |

| ISE Simulator Setup. 90                                      |

| Getting Started                                              |

| Design Files (VHDL, Verilog, or Schematic)                   |

| Test Bench File                                              |

| Xilinx Simulation Libraries                                  |

| Xilinx Simulation Libraries                                  |

| Updating the Xilinx Simulation Libraries                     |

| Mapping Simulation Libraries in the Modelsim.ini File        |

| Adding an HDL Test Bench 92                                  |

| Adding Tutorial Test Bench File                              |

| VHDL Simulation                                              |

| Verilog Simulation                                           |

| Behavioral Simulation Using ModelSim93                       |

| Locating the Simulation Processes                            |

| Specifying Simulation Properties                             |

| Performing Simulation 95 Adding Signals 95                   |

| Adding Dividers                                              |

| Rerunning Simulation                                         |

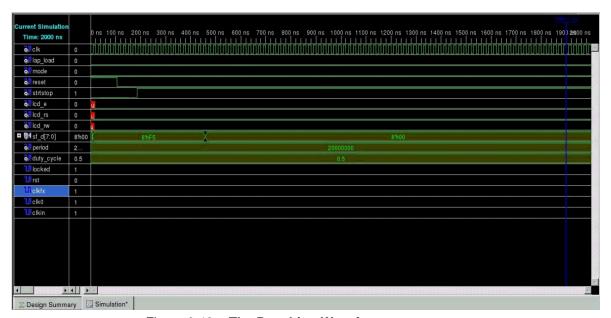

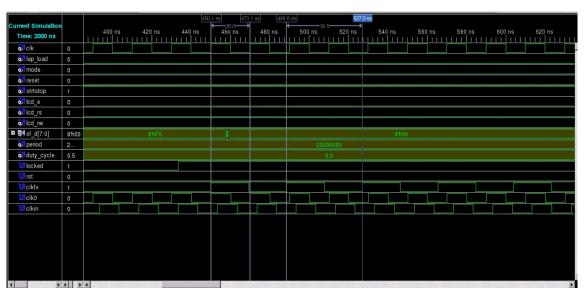

| Analyzing the Signals                                        |

| Saving the Simulation                                        |

| Behavioral Simulation Using ISE Simulator 99                 |

| Locating the Simulation Processes 99                         |

| Specifying Simulation Properties                             |

| Performing Simulation                                        |

| Adding Signals                                               |

| Rerunning Simulation                                         |

| Analyzing the Signals                                        |

| Creating a Test Bench Waveform Source                        |

| Applying Stimulus                                            |

|                                                              |

| Chapter 5: Design Implementation                             |

| Overview of Design Implementation                            |

| Getting Started                                              |

| Continuing from Design Entry                                 |

| Starting from Design Implementation 108                      |

| Specifying Options 109                                       |

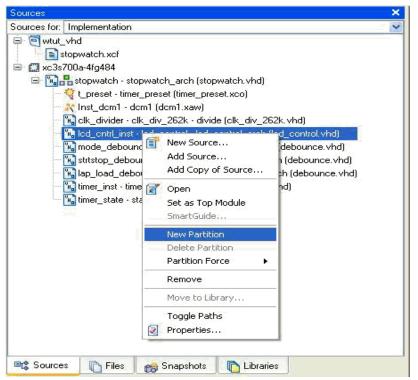

| Creating Partitions                                          |

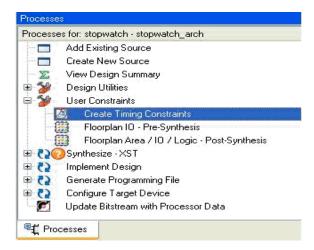

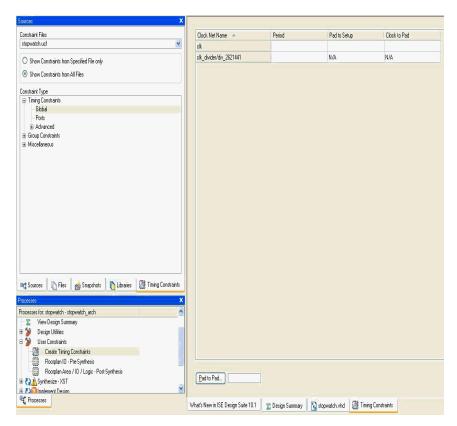

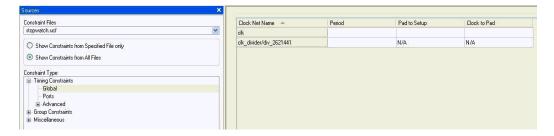

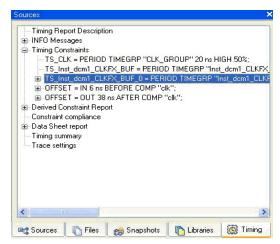

| Creating Timing Constraints                                  |

| Translating the Design                                       |

| Using the Constraints Editor 114                             |

| Using the Floorplan Editor                                   |

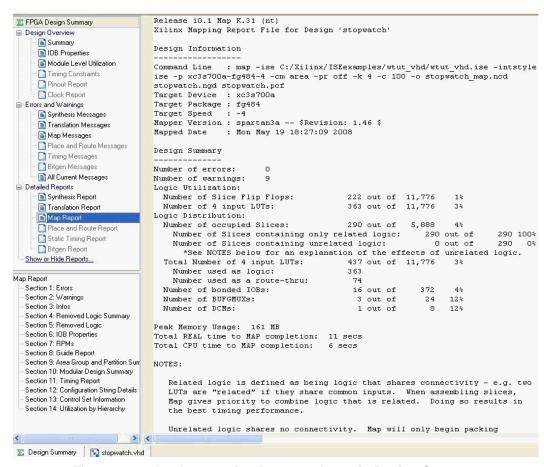

| Mapping the Design                                           |

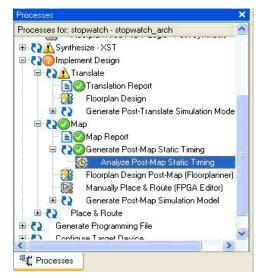

| Using Timing Analysis to Evaluate Block Delays After Mapping |

| Estimating Timing Goals with the 50/50 Rule                  |

| Report Paths in Timing Constraints Option       | 124 |

|-------------------------------------------------|-----|

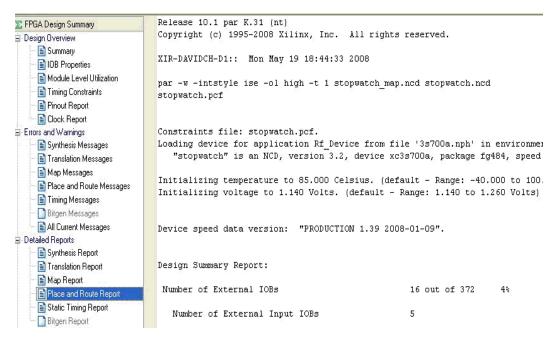

| Placing and Routing the Design                  | 126 |

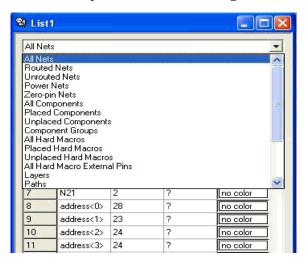

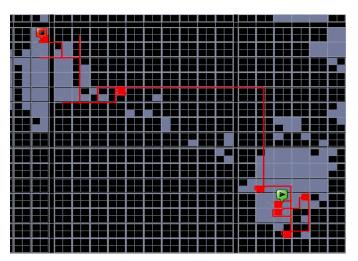

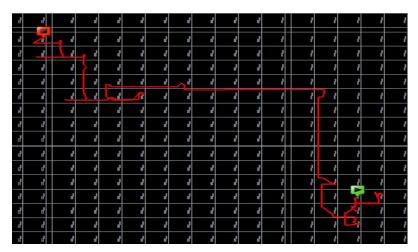

| Using FPGA Editor to Verify the Place and Route | 127 |

| Evaluating Post-Layout Timing                   | 129 |

| Changing HDL with Partition                     |     |

| Creating Configuration Data                     |     |

| 8 8                                             |     |

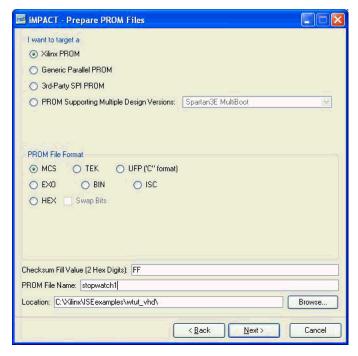

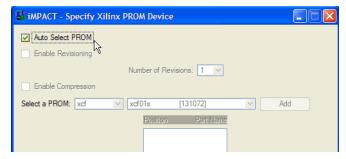

| Creating a PROM File with iMPACT                |     |

| Command Line Implementation                     | 136 |

| Objection Co. Timing Observation                |     |

| Chapter 6: Timing Simulation                    |     |

| Overview of Timing Simulation Flow              | 137 |

| Getting Started                                 | 137 |

| Required Software                               |     |

| Required Files                                  |     |

| Specifying a Simulator                          |     |

| Timing Simulation Using ModelSim                |     |

| Specifying Simulation Process Properties        |     |

| Performing Simulation                           |     |

| Adding Signals                                  |     |

| Adding Dividers                                 |     |

| Rerunning Simulation                            |     |

| Saving the Simulation                           |     |

| Timing Simulation Using Xilinx ISE Simulator    |     |

| Specifying Simulation Process Properties        |     |

| Performing Simulation                           |     |

| Adding Signals                                  |     |

| Viewing Full Signal Names                       |     |

| Rerunning Simulation                            |     |

| Analyzing the Signals                           | 150 |

|                                                 |     |

| Chapter 7: iMPACT Tutorial                      |     |

| Device Support                                  | 153 |

| Download Cable Support                          |     |

| Parallel Cable IV                               |     |

| Platform Cable USB                              | 154 |

| MultiPRO Cable                                  | 154 |

| Configuration Mode Support                      | 154 |

| Getting Started                                 | 154 |

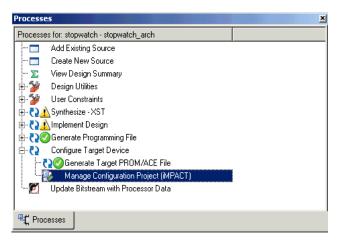

| Generating the Configuration Files              |     |

| Connecting the Cable                            |     |

| Starting the Software                           |     |

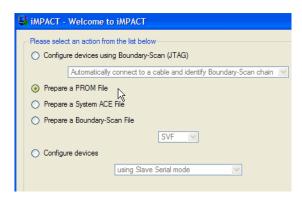

| Opening iMPACT from Project Navigator           |     |

| Opening iMPACT stand-alone                      |     |

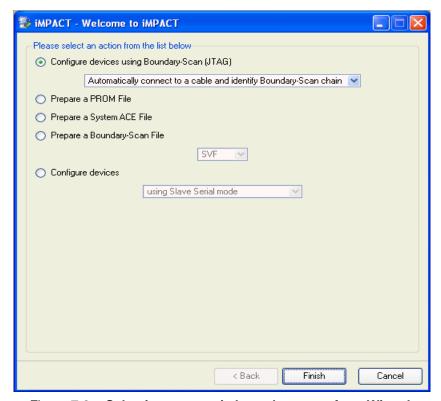

| Creating a iMPACT New Project File              |     |

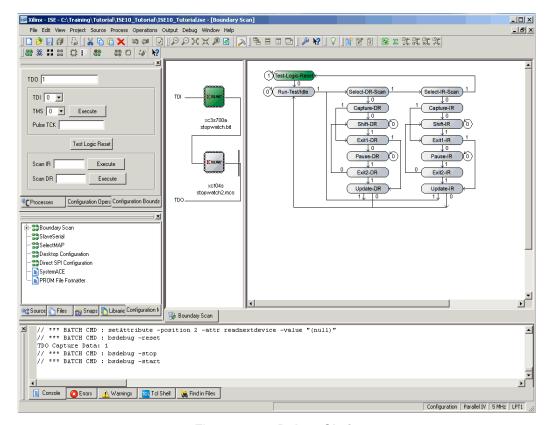

| Using Boundary Scan Configuration Mode          |     |

| Specifying Boundary Scan Configuration Mode     |     |

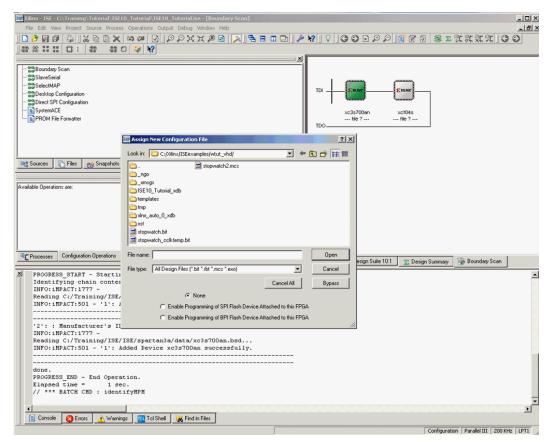

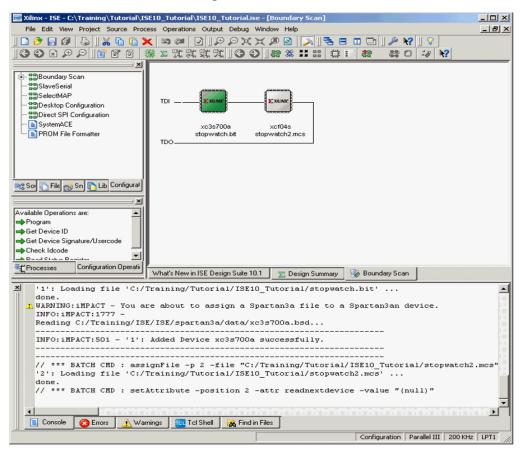

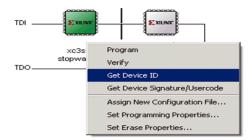

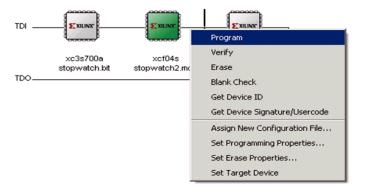

| Assigning Configuration Files                   | 158 |

| Saving the Project File                       | 159 |

|-----------------------------------------------|-----|

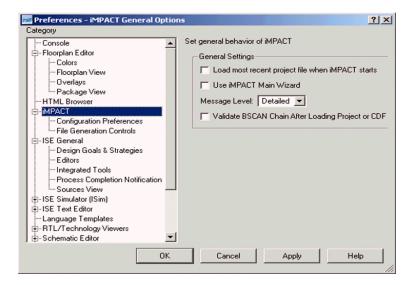

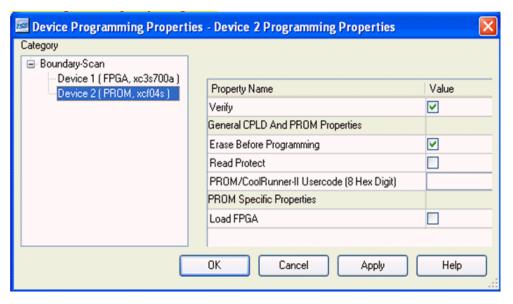

| Editing Preferences                           |     |

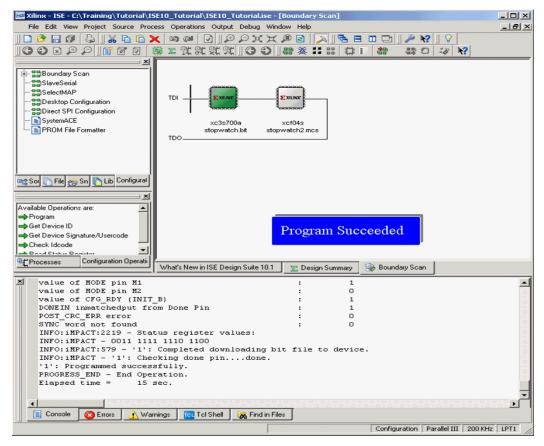

| Performing Boundary Scan Operations           |     |

| Troubleshooting Boundary Scan Configuration 1 | 162 |

| Verifying Cable Connection                    |     |

| Verifying Chain Setup                         | 163 |

| Creating an SVF File                          | 64  |

| Setting up Boundary Scan Chain                | 64  |

| JTAG chain setup for SVF generation           | 164 |

| Manual JTAG chain setup for SVF generation    | 164 |

| Writing to the SVF File 1                     | 165 |

| Stop Writing to the SVF                       |     |

| Playing back the SVF or XSVF file             | 166 |

| Other Configuration Modes                     | 166 |

| Slave Serial Configuration Mode               | 166 |

| SelectMAP Configuration Mode                  | 167 |

# Overview of ISE and Synthesis Tools

This chapter includes the following sections:

- "Overview of ISE"

- "Using Revision Control Features"

- "Overview of Synthesis Tools"

### Overview of ISE

ISE controls all aspects of the design flow. Through the Project Navigator interface, you can access all of the design entry and design implementation tools. You can also access the files and documents associated with your project.

# **Project Navigator Interface**

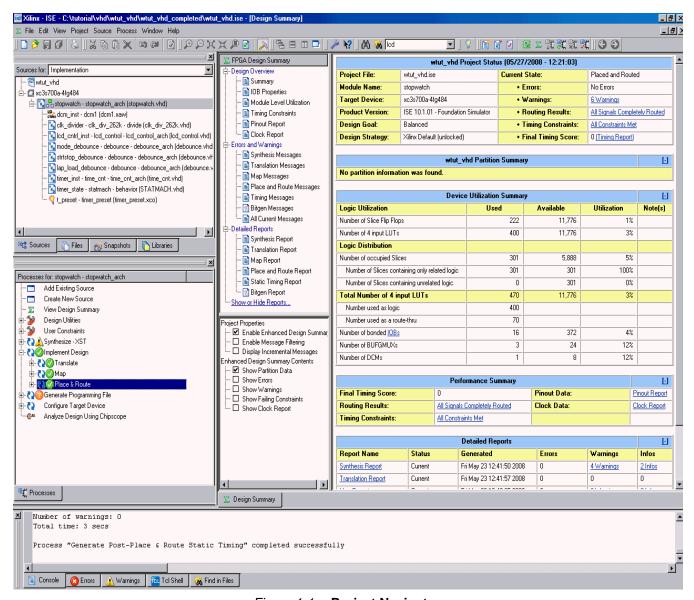

The Project Navigator Interface is divided into four main subwindows, as seen in Figure 1-1. On the top left is the Sources window which hierarchically displays the elements included in the project. Beneath the Sources window is the Processes window, which displays available processes for the currently selected source. The third window at the bottom of the Project Navigator is the Transcript window which displays status messages, errors, and warnings and also contains interactive tabs for Tcl scripting and the Find in Files function. The fourth window to the right is a multi-document interface (MDI) window referred to as the *Workspace*. It enables you to view html reports, ASCII text files, schematics, and simulation waveforms. Each window may be resized, undocked from Project Navigator or moved to a new location within the main Project Navigator window. The default layout can always be restored by selecting **View > Restore Default Layout**. These windows are discussed in more detail in the following sections.

Figure 1-1: Project Navigator

#### Sources Window

This window consists of three tabs which provide project and file information for the user. Each tab is discussed in further detail below.

#### Sources Tab

The Sources tab displays the project name, the specified device, and user documents and design source files associated with the selected Design View. The Design View ("Sources for") drop-down list at the top of the Sources tab allows you to view only those source files associated with the selected Design View, such as Synthesis/Implementation. In the "Number of" drop-down list, a Resources column and a Preserve Column are available for Designs that use Partitions. The use of partitions is covered in Chapter 5, "Design Implementation".

Each file in a Design View has an associated icon. The icon indicates the file type (HDL file, schematic, core, or text file, for example). For a complete list of possible source types and their associated icons, see the ISE<sup>TM</sup> Help. Select **Help > ISE Help Contents**, select the Index tab and search for "Source file types."

If a file contains lower levels of hierarchy, the icon has a + to the left of the name. HDL files have this + to show the entities (VHDL) or modules (Verilog) within the file. You can expand the hierarchy by clicking the +. You can open a file for editing by double-clicking on the filename.

#### **Snapshots Tab**

The Snapshots tab displays all snapshots associated with the project currently open in Project Navigator. A snapshot is a copy of the project including all files in the working directory, and synthesis and simulation sub-directories. A snapshot is stored with the project for which it was taken, and the snapshot can be viewed in the Snapshots tab. You can view the reports, user documents, and source files for all snapshots. All information displayed in the Snapshots tab is read-only. Using snapshots provides an excellent version control system, enabling subteams to do simultaneous development on the same design.

#### Libraries Tab

The Libraries tab displays all libraries associated with the project open in Project Navigator.

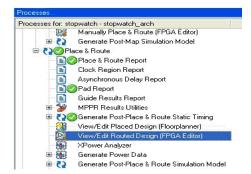

#### **Processes Window**

This window contains one default tab called the Processes tab.

#### **Processes Tab**

The Processes tab is context sensitive and it changes based upon the source type selected in the Sources tab and the Top-Level Source in your project. From the Processes tab, you can run the functions necessary to define, run and view your design. The Processes tab provides access to the following functions:

- Add an Existing Source

- Create New Source

- View Design Summary

- Design Utilities

Provides access to symbol generation, instantiation templates, viewing command line history, and simulation library compilation.

#### • User Constraints

Provides access to editing location and timing constraints.

#### Synthesis

Provides access to Check Syntax, Synthesis, View RTL or Technology Schematic, and synthesis reports. Available processes vary depending on the synthesis tools you use.

#### Implement Design

Provides access to implementation tools, design flow reports, and point tools.

#### Generate Programming File

Provides access to configuration tools and bitstream generation.

The Processes tab incorporates automake technology. This enables the user to select any process in the flow and the software automatically runs the processes necessary to get to the desired step. For example, when you run the Implement Design process, Project Navigator also runs the Synthesis process because implementation is dependent on up-to-date synthesis results.

**Note:** To view a running log of command line arguments used on the current project, expand Design Utilities and select **View Command Line Log File**. See the Command Line Implementation section of Chapter 5, "Design Implementation" for further details.

# **Transcript Window**

The Transcript window contains five default tabs: Console, Errors, Warnings, Tcl Shell, Find in Files.

#### Console

Displays errors, warnings, and information messages. Errors are signified by a red (X) next to the message, while warnings have a yellow exclamation mark (!).

#### Warnings

Displays only warning messages. Other console messages are filtered out.

#### Errors

Displays only error messages. Other console messages are filtered out.

#### Tcl Shell

Is a user interactive console. In addition to displaying errors, warnings and informational messages, the Tcl Shell allows a user to enter Project Navigator specific Tcl commands. For more information on Tcl commands, see the ISE Help.

#### • Find in Files

Displays the results of the **Edit > Find in Files** function.

#### Error Navigation to Source

You can navigate from a synthesis error or warning message in the Transcript window to the location of the error in a source HDL file. To do so, select the error or warning message, right-click the mouse, and select **Go to Source** from the right-click menu. The HDL source file opens and the cursor moves to the line with the error.

#### Error Navigation to Answer Record

You can navigate from an error or warning message in the Transcript window to relevant Answer Records on the <a href="https://www.xilinx.com/support">www.xilinx.com/support</a> website. To navigate to the Answer Record(s), select the error or warning message, right-click the mouse, and select **Go to Answer Record** from the right-click menu. The default web browser opens and displays all Answer Records applicable to this message.

# Workspace

#### **Design Summary**

The Design Summary lists high-level information about your project, including overview information, a device utilization summary, performance data gathered from the Place & Route (PAR) report, constraints information, and summary information from all reports with links to the individual reports.

#### Text Editor

Source files and other text documents can be opened in a user designated editor. The editor is determined by the setting found by selecting **Edit > Preferences**, expand ISE General and click **Editors.** The default editor is the ISE Text Editor. ISE Text Editor enables you to edit source files and user documents. You can access the Language Templates, which is a catalog of ABEL, Verilog, VHDL, Tcl and User Constraints File templates that you can use and modify in your own design.

#### ISE Simulator / Waveform Editor

ISE Simulator / Waveform Editor can be used to create and simulate test bench and test fixture within the Project Navigator framework. Waveform Editor can be used to graphically enter stimuli and the expected response, then generate a VHDL test bench or Verilog test fixture. For details, refer to "Creating a Test Bench Waveform Using the Waveform Editor" in Chapter 4.

#### Schematic Editor

The Schematic Editor is integrated in the Project Navigator framework. The Schematic Editor can be used to graphically create and view logical designs.

# **Using Revision Control Features**

# **Using Snapshots**

Snapshots enable you to maintain revision control over the design. A snapshot contains a copy of all of the files in the project directory. See also "Snapshots Tab."

# Creating a Snapshot

To create a snapshot:

- 1. Select Project > Take Snapshot.

- 2. In the Take a Snapshot of the Project dialog box, enter the snapshot name and any comments associated with the snapshot.

The snapshot containing all of the files in the project directory along with project settings is displayed in the Snapshots tab.

# Restoring a Snapshot

Since snapshots are read-only, a snapshot must be restored in order to continue work. When you restore a snapshot, it replaces the project in your current session.

To restore a snapshot:

- 1. In the Snapshots tab, select the snapshot from the drop-down list.

- 2. Select Project > Make Snapshot Current.

Before the snapshot replaces the current project, you are given the option to place the current project in a snapshot so that your work is not lost.

**Note:** Remote sources are copied with the snapshot and placed in a subdirectory named remote\_sources. These files will need to be manually copied to the original location or added to the project again in a new directory

#### Viewing a Snapshot

The Snapshots tab contains a list of all the snapshots available in the current project. To review a process report or verify process status within a snapshot:

- 1. Expand the snapshot source tree and select the desired source file.

- 2. Right-click the mouse over the desired process report.

- 3. From the menu, select **Open Without Updating**.

# **Using Project Archives**

You can also archive the entire project into a single compressed file. This allows for easier transfer over email and storage of numerous projects in a limited space.

# Creating an Archive

To create an archive:

- 1. Select Project > Archive.

- 2. In the Create Zip Archive dialog box, enter the archive name and location.

**Note:** The archive contains all of the files in the project directory along with project settings. Remote sources are included in the archive under a folder named remote\_sources. For more information, see the ISE Help.

# Restoring an Archive

You cannot restore an archived file directly into Project Navigator. The compressed file can be extracted with any ZIP utility and you can then open the extracted file in Project Navigator.

# Using Export/Import Source Control

You can use this feature to export to and retrieve project files and sources from a "staging area." The Export/Import processes are typically used in conjunction with a 3rd party source control system but can be used independently as a valid means of backing up a design.

# Exporting a Project

To export a project

1. Select Project > Source Control > Export

2. Follow the Export Project Wizard to determine which files to export, where to export the files to, and optionally create a Tcl script that can be used to regenerate the ISE project.

#### Importing a Project

To import a project

- 1. Select Project > Source Control > Import

- 2. Select the Project File (.ise or Tcl import script) and directory location to import the project file and sources.

# **Overview of Synthesis Tools**

You can synthesize your design using various synthesis tools. The following section lists the supported synthesis tools and includes some process properties information.

# **Precision Synthesis**

This synthesis tool is not part of the ISE package and is not available unless purchased separately. Two commonly used properties are Optimization Goal and Optimization Effort. With these properties you can control the synthesis results for area or speed and the amount of time the synthesizer runs. This synthesis tool is available for both an HDL- and Schematic-based design flow.

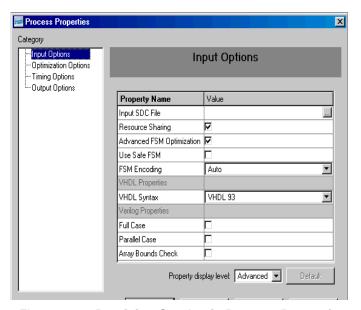

#### **Process Properties**

Process properties enable you to control the synthesis results of Precision. Most of the commonly used synthesis options available for the Precision stand-alone version are available for Precision synthesis through ISE.

For more information, see the Precision online help.

Figure 1-2: Precision Synthesis Process Properties

# Synplify/Synplify Pro

This synthesis tool is not part of the ISE package and is not available unless purchased separately. This synthesis tool is available for HDL-based designs, but it is not available for a schematic-based design.

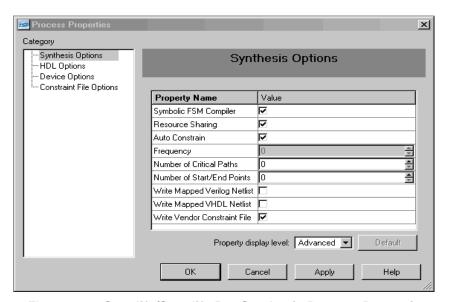

#### **Process Properties**

Process properties enable you to control the synthesis results of Synplify/Synplify Pro. Most of the commonly used synthesis options available in the Synplify/Synplify Pro stand-alone version are available for Synplify/Synplify Pro synthesis through ISE.

For more information, see the Synplify/Synplify Pro online help.

Figure 1-3: Synplify/Synplify Pro Synthesis Process Properties

# Xilinx Synthesis Technology (XST)

This synthesis tool is part of the ISE package and is available for both an HDL- and Schematic-based design flow.

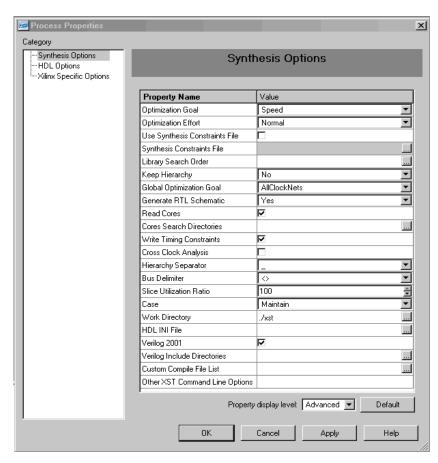

#### **Process Properties**

Process properties enable you to control the synthesis results of XST. Two commonly used properties are Optimization Goal and Optimization Effort. With these properties you can control the synthesis results for area or speed, and the amount of time the synthesizer runs.

More detailed information is available in the *XST User Guide*, available in the collection of software manuals. From ISE, select **Help > Software Manuals**, or go on the web at <a href="http://www.xilinx.com/support/software\_manuals.htm">http://www.xilinx.com/support/software\_manuals.htm</a>.

Figure 1-4: XST Synthesis Process Properties

# HDL-Based Design

This chapter includes the following sections:

- "Overview of HDL-Based Design"

- "Getting Started"

- "Design Description"

- "Design Entry"

- "Synthesizing the Design"

# **Overview of HDL-Based Design**

This chapter guides you through a typical HDL-based design procedure using a design of a runner's stopwatch. The design example used in this tutorial demonstrates many device features, software features, and design flow practices you can apply to your own design. This design targets a Spartan $^{\text{TM}}$ -3A device; however, all of the principles and flows taught are applicable to any Xilinx $^{\text{®}}$  device family, unless otherwise noted.

The design is composed of HDL elements and two cores. You can synthesize the design using Xilinx Synthesis Technology (XST), Synplify/Synplify Pro, or Precision.

This chapter is the first chapter in the "HDL Design Flow." After the design is successfully defined, you will perform behavioral simulation (Chapter 4, "Behavioral Simulation"), run implementation with the Xilinx Implementation Tools (Chapter 5, "Design Implementation"), perform timing simulation (Chapter 6, "Timing Simulation"), and configure and download to the Spartan-3A demo board (Chapter 7, "iMPACT Tutorial").

# **Getting Started**

The following sections describe the basic requirements for running the tutorial.

# **Required Software**

To perform this tutorial, you must have the following software and software components installed:

- Xilinx Series ISE<sup>TM</sup> 10.1i

- Spartan-3A libraries and device files

**Note:** For detailed software installation instructions, refer to the *ISE Release Notes and Installation Guide*.

This tutorial assumes that the software is installed in the default location *c*:\xilinx\ISE. If you have installed the software in a different location, substitute your installation path for *c*:\xilinx\ISE in the procedures that follow.

# Optional Software Requirements

The following third-party synthesis tools are incorporated into this tutorial, and may be used in place of the Xilinx Synthesis Tool (XST):

- Synplicity Synplify/Synplify PRO 8.8.02 (or above)

- Mentor Precision Synthesis 2006a2.7 (or above)

The following third-party simulation tool is optional for this tutorial, and may be used in place of the ISE Simulator:

• ModelSim XE/SE/PE 6.3c or newer

# VHDL or Verilog?

This tutorial supports both VHDL and Verilog designs, and applies to both designs simultaneously, noting differences where applicable. You will need to decide which HDL language you would like to work through for the tutorial, and download the appropriate files for that language. XST can synthesize a mixed-language design. However, this tutorial does not go over the mixed language feature.

# Installing the Tutorial Project Files

The Stopwatch tutorial projects can be downloaded from <a href="http://www.xilinx.com/support/techsup/tutorials/tutorials10.htm">http://www.xilinx.com/support/techsup/tutorials/tutorials10.htm</a>. Download either the VHDL or the Verilog design flow project files.

After you have downloaded the tutorial project files from the Web, unzip the tutorial projects into the  $c:\xilinx\sl SEexamples$  directory, replacing any existing files in that directory.

When you unzip the tutorial project files into c:\xilinx\ISEexamples, the directory wtut\_vhd (for a VHDL design flow) or wtut\_ver (for a Verilog design flow) is created within c:\xilinx\ISEexamples, and the tutorial files are copied into the newly-created directory.

The following table lists the locations of tutorial source files.

Table 2-1: Tutorial Directories

| Directory                    | Description                     |

|------------------------------|---------------------------------|

| wtut_vhd                     | Incomplete VHDL Source Files    |

| wtut_ver                     | Incomplete Verilog Source Files |

| wtut_vhd\wtut_vhd_comple ted | Completed VHDL Source Files     |

| wtut_ver\wtut_ver_comple ted | Completed Verilog Source Files  |

**Note:** Do not overwrite any files in the solution directories.

The completed directories contain the finished HDL source files.

This tutorial assumes that the files are unzipped under c:\xilinx\ISEexamples, but you can unzip the source files into any directory with read-write permissions. If you unzip the files into a different location, substitute your project path for c:\xilinx\ISEexamples in the procedures that follow.

# Starting the ISE Software

To start ISE:

Double-click the ISE Project Navigator icon on your desktop or select Start > All Programs > Xilinx ISE Design Suite10.1 > ISE > Project Navigator.

Figure 2-1: Project Navigator Desktop Icon

# Creating a New Project

**Note:** Two methods are provided for creating a new project: Using the New Project Wizard and Using a Tcl Script. Use either method provided below.

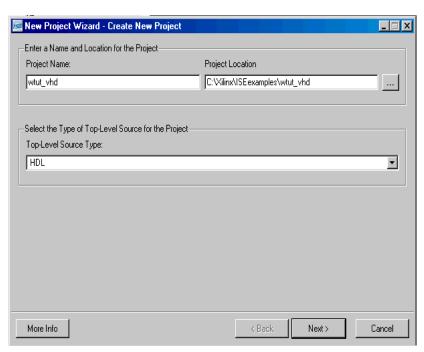

#### Creating a New Project: Using the New Project Wizard

From Project Navigator, select File > New Project.

The New Project Wizard appears.

Figure 2-2: New Project Wizard - Create New Project

- 2. In the Project Location field, browse to c:\xilinx\ISEexamples or to the directory in which you installed the project.

- 3. Type wtut\_vhd or wtut\_ver in the Project Name field.

- 4. Verify that HDL is selected as the Top-Level Source Type and click **Next**. The New Project Wizard Device Properties window appears.

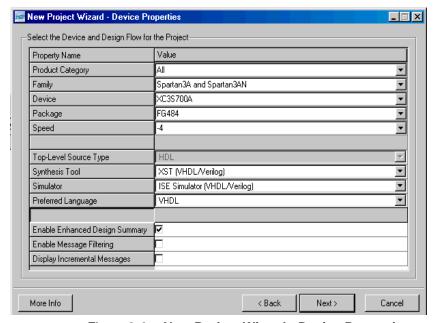

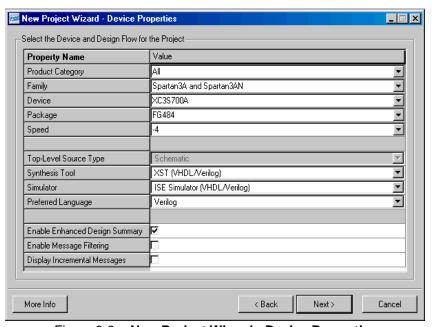

Figure 2-3: New Project Wizard - Device Properties

- 5. Select the following values in the New Project Wizard Device Properties window:

- Product Category: All

- Family: Spartan3A and Spartan3AN

- Device: XC3S700A

- ◆ Package: FG484

- ♦ Speed: -4

- Synthesis Tool: XST (VHDL/Verilog)

- Simulator: ISE Simulator (VHDL/Verilog)

- Preferred Language: VHDL or Verilog depending on preference. This will determine the default language for all processes that generate HDL files.

- 6. Click **Next**, then **Next**, and then click **Add Source** in the New Project Wizard Add Existing Sources window.

- 7. Browse to c:\xilinx\ISEexamples\wtut\_vhd or c:\xilinx\ISEexamples\wtut\_ver.

- 8. Select the following files (.vhd files for VHDL design entry or .v files for Verilog design entry) and click **Open**.

- ♦ clk\_div\_262k

- ♦ lcd\_control

- ♦ statmach

- ♦ stopwatch

- 9. Click **Next**, then **Finish** to complete the New Project Wizard.

- 10. In the Adding Source Files dialog box, verify that all added HDL files are associated with Synthesis/Imp + Simulation, then click **OK**.

#### Creating a New Project: Using a Tcl Script

- 1. With Project Navigator open, select the Tcl Shell tab.

- 2. Change the current working directory to the directory where the tutorial source files were unzipped by typing cd c:/xilinx/ISEexamples/wtut\_vhd (VHDL design entry) or cd c:/xilinx/ISEexamples/wtut ver (Verilog design entry).

- 3. Run the project creation Tcl script by typing source create\_wtut\_vhd.tcl (VHDL design entry) or source create\_wtut\_ver.tcl (Verilog design entry).

- 4. (VHDL only) Once the project is created and opened, right-click on the device line and select **Properties...** Change the Preferred Language: to **VHDL**. This will determine the default language for all processes that generate HDL files.

# Stopping the Tutorial

You may stop the tutorial at any time and save your work by selecting **File > Save All**.

# **Design Description**

The design used in this tutorial is a hierarchical, HDL-based design, which means that the top-level design file is an HDL file that references several other lower-level macros. The lower-level macros are either HDL modules or IP modules.

The design begins as an unfinished design. Throughout the tutorial, you will complete the design by generating some of the modules from scratch and by completing others from existing files. When the design is complete, you will simulate it to verify the design's functionality.

In the runner's stopwatch design, there are five external inputs and four external output buses. The system clock is an externally generated signal. The following list summarizes the input and output signals of the design.

# Inputs

The following are input signals for the tutorial stopwatch design.

#### strtstop

Starts and stops the stopwatch. This is an active low signal which acts like the start/stop button on a runner's stopwatch.

#### reset

Puts the stopwatch in clocking mode and resets the time to 0:00:00.

#### clk

Externally generated system clock.

#### mode

Toggles between clocking and timer modes. This input is only functional while the clock or timer is not counting.

#### lap\_load

This is a dual function signal. In clocking mode it displays the current clock value in the 'Lap' display area. In timer mode it loads the pre assigned values from the ROM to the timer display when the timer is not counting.

# **Outputs**

The following are outputs signals for the design.

#### lcd\_e, lcd\_rs, lcd\_rw

These outputs are the control signals for the LCD display of the Spartan-3A demo board used to display the stopwatch times.

#### • sf\_d[7:0]

Provides the data values for the LCD display.

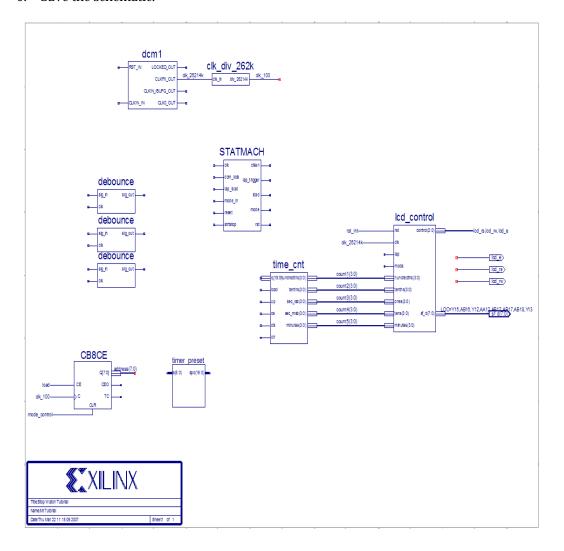

#### **Functional Blocks**

The completed design consists of the following functional blocks.

#### clk\_div\_262k

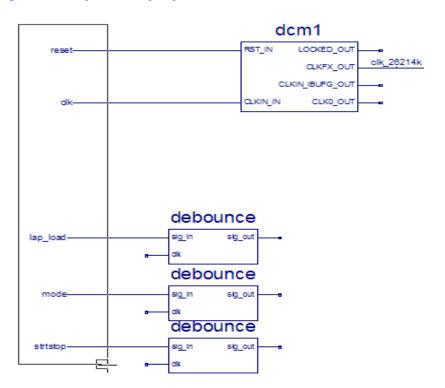

Macro which divides a clock frequency by 262,144. Converts 26.2144 MHz clock into 100 Hz 50% duty cycle clock.

#### dcm1

Clocking Wizard macro with internal feedback, frequency controlled output, and duty-cycle correction. The CLKFX\_OUT output converts the 50 MHz clock of the Spartan-3A demo board to 26.2144 MHz.

#### debounce

Schematic module implementing a simplistic debounce circuit for the strtstop, mode, and lap\_load input signals.

#### lcd\_control

Module controlling the initialization of and output to the LCD display.

#### statmach

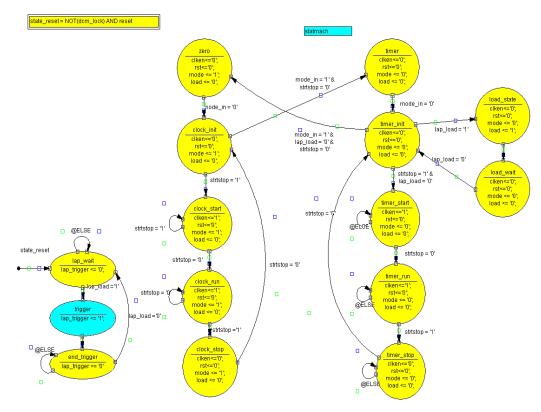

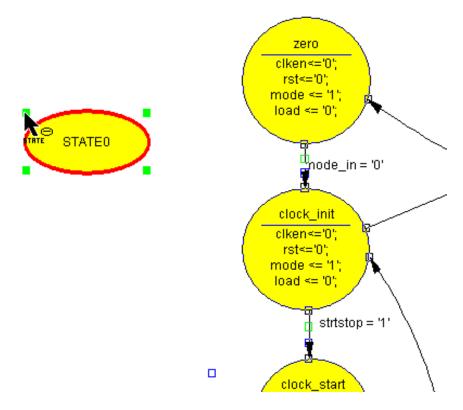

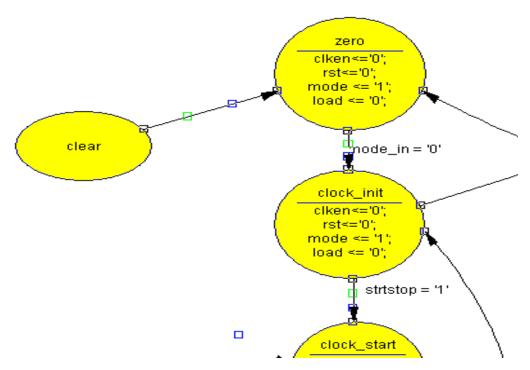

State Machine module defined and implemented in State Diagram Editor. Controls the state of the stopwatch.

#### timer\_preset

CORE Generator™ 64x20 ROM. This macro contains 64 preset times from 0:00:00 to 9:59:99 which can be loaded into the timer.

#### time\_cnt

Up/down counter module which counts between 0:00:00 to 9:59:99 decimal. This macro has five 4-bit outputs, which represent the digits of the stopwatch time.

# **Design Entry**

28

For this hierarchical design, you will examine HDL files, correct syntax errors, create an HDL macro, and add a CORE Generator and a Clocking module. You will create and use

each type of design macro. All procedures used in the tutorial can be used later for your own designs.

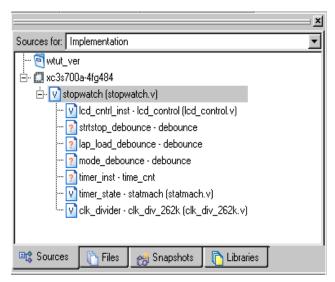

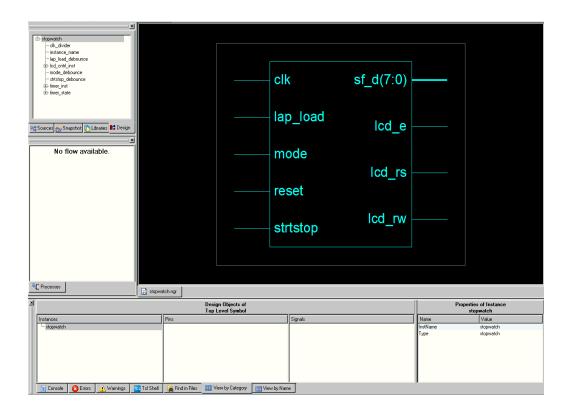

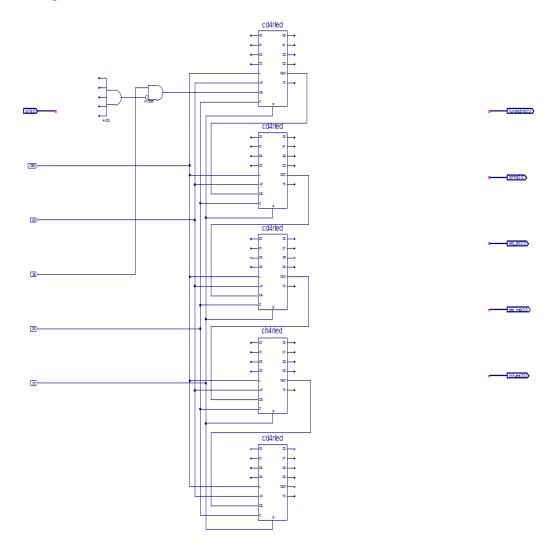

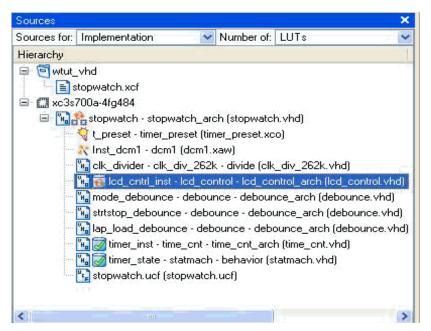

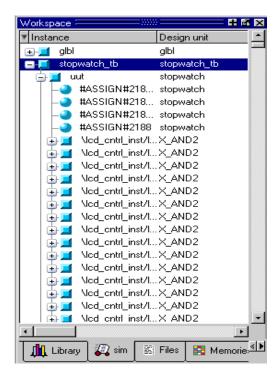

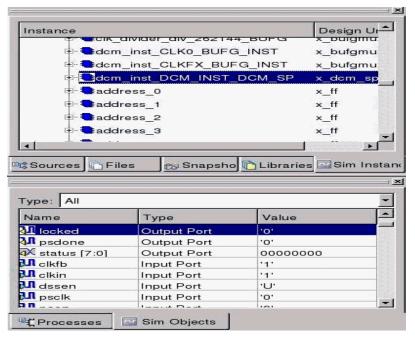

With the wtut\_vhd.ise or wtut\_ver.ise project open in Project Navigator, the Sources tab displays all of the source files currently added to the project, with the associated entity or module names (see Figure 2-4). In the current project, time\_cnt is instantiated, but the associated entity or module is not defined in the project.

Instantiated components with no entity or module declaration are displayed with a red question mark.

Figure 2-4: Sources Tab Showing Completed Design

# **Adding Source Files**

HDL files must be added to the project before they can be synthesized. Three HDL files have already been added to this project. An additional file must be added.

- 1. Select Project > Add Source.

- 2. Select time\_cnt.vhd or time\_cnt.v from the project directory and click Open.

- 3. In the Adding Source Files dialog box, verify that time\_cnt is associated with Synthesis/Imp + Simulation and click OK.

**Note:** Alternatively, the time\_cnt.vhd file could be added to the project by entering the following command in the Tcl Shell tab.

```

xfile add time_cnt.vhd

```

The red question-mark (?) for *time\_cnt* should change to show the VHD file icon.

Figure 2-5: time\_cnt.vhd File in Sources Tab

Each source Design unit is represented under the sources tab using the following syntax: <instance name> - <entity name> - <architecture name> - (<file name>).

# Checking the Syntax

To check the syntax of source files:

- Select stopwatch.vhd or stopwatch.v in the Sources tab.

When you select the HDL file, the Processes tab displays all processes available for this file.

- 2. In the Processes tab, click the + next to Synthesize to expand the process hierarchy.

- 3. Double-click **Check Syntax** in the Synthesize hierarchy.

Note: Check Syntax is not available when Synplify is selected as the synthesis tool.

# Correcting HDL Errors

The time\_cnt module contains a syntax error that must be corrected. The red "x" beside the Check Syntax process indicates an error was found during the analysis. In the Console tab of the Transcript window, Project Navigator reports errors with a red (X) and warnings with a yellow (!).

To display the error in the source file:

- 1. Click the file name in the error message in the Console or Errors tab. The source code comes up in the main display tab.

- 2. Correct any errors in the HDL source file. The comments next to the error explain this simple fix.

- 3. Select **File > Save** to save the file.

- 4. Re-analyze the file by selecting the HDL file and double-clicking **Check Syntax**.

# Creating an HDL-Based Module

Next you will create a module from HDL code. With ISE, you can easily create modules from HDL code using the ISE Text Editor. The HDL code is then connected to your top-level HDL design through instantiation and is compiled with the rest of the design.

You will author a new HDL module. This macro will be used to debounce the strtstop, mode and lap\_load inputs.

#### Using the New Source Wizard and ISE Text Editor

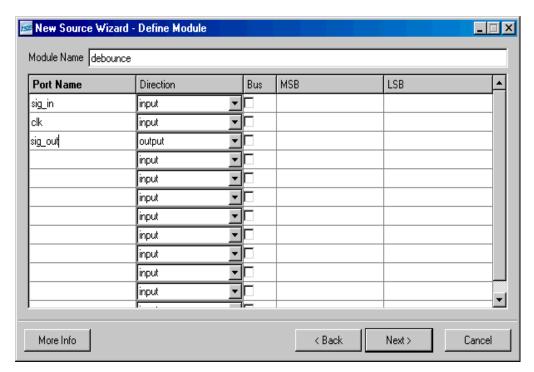

In this section, you create a file using the New Source wizard, specifying the name and ports of the component. The resulting HDL file is then modified in the ISE Text Editor.

To create the source file:

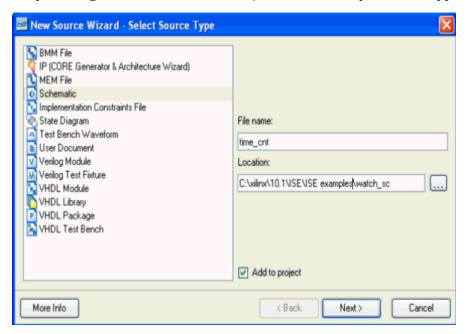

1. Select Project > New Source.

The dialog box New Source Wizard opens in which you specify the type of source you want to create.

- 2. Select VHDL Module or Verilog Module.

- 3. In the File Name field, type debounce.

- 4. Click Next.

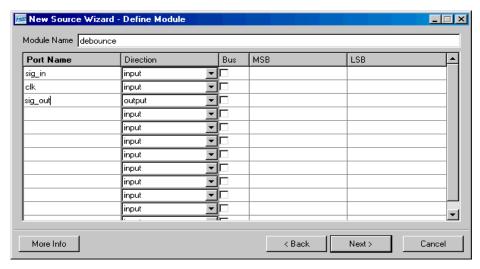

- 5. Enter two input ports named sig\_in and clk and an output port named sig\_out for the debounce component in this way:

- a. In the first three Port Name fields type sig\_in, clk and sig\_out.

- b. Set the Direction field to input for sig\_in and clk and to output for sig\_out.

- c. Leave the Bus designation boxes unchecked.

Figure 2-6: New Source Wizard for Verilog

- 6. Click **Next** to complete the Wizard session.

- A description of the module displays.

- 7. Click **Finish** to open the empty HDL file in the ISE Text Editor.

The VHDL file is displayed in Figure 2-7. The Verilog HDL file is displayed in Figure 2-8.

```

debounce - Behavioral

Project Name:

Target Devices:

Tool versions:

-- Description:

13

-- Dependencies:

-- Revision:

-- Revision 0.01 - File Created

15

-- Additional Comments:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

20

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

29

entity debounce is

Port ( sig_in : in STD_LOGIC;

clk : in STD_LOGIC;

sig_out : out STD_LOGIC);

31

32

end debounce;

architecture Behavioral of debounce is

begin

40

end Behavioral;

```

Figure 2-7: VHDL File in ISE Text Editor

```

timescale 1ns / 1ps

2

3

// Company:

// Engineer:

4

5

177

// Create Date:

6

14:12:53 03/15/2007

// Design Name:

7

8

// Module Name:

debounce

9

// Project Name:

10

// Target Devices:

// Tool versions:

11

12

// Description:

13

17

14

// Dependencies:

15

17

// Revision:

16

// Revision 0.01 - File Created

17

18

// Additional Comments:

19

20

module debounce(sig in, clk, sig out);

21

2.2

input sig_in;

23

input clk;

24

output sig_out;

25

26

27

endmodule

28

```

Figure 2-8: Verilog File in ISE Text Editor

In the ISE Text Editor, the ports are already declared in the HDL file, and some of the basic file structure is already in place. Keywords are displayed in blue, comments in green, and values are black. The file is color-coded to enhance readability and help you recognize typographical errors.

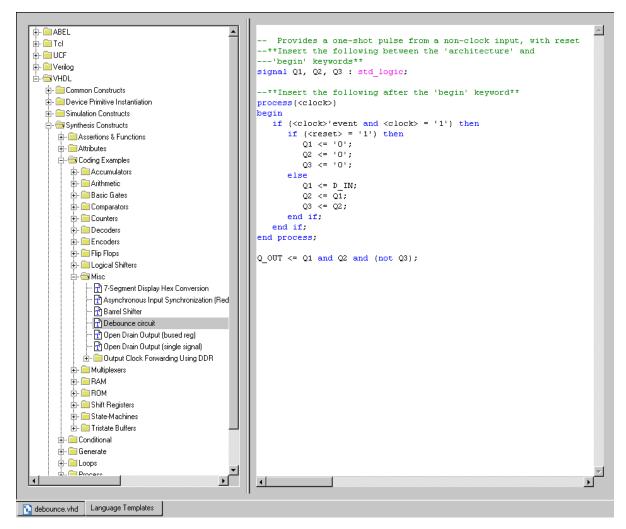

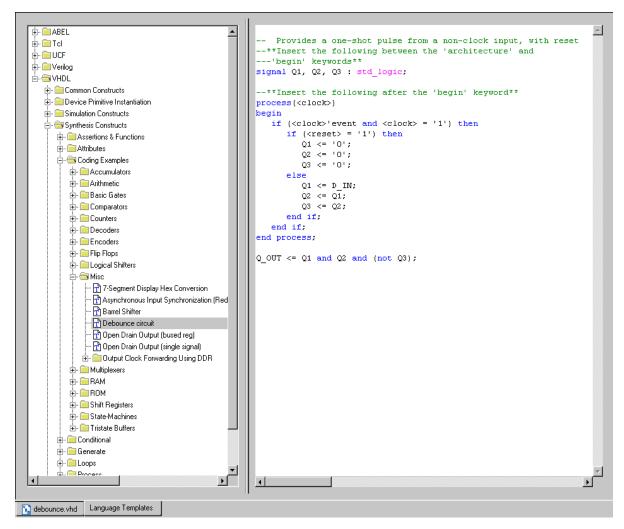

#### Using the Language Templates

The ISE Language Templates include HDL constructs and synthesis templates which represent commonly used logic components, such as counters, D flip-flops, multiplexers, and primitives. You will use the Debounce Circuit template for this exercise.

**Note:** You can add your own templates to the Language Templates for components or constructs that you use often.

To invoke the Language Templates and select the template for this tutorial:

- From Project Navigator, select Edit > Language Templates.

Each HDL language in the Language Templates is divided into five sections: Common Constructs, Device Primitive Instantiation, Simulation Constructs, Synthesis Constructs and User Templates. To expand the view of any of these sections, click the + next to the section. Click any of the listed templates to view the template contents in the right pane.

- 2. Under either the VHDL or Verilog hierarchy, expand the Synthesis Constructs hierarchy, expand the Coding Examples hierarchy, expand the Misc hierarchy, and select the template called [One-shot,] Debounce Circuit. Use the appropriate template for the language you are using.

- Upon selection, the HDL code for a debounce circuit is displayed in the right pane.

Figure 2-9: Language Templates

#### Adding a Language Template to Your File

You will now use the drag and drop method for adding templates to your HDL file. Refer to "Working with Language Templates" in the ISE Help for additional usability options.

To add the template to your HDL file using the drag and drop method:

- Select Window > Tile Vertically to show both the HDL file and the Language Templates window.

- 2. Click and drag the **Debounce Circuit** name from the Language Template topology into the debounce.vhd file under the architecture begin statement, or into the debounce.v file under the module and pin declarations.

- 3. Close the Language Templates window.

- 4. (Verilog only) Complete the Verilog module by doing the following:

- a. Remove the reset logic (not used in this design) by deleting the three lines beginning with if and ending with else.

- b. Change < reg\_name > to q in all six locations.

- c. Change <clock> to clk; <input> to sig\_in; and <output> to sig\_out.

- 5. (VHDL only) Complete the VHDL module by doing the following:

- a. Move the line beginning with the word **signal** so that it is between the **architecture** and **begin** keywords.

- b. Remove the reset logic (not used in this design) by deleting the five lines beginning with if (<reset>... and ending with else and delete one of the end if; lines.

- c. Use Edit > Replace to change <clock> to clk; D\_IN to sig\_in; and Q\_OUT to sig\_out.

You now have complete and functional HDL code.

- 6. Save the file by selecting **File > Save**.

- 7. Select one of the debounce instances in the Sources tab.

- 8. In the Processes tab, double-click Check Syntax.

- 9. Close the ISE Text Editor.

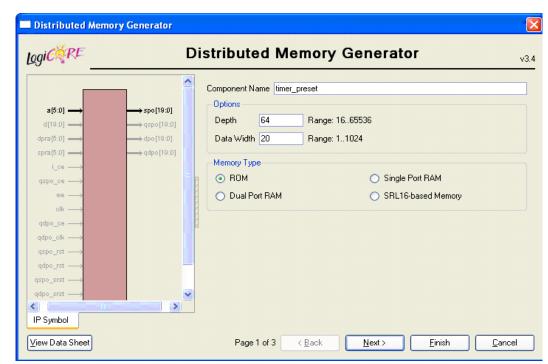

# Creating a CORE Generator Module

CORE Generator is a graphical interactive design tool that enables you to create high-level modules such as memory elements, math functions and communications and IO interface cores. You can customize and pre-optimize the modules to take advantage of the inherent architectural features of the Xilinx FPGA architectures, such as Fast Carry Logic, SRL16s, and distributed and block RAM.

In this section, you will create a CORE Generator module called timer\_preset. The module will be used to store a set of 64 values to load into the timer.

# Creating a CORE Generator Module

To create a CORE Generator module:

- 1. In Project Navigator, select **Project > New Source**.

- 2. Select IP (Coregen & Architecture Wizard).

- 3. Type timer\_preset in the File name field.

- 4. Click Next.

- 5. Double-click Memories & Storage Elements, then double-click RAMs & ROMs.

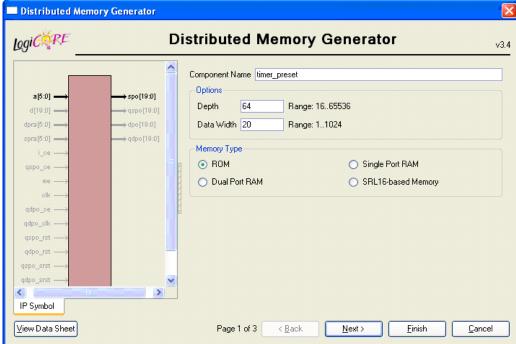

- 6. Select **Distributed Memory Generator**, then click **Next** and click **Finish** to open the Distributed Memory Generator customization GUI. This customization GUI enables you to customize the memory to the design specifications.

- 7. Fill in the Distributed Memory Generator customization GUI with the following settings:

- Component Name: **timer\_preset** Defines the name of the module.

- Depth: **64** Defines the number of values to be stored

- Data Width: **20** Defines the width of the output bus.

- ♦ Memory Type: ROM

- Click Next.

- Leave Input and output options as Non Registered; Click **Next**.

◆ Coefficients File: Click the **Browse** button and select definition1\_times.coe.

Figure 2-10: CORE Generator - Distributed Memory Generator Customization GUI

- 8. Check that *only* the following pins are used (used pins are highlighted on the symbol on the left side of the customization GUI):

- a[5:0]

- spo[19:0]

- Click Finish.

The module is created and automatically added to the project library.

**Note:** A number of files are added to the project directory. Some of these files are:

- timer\_preset.vho or timer\_preset.veo

These are the instantiation templates used to incorporate the CORE Generator module into your source HDL.

- timer\_preset.vhd or timer\_preset.v

These are HDL wrapper files for the core and are used only for simulation.

timer\_preset.edn

This file is the netlist that is used during the Translate phase of implementation.

timer\_preset.xco

This file stores the configuration information for the timer\_preset module and is used as a project source.

timer\_preset.mif

This file provides the initialization values of the ROM for simulation.

### Instantiating the CORE Generator Module in the HDL Code

Next, instantiate the CORE Generator module in the HDL code using either a VHDL flow or a Verilog flow.

#### **VHDL Flow**

To instantiate the CORE Generator module using a VHDL flow:

- 1. In Project Navigator, double-click stopwatch. vhd to open the file in ISE Text Editor.

- 2. Place your cursor after the line that states:

```

-- Insert CORE Generator ROM component declaration here

```

3. Select **Edit** > **Insert File**, then select timer\_preset.vho *and click* **Open**. The VHDL template file for the CORE Generator instantiation is inserted.

```

121

----- Begin Cut here for COMPONENT Declaration ----- COMP_TAG

122

component timer_preset

123

port (

a: IN std logic VECTOR(5 downto 0);

124

spo: OUT std logic VECTOR(19 downto 0));

125

126 end component;

127

-- Synplicity black box declaration

128

129

attribute syn black box : boolean;

130 attribute syn_black_box of timer_preset: component is true;

131

132 -- COMP TAG END ----- End COMPONENT Declaration ------

```

Figure 2-11: VHDL Component Declaration for CORE Generator Module

4. Highlight the inserted code from

```

-- Begin Cut here for INSTANTIATION Template ----

to

--INST_TAG_END ----- END INSTANTIATION Template -----

```

- 5. Select **Edit > Cut**.

- 6. Place the cursor after the line that states:

```

--Insert CORE Generator ROM Instantiation here

```

- 7. Select **Edit > Paste** to place the core instantiation.

- 8. Change the instance name from your\_instance\_name to t\_preset.

- 9. Edit this instantiated code to connect the signals in the Stopwatch design to the ports of the CORE Generator module as shown in Figure 2-12.

Figure 2-12: VHDL Component Instantiation of CORE Generator Module

- 10. The inserted code of timer\_preset.vho contains several lines of commented text for instruction and legal documentation. Delete these commented lines if desired.

- 11. Save the design using **File > Save**, and close the ISE Text Editor.

### Verilog Flow

To instantiate the CORE Generator module using a Verilog flow:

- 1. In Project Navigator, double-click stopwatch.v to open the file in the ISE Text Editor.

- 2. Place your cursor after the line that states:

```

//Place the Coregen module instantiation for timer_preset here

```

- 3. Select Edit > Insert File, and select timer\_preset.veo.

- 4. The inserted code of timer\_preset.veo contains several lines of commented text for instruction and legal documentation. Delete these commented lines if desired.

- 5. Change the instance name from YourInstanceName to t\_preset.

- 6. Edit this code to connect the signals in the Stopwatch design to the ports of the CORE Generator module as shown in Figure 2-13.

Figure 2-13: Verilog Component Instantiation of the CORE Generator Module

7. Save the design using File > Save and close stopwatch.v in the ISE Text Editor.

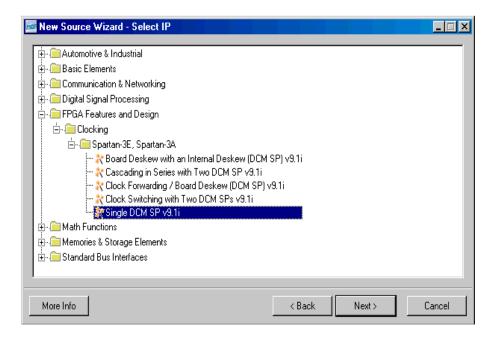

# Creating a DCM Module

The Clocking Wizard, a part of the Xilinx Architecture Wizard, enables you to graphically select Digital Clock Manager (DCM) features that you wish to use. In this section you will create a basic DCM module with CLK0 feedback and duty-cycle correction.

# Using the Clocking Wizard

To create the dcm1 module:

- 1. In Project Navigator, select **Project > New Source**.

- 2. In the New Source dialog box, select **IP (CoreGen & Architecture Wizard)** source and type **dcm1** for the file name.

- 3. Click Next.

- 4. In the Select IP dialog box, select FPGA Features and Design > Clocking > Spartan-3E, Spartan-3A > Single DCM SP.

Figure 2-14: Selecting Single DCM IP Type

- 5. Click **Next**, then **Finish**. The Clocking Wizard is launched.

- 6. Verify that **RST**, **CLK0** and **LOCKED** ports are selected.

- 7. Select **CLKFX** port.

- 8. Type **50** and select **MHz** for the Input Clock Frequency.

- 9. Verify the following settings:

- ♦ Phase Shift: **NONE**

- **♦** CLKIN Source: External, Single

- ♦ Feedback Source: Internal

- Feedback Value: 1X

- Use Duty Cycle Correction: Selected

- 10. Click the Advanced button.

- 11. Select Wait for DCM lock before DONE Signal goes high.

- 12. Click **OK**.

- 13. Click Next, and then click Next again.

- 14. Select **Use output frequency** and type **26.2144** in the box and select **MHz**.

$$(26.2144Mhz)/2^{18} = 100Hz$$

15. Click **Next**, and then click **Finish**.

The dcml.xaw file is added to the list of project source files in the Sources tab.

### Instantiating the dcm1 Macro - VHDL Design

Next, you will instantiate the dcm1 macro for your VHDL or Verilog design. To instantiate the dcm1 macro for the VHDL design:

- 1. In Project Navigator, in the Sources tab, select dcm1.xaw.

- 2. In the Processes tab, right-click **View HDL Instantiation Template** and select **Properties**.

- 3. Choose **VHDL** for the HDL Instantiation Template Target Language value and click **OK**

- 4. In the Processes tab, double-click View HDL Instantiation Template.

- 5. Highlight the component declaration template in the newly opened HDL Instantiation Template (dcml.vhi), shown below.

```

-- Notes:

-- 1) This instantiation template has been au

6

-- std logic and std logic vector for the por

7

-- 2) To use this template to instantiate thi:

8

9

COMPONENT dcm1

10

PORT (

11

CLKIN IN : IN std logic;

RST IN : IN std logic;

12

13

CLKFX OUT : OUT std logic;

14

CLKIN IBUFG OUT : OUT std logic;

15

CLKO OUT : OUT std logic;

16

LOCKED OUT : OUT std logic

17

);

END COMPONENT:

```

Figure 2-15: VHDL DCM Component Declaration

- 6. Select Edit > Copy.

- 7. Place the cursor in the *stopwatch.vhd* file in a section labeled

```

-- Insert dcml component declaration here.

```

- 8. Select **Edit > Paste** to paste the component declaration.

- 9. Highlight the instantiation template in the newly opened HDL Instantiation Template, shown below.

```

10

20

Inst dcm1: dcm1 PORT MAP (

21

CLKIN IN => ,

22

RST IN => ,

23

CLKFX OUT =>

CLKIN IBUFG OUT => ,

24

CLKO OUT => ,

25

26

LOCKED OUT =>

27

1:

```

Figure 2-16: VHDL DCM Component Instantiation

- 10. Select Edit > Copy.

- 11. Place the cursor in the stopwatch. vhd file below the line labeled

```

"-- Insert dcml instantiation here".

```

- 12. Select **Edit > Paste** to paste the instantiation template.

- 13. Make the necessary changes as shown in the figure below.

```

141

----- Insert dcm1 instantiation here

142

Inst dcm1: dcm1 PORT MAP (

143

CLKIN IN => clk,

144

RST IN => reset,

CLKFX OUT => clk 26214k,

145

CLKIN IBUFG OUT => open,

146

CLKO OUT => open,

147

148

LOCKED OUT => locked

149

```

Figure 2-17: VHDL Instantiation for dcm1

14. Select File > Save to save the stopwatch. vhd file.

### Instantiating the dcm1 Macro - Verilog

To instantiate the dcm1 macro for your Verilog design:

- 1. In Project Navigator, in the Sources tab, select dcm1.xaw.

- 2. In the Processes tab, double-click View HDL Instantiation Template.

- 3. From the newly opened HDL Instantiation Template (dcml.tfi), copy the instantiation template, shown below.

```

4  // Instantiate the module

5  dcm1 instance_name (

6    .CLKIN_IN(CLKIN_IN),

7    .RST_IN(RST_IN),

8    .CLKFX_OUT(CLKFX_OUT),

9    .CLKIN_IBUFG_OUT(CLKIN_IBUFG_OUT),

10    .CLKO_OUT(CLKO_OUT),

11    .LOCKED_OUT(LOCKED_OUT)

12  );

```

Figure 2-18: dcm1 Macro and Instantiation Templates

- 4. Paste the instantiation template into the section in stopwatch.v labeled //Insert dcml instantiation here.

- 5. Make the necessary changes as shown in the figure below.

```

45 //Insert dcm1 instantiation here

46 dcm1 instance_name (

47 .CLKIN_IN(clk),

48 .RST_IN(reset),

49 .CLKFX_OUT(clk_26214k),

50 .CLKIN_IBUFG_OUT(),

51 .CLKO_OUT(),

52 .LOCKED_OUT(locked)

53 );

```

Figure 2-19: Verilog Instantiation for dcm1

6. Select **File > Save** to save the stopwatch.v file.

# Synthesizing the Design

So far you have been using XST (the Xilinx synthesis tool) for syntax checking. Next, you will synthesize the design using either XST, Synplify/Synplify Pro or Precision. The synthesis tool uses the design's HDL code and generates a supported netlist type (EDIF or NGC) for the Xilinx implementation tools. The synthesis tool performs three general steps (although all synthesis tools further break down these general steps) to create the netlist:

#### Analyze / Check Syntax

Checks the syntax of the source code.

#### Compile

Translates and optimizes the HDL code into a set of components that the synthesis tool can recognize.

#### Map

**Translates the** components from the compile stage into the target technology's primitive components.

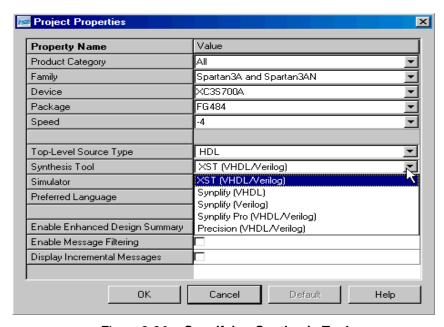

The synthesis tool can be changed at any time during the design flow. To change the synthesis tool:

- Select the targeted part in the Sources tab.

- 2. Select Source > Properties.

- 3. In the Project Properties dialog box, click on the Synthesis Tool value and use the pull-down arrow to select the desired synthesis tool from the list.

Figure 2-20: Specifying Synthesis Tool

**Note:** If you do not see your synthesis tool among the options in the list, you may not have the software installed or may not have it configured in ISE. The Synthesis tools are configured in the Preferences dialog box (**Edit > Preferences**, expand ISE General, then click **Integrated Tools**).

Changing the design flow results in the deletion of implementation data. You have not yet created any implementation data in this tutorial. For projects that contain implementation data, Xilinx recommends that you take a snapshot of the project before changing the

synthesis tool to preserve this data. For more information about taking a snapshot, see "Creating a Snapshot" in Chapter 1.

A summary of available synthesis tools is available in "Overview of Synthesis Tools" in Chapter 1

Read the section for your synthesis tool:

- "Synthesizing the Design using XST"

- "Synthesizing the Design using Synplify/Synplify Pro"

- "Synthesizing the Design Using Precision Synthesis"

# Synthesizing the Design using XST

Now that you have created and analyzed the design, the next step is to synthesize the design. During synthesis, the HDL files are translated into gates and optimized for the target architecture.

Processes available for synthesis using XST are as follows:

- View Synthesis Report

- Gives a synthesis mapping and timing summary as well as a list of optimizations that took place.

- View RTL Schematic

- Generates a schematic view of your RTL netlist.

- View Technology Schematic

- Generates a schematic view of your Technology netlist.

- Check Syntax

- Verifies that the HDL code is entered properly.

- Generate Post-Synthesis Simulation Model

- Creates HDL simulation models based on the synthesis netlist.

### **Entering Constraints**

XST supports a User Constraint File (UCF) style syntax to define synthesis and timing constraints. This format is called the Xilinx Constraint File (XCF), and the file has an .xcf file extension. XST uses the .xcf extension to determine if the file is a constraints file.

To create a new Xilinx Constraint File:

- 1. Select Project > Add Source.

- 2. In the Add Existing Sources dialog box, change the Files of type: to 'All Files (\*.\*) and then select and add **stopwatch.xcf**.

- 3. Notice that stopwatch.xcf is added as a User Document.

**Note:** In place of the three steps above, you may add the .xcf file through the Tcl Shell, using the following command and then selecting **View > Refresh**.

#### xfile add stopwatch.xcf

- 4. Double-click stopwatch.xcf to open the file in the ISE Text Editor.

- 5. The following constraints should exist in the stopwatch.xcf file:

```

NET "CLK" TNM_NET = "CLK_GROUP";

```

```

TIMESPEC "TS_CLK"=PERIOD "CLK_GROUP" 20 ns;

BEGIN MODEL stopwatch

NET "sf_d<7>" LOC = "Y15";

NET "sf_d<6>" LOC = "AB16";

NET "sf_d<5>" LOC = "Y16";

NET "sf_d<4>" LOC = "AA12";

NET "sf_d<3>" LOC = "AB12";

NET "sf_d<2>" LOC = "AB17";

NET "sf_d<1>" LOC = "AB18";

NET "sf_d<0>" LOC = "Y13";

END;

```

6. Close stopwatch.xcf.

**Note:** For more constraint options in the implementation tools, see "Using the Constraints Editor" and "Using the Floorplan Editor" in Chapter 5, "Design Implementation."

# **Entering Synthesis Options**

Synthesis options enable you to modify the behavior of the synthesis tool to make optimizations according to the needs of the design. One commonly used option is to control synthesis to make optimizations based on area or speed. Other options include controlling the maximum fanout of a flip-flop output or setting the desired frequency of the design.

To enter synthesis options:

- 1. Select stopwatch.vhd (or stopwatch.v) in the Sources tab.

- 2. In the Processes tab, right-click the **Synthesize** process and select **Properties**.

- Under the Synthesis Options tab, click in the Synthesis Constraints File property field and enter stopwatch.xcf.

- 4. Check the Write Timing Constraints box.

- 5. Click OK.

# Synthesizing the Design

Now you are ready to synthesize your design. To take the HDL code and generate a compatible netlist:

- 1. Select stopwatch.vhd (or stopwatch.v).

- 2. Double-click the **Synthesize** process in the Processes tab.

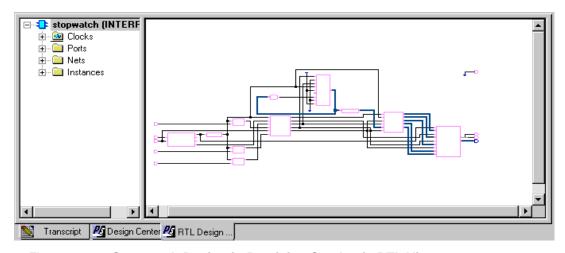

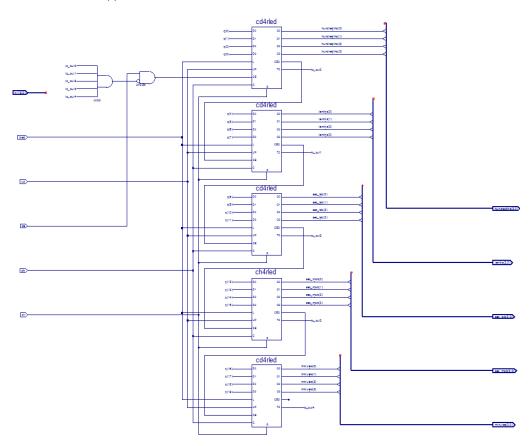

# The RTL / Technology Viewer

XST can generate a schematic representation of the HDL code that you have entered. A schematic view of the code helps you analyze your design by displaying a graphical connection between the various components that XST has inferred. There are two forms of the schematic representation:

- **RTL View** Pre-optimization of the HDL code.

- Technology View Post-synthesis view of the HDL design mapped to the target technology.

To view a schematic representation of your HDL code:

- 1. In the Processes tab, click the + next to Synthesize to expand the process hierarchy.

- 2. Double-click View RTL Schematic or View Technology Schematic.

The RTL Viewer displays the top level schematic symbol for the design. Double-click on the symbol to push into the schematic and view the various design elements and connectivity. Right-click the schematic to view the various operations that can be performed in the schematic viewer.

Figure 2-21: RTL Viewer

You have completed XST synthesis. An NGC file now exists for the Stopwatch design. To continue with the HDL flow:

- Go to Chapter 4, "Behavioral Simulation," to perform a pre-synthesis simulation of this design.

OR

- Proceed to Chapter 5, "Design Implementation," to place and route the design.

**Note:** For more information about XST constraints, options, reports, or running XST from the command line, see the XST User Guide. This guide is available in the collection of software manuals and is accessible from ISE by selecting **Help > Software Manuals**, or from the web at <a href="http://toolbox.xilinx.com/docsan/xilinx10/books/manuals.pdf">http://toolbox.xilinx.com/docsan/xilinx10/books/manuals.pdf</a>

# Synthesizing the Design using Synplify/Synplify Pro

Now that you have entered and analyzed the design, the next step is to synthesize the design. In this step, the HDL files are translated into gates and optimized to the target

architecture. To access Synplify's RTL viewer and constraints editor you must run Synplify outside of ISE.

To synthesize the design, set the global synthesis options:

- 1. Select stopwatch.vhd (or stopwatch.v).

- 2. In the Processes tab, right-click the **Synthesize** process and select **Properties**.

- 3. Check the Write Vendor Constraint File box.

- 4. Click **OK** to accept these values.

- 5. Double-click the **Synthesize** process to run synthesis.

**Note:** This step can also be done by selecting stopwatch.vhd (or stopwatch.v), clicking **Synthesize** in the Processes tab, and selecting **Process > Run**.

Processes available in Synplify and Synplify Pro synthesis include:

#### • View Synthesis Report

Lists the synthesis optimizations that were performed on the design and gives a brief timing and mapping report.

#### View RTL Schematic

Accessible from the Launch Tools hierarchy, this process displays Synplify or Synplify Pro with a schematic view of your HDL code

### • View Technology Schematic

Accessible from the Launch Tools hierarchy, this process displays Synplify or Synplify Pro with a schematic view of your HDL code mapped to the primitives associated with the target technology.

# **Examining Synthesis Results**

To view overall synthesis results, double-click **View Synthesis Report** under the **Synthesize** process. The report consists of the following four sections:

- "Compiler Report"

- "Mapper Report"

- "Timing Report"

- "Resource Utilization"

### Compiler Report

The compiler report lists each HDL file that was compiled, names which file is the top level, and displays the syntax checking result for each file that was compiled. The report also lists FSM extractions, inferred memory, warnings on latches, unused ports, and removal of redundant logic.

**Note:** Black boxes (modules not read into a design environment) are always noted as unbound in the Synplify reports. As long as the underlying netlist (.ngo, .ngc or .edn) for a black box exists in the project directory, the implementation tools merge the netlist into the design during the Translate phase.

#### Mapper Report

The mapper report lists the constraint files used, the target technology, and attributes set in the design. The report lists the mapping results of flattened instances, extracted counters, optimized flip-flops, clock and buffered nets that were created, and how FSMs were coded.

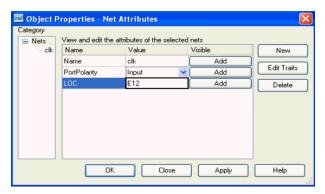

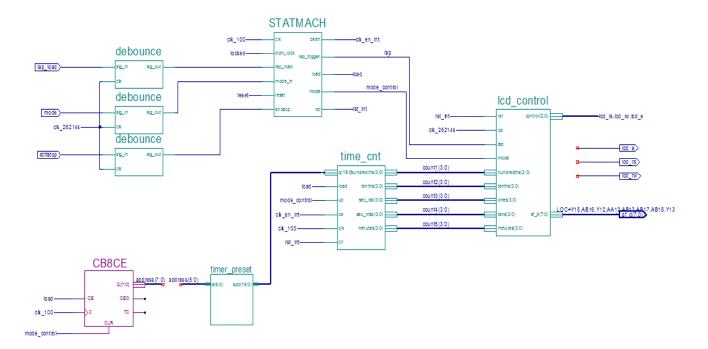

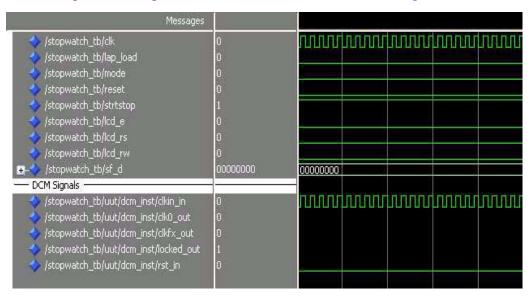

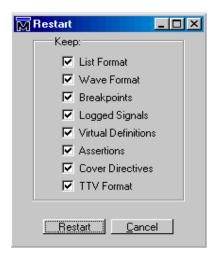

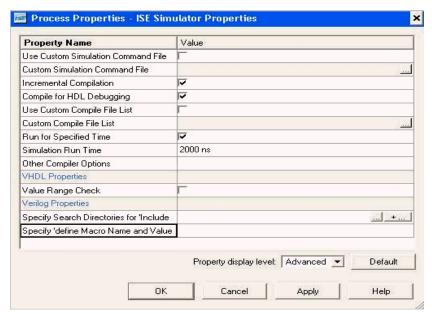

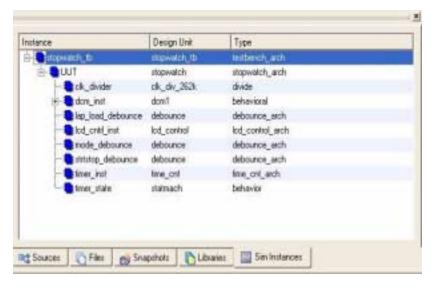

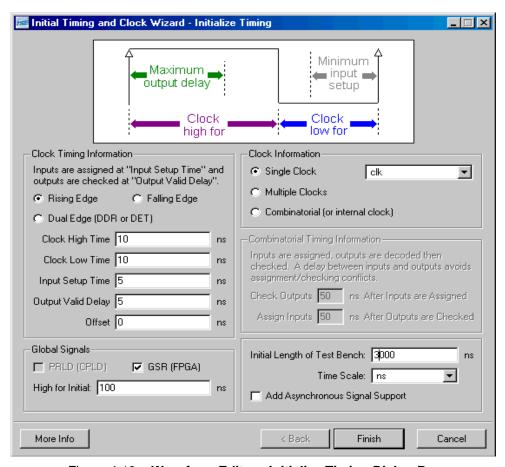

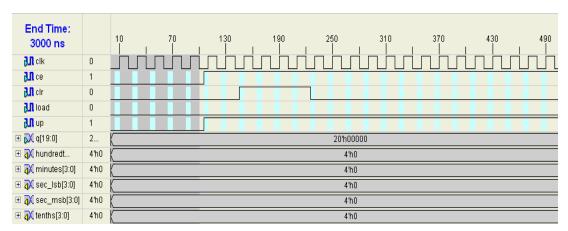

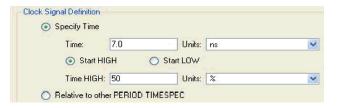

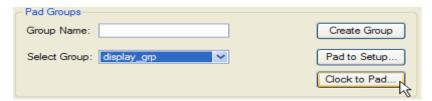

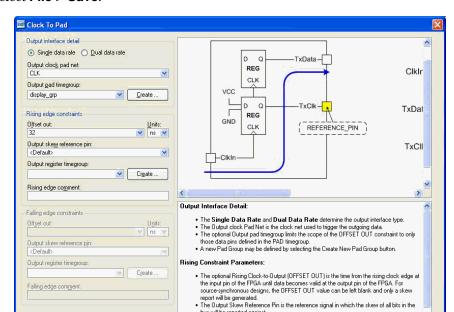

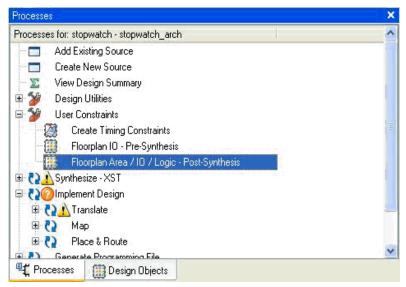

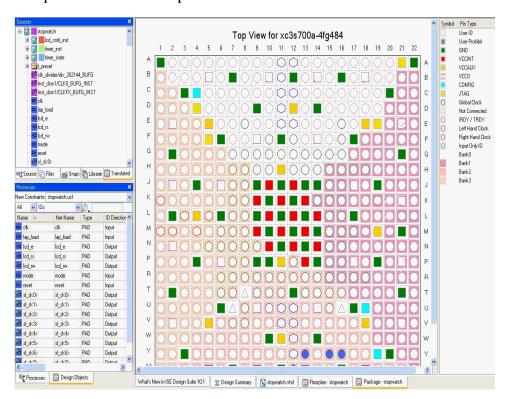

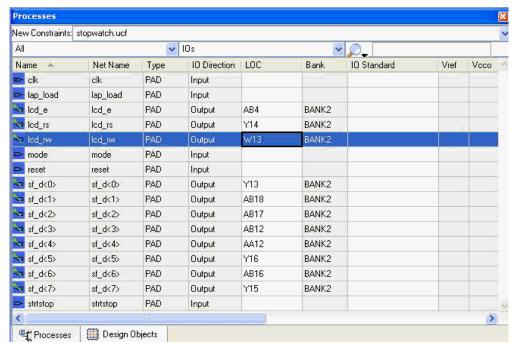

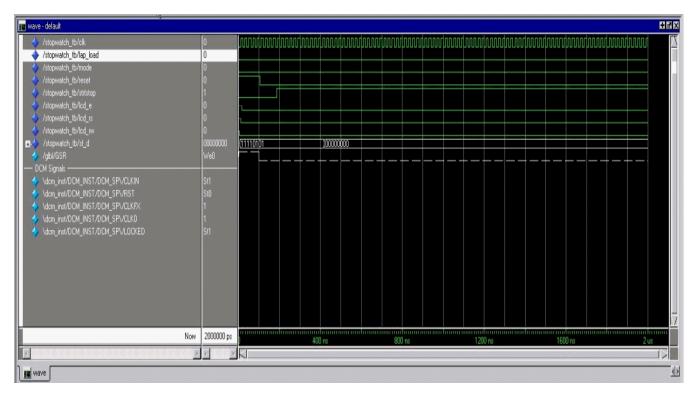

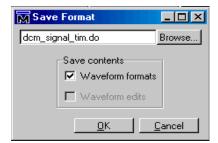

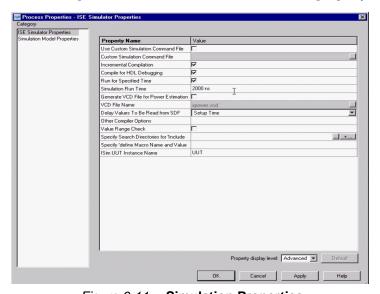

#### **Timing Report**