## EE 330 Midterm Exam #01

Name: \_\_\_\_\_Score\_\_\_\_

Instructions:

- The exam is for individual work, with closed-book, closed-notes, no electronic devices.

- One sheet of formulas of US letter size is allowed. No other papers allowed.

- Write brief solutions in the space provided on this exam. If necessary, you can write on the backside but clearly mark the question numbers.

- Do not erase. Just cross out unwanted writing, and write correct answers in clean space.

- Specific parameters are given in the problem statements. Extra process and device parameters are attached at the end of the exam.

- Here are some additional parameters in case you need them:  $\mu_n C_{OX}=300\mu A/V^2$ ,  $\mu_p C_{OX}=100\mu A/V^2$ ,  $V_{TNO}=0.5V$ ,  $V_{TPO}=-0.5V$ ,  $C_{OX}=8fF/\mu^2$ , no Vds effect ( $\lambda=0$ ), diode  $J_S=10^{-17}A/\mu^2$ , k/q=8.61E-5 V/K, kT/q=26mV.

- If you need any other parameters, clearly make an assumption and proceed.

- 1. Use two words (phrases) to briefly answer the following questions: (2 pts each)

- a. Name the largest chip fabrication foundry in the world, and give the main reason why we focus on it.

- b. Name the largest two semiconductor companies in the world.

- c. Name one famous CEO who graduated from ISU and the corresponding large semiconductor company.

- d. State why a barrier metal layer is used when creating copper interconnects, and reason why copper is better than aluminum.

- e. Name two drawbacks of Pass Transistor Logic.

- 2. Circle the best choice or draw the best matches. (3 pts each)

- a. On a given wafer, as the die area increase, match parameter and the trend:

- Die area cost

a) constant as area increase

Add

Neither

- Defect density

- b) increase linearly as area increase

- Yield of good die c) increase exponentially • Cost of good die

- d) decrease exponentially

- b. Circle the most important goal when designing a chip product:

- Smaller die area

- Higher yield

- Better performance

- Selling more chips

- Other:

- c. A chip has 5 components, each has 10% chance being bad. The chance the whole chip is bad is close to: a) 10%, b) 40%, c) 50%, d) 60%, e)90%

- d. Match each process step with how they add or subtract materials:

- Photolithography

- Etching

- Chemical vapor deposition Subtract

- Oxidation

- Chemical mechanical polishing (CMP)

- e. Rank the following layers in conductivity from highest (1) to lowest (5):

- Poly\_\_\_\_, Substrate\_\_\_\_, Top metal\_\_\_\_, N-well\_\_\_\_, Metal 1\_\_\_\_

3. (15 pts) Layout a minimum sized 400K $\Omega$  resistor in a 0.25 $\mu$  CMOS process. It has a High Resistivity Poly which has R $\equiv$ =1000 $\Omega$ . Assume the minimum width of HR Poly is 4 $\lambda$  and the minimum spacing is 2 $\lambda$ . Use metal layers to connect between poly strips. Minimum metal width is 4 $\lambda$ . Ignore metal resistance. The total resistor area should have rectangular shape with aspect ratio close to 1:2.

4. (15 pts) For the previous resistor, what is the total layout area? What is the poly resistor area? Suppose the foundry provides random variation A numbers,  $A_{\Delta R/R}=2\% \mu m$ . What is the  $\sigma$  value of  $\Delta R/R$ ? If we need the  $3\sigma$  to be  $\leq 0.1\%$  to achieve our yield target, how should we modify our design?

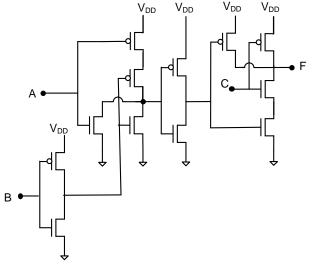

- 5. (15 pts) The transistor level implementation of a logic block with inputs A, B, and C and an output F is shown below.

- a. Given a Boolean expression for F in terms of the inputs A, B, and C.

- b. Implement the same Boolean function using the compound gate logic approach at the transistor level. Assume the inputs that are available are A, B, and C.

6. (15 pts) Assume 300mm wafers after processing cost \$3140 per wafer. If the defect density on these wafers is  $1.1/\text{cm}^2$ , determine the cost per good die if the die is square with a side dimension of 3 mm. Assume the soft yield is 100%. Use  $e^{\epsilon} \approx 1+\epsilon$ .

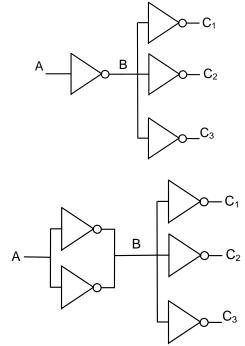

- 7. (15 pts) Two circuits are shown below that ideally implement the same Boolean function. Though the lower circuit has the outputs of two inverters that are tied together, since the inputs are the same, this is an allowed and actually widely used circuit. Assume the Boolean logic levels for these circuits are 0V and 5V and all transistors are minimum sized. Specify the model you use for the inverters when solving this problem.

- a) If the input A changes from  $V_{DD}$  to 0 at time t=0, the output B will subsequently change from low to high. Determine the time it takes for the B output to change states for the upper circuit.

- b) Repeat part a) for the lower circuit.

## MOSIS WAFER ACCEPTANCE TESTS

| RUN: T4BK (MM_NON-EPI_THK-MTL) | VENDOR: | TSMC  |              |

|--------------------------------|---------|-------|--------------|

| TECHNOLOGY: SCN018             | FEATURE | SIZE: | 0.18 microns |

INTRODUCTION: This report contains the lot average results obtained by MOSIS from measurements of MOSIS test structures on each wafer of this fabrication lot. SPICE parameters obtained from similar measurements on a selected wafer are also attached.

COMMENTS: DSCN6M018\_TSMC

| TRANSISTOR PARAMETERS               | W/L       | N-CHANNEL P-CHANNEL  |                        | UNITS                   |  |

|-------------------------------------|-----------|----------------------|------------------------|-------------------------|--|

| MINIMUM<br>Vth                      | 0.27/0.18 | 0.50                 | -0.53                  | volts                   |  |

| SHORT<br>Idss<br>Vth<br>Vpt         | 20.0/0.18 | 571<br>0.51<br>4.7   | -266<br>-0.53<br>-5.5  | uA/um<br>volts<br>volts |  |

| WIDE<br>Ids0                        | 20.0/0.18 | 22.0                 | -5.6                   | pA/um                   |  |

| LARGE<br>Vth<br>Vjbkd<br>Ijlk       | 50/50     | 0.42<br>3.1<br><50.0 | -0.41<br>-4.1<br><50.0 | volts<br>volts<br>pA    |  |

| K' (Uo*Cox/2)<br>Low-field Mobility |           | 171.8<br>398.02      | -36.3<br>84.10         | uA/V^2<br>cm^2/V*s      |  |

COMMENTS: Poly bias varies with design technology. To account for mask bias use the appropriate value for the parameters XL and XW in your SPICE model card.

| in your br                                                                             |                                    | gn Tecl                  |                    | XL                                       | (um)                | XW (um)             |                    |                                |

|----------------------------------------------------------------------------------------|------------------------------------|--------------------------|--------------------|------------------------------------------|---------------------|---------------------|--------------------|--------------------------------|

|                                                                                        |                                    | —                        | thi<br>(lambd      | a=0.09)<br>ck oxid<br>a=0.10)<br>ck oxid | le                  | 0.0<br>0.0<br>-0.0  | 02                 | -0.01<br>-0.01<br>0.00<br>0.00 |

| FOX TRANSISTORS<br>Vth                                                                 | -                                  | ATE<br>oly               | -                  | TIVE E<br>6.6                            | P+ACTIVE<br><-6.6   | UNITS<br>volts      |                    |                                |

| PROCESS PARAMETERS<br>Sheet Resistance<br>Contact Resistance<br>Gate Oxide Thickness   | <sup>N+</sup><br>6.6<br>10.1<br>40 | ₽+<br>7.5<br>10.6        | POLY<br>7.7<br>9.3 | N+BLK<br>61.0                            | PLY+BLK<br>317.1    | м1<br>0.08          | м2<br>0.08<br>4.18 | - ··· 1                        |

| PROCESS PARAMETERS<br>Sheet Resistance<br>Contact Resistance<br>COMMENTS: BLK is silie | M3<br>0.08<br>8.97<br>cide b       | POLY_H<br>991.5<br>lock. |                    | м4<br>0.08<br>14.09                      | м5<br>0.08<br>18.84 | м6<br>0.01<br>21.44 | N_W<br>941         | UNITS<br>ohms/sq<br>ohms       |

## CAPACITANCE PARAMETERS

| N+                                  | P+ 1 | POLY | M1 | M2 | M3   | M4 | M5 | M6 | R_W | D_N_W | M5P  | N_W | UNITS              |

|-------------------------------------|------|------|----|----|------|----|----|----|-----|-------|------|-----|--------------------|

| Area (substrate) 998                | 1152 | 103  | 39 | 19 | 13   | 9  | 8  | 3  |     | 129   |      | 127 | aF/um^2            |

| Area (N+active)                     |      | 8566 | 54 | 21 | 14   | 11 | 10 | 9  |     |       |      |     | aF/um^2            |

| Area (P+active)                     |      | 8324 |    |    |      |    |    |    |     |       |      |     | aF/um^2            |

| Area (poly)                         |      |      | 64 | 18 | 10   | 7  | 6  | 5  |     |       |      |     | aF/um^2            |

| Area (metal1)                       |      |      |    | 44 | 16   | 10 | 7  | 5  |     |       |      |     | aF/um^2            |

| Area (metal2)                       |      |      |    |    | 38   | 15 | 9  | 7  |     |       |      |     | aF/um^2            |

| Area (metal3)                       |      |      |    |    |      | 40 | 15 | 9  |     |       |      |     | aF/um^2            |

| Area (metal4)                       |      |      |    |    |      |    | 37 | 14 |     |       | 4000 |     | aF/um^2            |

| Area (metal5)                       |      |      |    |    |      |    |    | 36 |     |       | 1003 |     | aF/um^2            |

| Area (r well) 987                   |      |      |    |    |      |    |    |    | 574 |       |      |     | aF/um^2<br>aF/um^2 |

| Area (d well)<br>Area (no well) 139 |      |      |    |    |      |    |    |    | 574 |       |      |     | aF/um <sup>2</sup> |

| Fringe (substrate) 244              | 201  |      | 18 | 61 | 55   | 43 | 25 |    |     |       |      |     | aF/um              |

| Fringe (poly)                       | 201  |      | 69 | 39 | 29   | 24 | -  | 19 |     |       |      |     | aF/um              |

| Fringe (metal1)                     |      |      |    | 61 | 35   |    | 23 | -  |     |       |      |     | aF/um              |

| Fringe (metal2)                     |      |      |    |    | 54   | 37 | 27 | 24 |     |       |      |     | aF/um              |

| Fringe (metal3)                     |      |      |    |    |      | 56 | 34 | 31 |     |       |      |     | aF/um              |

| Fringe (metal4)                     |      |      |    |    |      |    | 58 | 40 |     |       |      |     | aF/um              |

| Fringe (metal5)                     |      |      |    |    |      |    |    | 61 |     |       |      |     | aF/um              |

| Overlap (P+active)                  |      | 652  |    |    |      |    |    |    |     |       |      |     | aF/um              |

|                                     |      |      |    |    |      |    |    |    |     |       |      |     |                    |

| CIRCUIT PARAMET                     | EBS  |      |    | 11 | NITS |    |    |    |     |       |      |     |                    |

| Inverters                           | K    |      |    | 0  |      |    |    |    |     |       |      |     |                    |

|                                     | IX . |      |    |    |      |    |    |    |     |       |      |     |                    |

| Inverters             | ĸ         |        |             |  |  |  |

|-----------------------|-----------|--------|-------------|--|--|--|

| Vinv                  | 1.0       | 0.74   | volts       |  |  |  |

| Vinv                  | 1.5       | 0.78   | volts       |  |  |  |

| Vol (100 uA)          | 2.0       | 0.08   | volts       |  |  |  |

| Voh (100 uA)          | 2.0       | 1.63   | volts       |  |  |  |

| Vinv                  | 2.0       | 0.82   | volts       |  |  |  |

| Gain                  | 2.0       | -23.33 |             |  |  |  |

| Ring Oscillator Fre   | eq.       |        |             |  |  |  |

| D1024_THK (31-9       | stg,3.3V) | 338.22 | MHz         |  |  |  |

| DIV1024 (31-stg,      | 1.8V)     | 402.84 | MHz         |  |  |  |

| Ring Oscillator Power |           |        |             |  |  |  |

| D1024_THK (31-9       | stg,3.3V) | 0.07   | uW/MHz/gate |  |  |  |

| DIV1024 (31-stg,      | 1.8V)     | 0.02   | uW/MHz/gate |  |  |  |

|                       |           |        |             |  |  |  |

COMMENTS: DEEP\_SUBMICRON