#### EE 330 Lecture 11

#### Capacitances in Interconnects Back-end Processing

#### Capacitance in Interconnects

$$C = C_D A$$

$C_D$  is the capacitance density and A is the area of the overlap

#### Capacitance in Interconnects

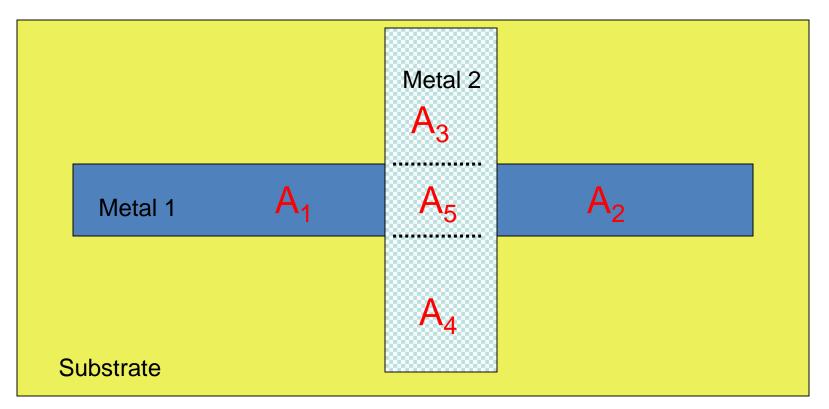

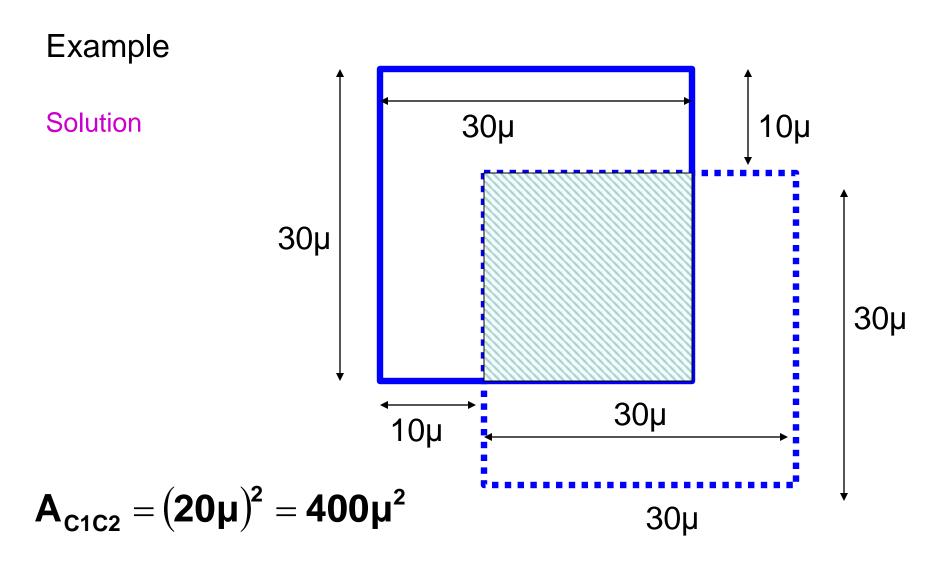

**Equivalent Circuit**

$$C_{12} = C_{D12} A_5$$

$$C_{1S} = C_{D1S} (A_1 + A_2 + A_5)$$

$$C_{2S} = C_{D2S} (A_3 + A_4)$$

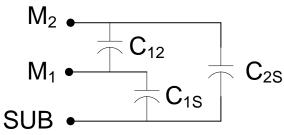

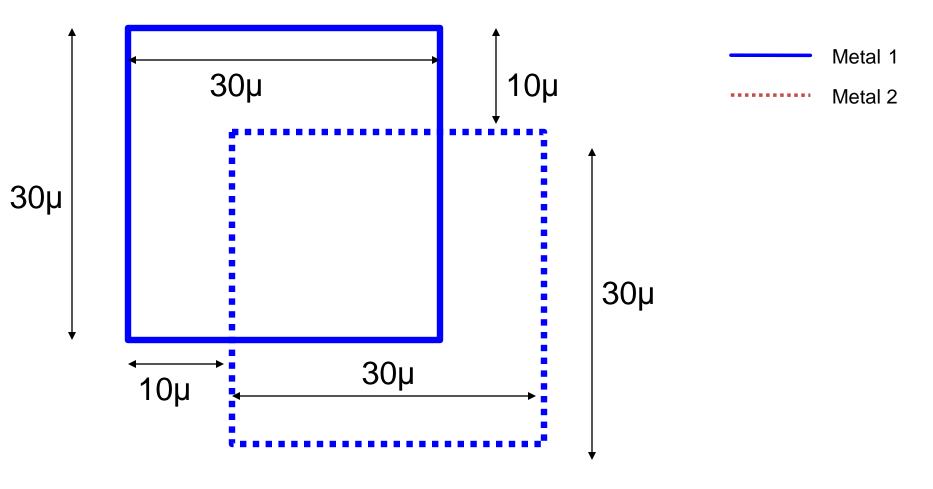

#### Example

Two metal layers, Metal 1 and Metal 2, are shown. Both are above field oxide. Determine the capacitance between Metal 1 and Metal 2. Assume the process has capacitance densities from  $M_1$  to substrate of .05fF/u<sup>2</sup>, from  $M_1$  to  $M_2$  of .07fF/u<sup>2</sup> and from  $M_2$  to substrate of .025fF/u<sup>2</sup>.

The capacitance density from  $M_1$  to  $M_2$  is .07fF/u<sup>2</sup>

$C_{12} = A_{C1C2} \bullet C_{D12} = 400 \mu^2 \bullet 0.07 \text{fF}/\mu^2 = 28 \text{fF}$

# Capacitance and Resistance in Interconnects

See MOSIS WEB site for process parameters that characterize parasitic resistances and capacitances

www.mosis.org

| RUN: T4BK (MM_NON-EPI_THK-MTL) | VENDOR: TSMC               |

|--------------------------------|----------------------------|

| TECHNOLOGY: SCN018             | FEATURE SIZE: 0.18 microns |

INTRODUCTION: This report contains the lot average results obtained by MOSIS from measurements of MOSIS test structures on each wafer of this fabrication lot. SPICE parameters obtained from similar measurements on a selected wafer are also attached.

COMMENTS: DSCN6M018\_TSMC

| TRANSISTOR PARAMETERS | S W/L     | N-CHANNEL | P-CHANNEL | UNITS    |

|-----------------------|-----------|-----------|-----------|----------|

| MINIMUM<br>Vth        | 0.27/0.18 | 0.50      | -0.53     | volts    |

| vin                   |           | 0.50      | -0.55     | VOILS    |

| SHORT                 | 20.0/0.18 |           |           |          |

| Idss                  |           | 571       | -266      | uA/um    |

| Vth                   |           | 0.51      | -0.53     | volts    |

| Vpt                   |           | 4.7       | -5.5      | volts    |

| WIDE                  | 20.0/0.18 |           |           |          |

| Ids0                  |           | 22.0      | -5.6      | pA/um    |

| LARGE                 | 50/50     |           |           |          |

| Vth                   |           | 0.42      | -0.41     | volts    |

| Vjbkd                 |           | 3.1       | -4.1      | volts    |

| Ijlk                  |           | <50.0     | <50.0     | рА       |

| K' (Uo*Cox/2)         |           | 171.8     | -36.3     | uA/V^2   |

| Low-field Mobility    |           | 398.02    | 84.10     | cm^2/V*s |

COMMENTS: Poly bias varies with design technology. To account for mask bias use the appropriate value for the parameters XL and XW in vour SPICE model card.

| FOX TRANSISTORS | GATE | N+ACTIVE | P+ACTIVE | UNITS |

|-----------------|------|----------|----------|-------|

| Vth             | Poly | >6.6     | <-6.6    | volts |

| PROCESS PARAMETERS<br>Sheet Resistance<br>Contact Resistance                                                                                                                                                                                                                                                                                                                                      | N+<br>6.6<br>10.1            |                   |                             | 7                    | N+E<br>61                        | 3LK<br>L.Ø                                   |                                                  | Y+B<br>17.                                                       |                                                     | M1<br>0.0         | 8 0.         | 08 o    | NITS<br>hms/so<br>hms | 7                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------|-----------------------------|----------------------|----------------------------------|----------------------------------------------|--------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------|-------------------|--------------|---------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROCESS PARAMETERS<br>Sheet Resistance<br>Contact Resistance<br>COMMENTS: BLK is silicit                                                                                                                                                                                                                                                                                                          | M3<br>0.08<br>8.97<br>de blo | 99                | /_HRI<br>91.5               |                      | M4<br>0.0<br>4.0                 | 8                                            | 0                                                | M5<br>.08<br>.84                                                 |                                                     | M6<br>0.0<br>21.4 | 1 9          | W<br>41 | UNIT<br>ohms<br>ohms  | /sq                                                                                                                                                                                             |

| CAPACITANCE PARAMETERS<br>Area (substrate)<br>Area (N+active)<br>Area (P+active)<br>Area (poly)<br>Area (metal1)<br>Area (metal2)<br>Area (metal3)<br>Area (metal4)<br>Area (metal4)<br>Area (metal5)<br>Area (r well)<br>Area (d well)<br>Area (no well)<br>Fringe (substrate)<br>Fringe (metal1)<br>Fringe (metal2)<br>Fringe (metal3)<br>Fringe (metal3)<br>Fringe (metal4)<br>Fringe (metal5) |                              | P+<br>1152<br>201 | POLY<br>103<br>8566<br>8324 | 39<br>54<br>64<br>18 | 19<br>21<br>18<br>44<br>61<br>39 | 13<br>14<br>10<br>16<br>38<br>55<br>29<br>35 | 9<br>11<br>7<br>10<br>15<br>40<br>43<br>24<br>37 | 8<br>10<br>6<br>7<br>9<br>15<br>37<br>25<br>21<br>23<br>27<br>34 | 3<br>9<br>5<br>7<br>9<br>14<br>36<br>19<br>21<br>24 | R_W               | D_N_W<br>129 |         | N_W<br>127            | UNITS<br>aF/um^2<br>aF/um^2<br>aF/um^2<br>aF/um^2<br>aF/um^2<br>aF/um^2<br>aF/um^2<br>aF/um^2<br>aF/um^2<br>aF/um^2<br>aF/um^2<br>aF/um^2<br>aF/um<br>aF/um<br>aF/um<br>aF/um<br>aF/um<br>aF/um |

| Overlap (P+active)                                                                                                                                                                                                                                                                                                                                                                                |                              |                   | 652                         |                      |                                  |                                              |                                                  |                                                                  |                                                     |                   |              |         |                       | aF/um                                                                                                                                                                                           |

T4BK SPICE BSIM3 VERSION 3.1 PARAMETERS SPICE 3f5 Level 8, Star-HSPICE Level 49, UTMOST Level 8 \* DATE: Jan 21/05 \* LOT: T4BK WAF: 3004 \* Temperature parameters=Default .MODEL CMOSN NMOS ( LEVEL = 49 +VERSION = 3.1TNOM = 27 TOX = 4E - 9+XJ = 1E-7NCH = 2.3549E17 VTH0 = 0.3662648 +K1 = 0.5802748 K2 = 3.124029E-3K3 = 1E - 3+K3B = 3.3886871WØ = 1E-7NLX = 1.766159E-7+DVTØW = 0 DVT1W = 0 DVT2W = 0 +DVT0 = 1.2312416 DVT1 = 0.3849841DVT2 = 0.0161351 +U0 = 265.1889031= -1.506402E-9UB = 2.489393E - 18UA +UC = 5.621884E - 11VSAT = 1.017932E5A0 = 2 +AGS = 0.4543117 BØ = 3.433489E-7B1 = 5E-6+KETA = -0.0127714A1 = 1.158074E-3A2 = 1 +RDSW = 136.5582806 PRWG = 0.5 PRWB = -0.2= 0 +WR = 1 WINT LINT = 1.702415E-8+XL = 0 XW = -1E - 8DWG = -4.211574E-9= 1.107719E-8 +DWB VOFF = -0.0948017 NFACTOR = 2.1860065+CIT = 0 CDSC = 2.4E-4CDSCD = 0 ETAB +CDSCB = 0 ETA0 = 3.335516E-3 = 6.028975E-5+DSUB PCLM = 0.0214781 = 0.6602119 PDIBLC1 = 0.1605325+PDIBLC2 = 3.287142E-3 PDIBLCB = -0.1DROUT = 0.7917811 PSCBE2 = 4.122516E-9 +PSCBE1 = 6.420235E9PVAG = 0.0347169 +DELTA RSH = 6.6 MOBMOD = 1= 0.01 +PRT UTE KT1 = -0.11= 0 = -1.5 +KT1L KT2 = 0.022 UA1 = 4.31E-9= 0 +UB1 = -7.61E - 18UC1 = -5.6E - 11AT = 3.3E4+WL = 0 WLN = 1 = 0 WW = 1 = 0 LL = 0 +WWN WWL +LLN = 1 LW = 0 LWN = 1 = 0 XPART = 0.5 +LWL CAPMOD = 2+CGDO = 8.06E-10 CGSO = 8.06E - 10CGBO = 1E - 12+CJ = 9.895609E-4 PB = 0.8 MJ = 0.3736889 +CJSW = 2.393608E-10 PBSW MJSW = 0.1537892 = 0.8 +CJSWG = 3.3E - 10PBSWG = 0.8 MJSWG = 0.1537892 +CF = 0 **PVTHØ** PRDSW = -1.73163E-3= -1.4173554 +PK2 = 1.600729E-3WKETA = -3.255127E-3= 1.601517E-3 LKETA +PU0 = 5.2024473 PUA = 1.584315E-12PUB = 7.446142E-25+PVSAT = 1.686297E3 PETAØ PKETA = 1.001594E-4= -2.039532E-3

)

\*

| .MODEL CMOSP PMOS (                     |                                           | LEVEL = 49            |

|-----------------------------------------|-------------------------------------------|-----------------------|

| +VERSION = 3.1                          | TNOM = 27                                 | TOX = 4E-9            |

| +XJ = 1E-7                              | NCH = 4.1589E17                           | VTH0 = -0.3708038     |

| +K1 = 0.5895473                         | K2 = 0.0235946                            | K3 = 0                |

| +K3B = 13.8642028                       | W0 = 1E-6                                 | NLX = 1.517201E-7     |

| +DVT0W = 0                              | DVT1W = 0                                 | DVT2W = 0             |

| +DVT0 = 0.7885088                       | DVT1 = 0.2564577                          | DVT2 = 0.1            |

| +U0 = 103.0478426                       | UA = 1.049312E-9                          | UB = 2.545758E-21     |

| +UC = -1E - 10                          | VSAT = 1.645114E5                         | A0 = 1.627879         |

| +AGS = 0.3295499                        | B0 = 5.207699E-7                          | B1 = 1.370868E-6      |

| +KETA = 0.0296157                       | A1 = 0.4449009                            | A2 = 0.3              |

| +RDSW = 306.5789827                     | PRWG = 0.5                                | PRWB = 0.5            |

| +WR = 1                                 | WINT = Ø                                  | LINT = 2.761033E-8    |

| +XL = 0                                 | XW = -1E-8                                | DWG = -2.433889E-8    |

| +DWB = -9.34648E-11                     | VOFF = -0.0867009                         | NFACTOR = $2$         |

| +CIT = 0                                | CDSC = 2.4E-4                             | CDSCD = 0             |

| +CDSCB = 0                              | ETA0 = 1.018318E-3                        | ETAB = -3.206319E-4   |

| +DSUB = 1.094521E-3                     | PCLM = 1.3281073                          | PDIBLC1 = 2.394169E-3 |

| +PDIBLC2 = -3.255915E-6                 |                                           | DROUT = 0             |

| +PSCBE1 = 4.881933E10                   | PSCBE2 = 5E-10                            | PVAG = 2.0932623      |

| +DELTA = 0.01                           | RSH = 7.5                                 | MOBMOD = 1            |

| +PRT = 0                                | UTE = -1.5                                | KT1 = -0.11           |

| +KT1L = 0                               | KT2 = 0.022                               | UA1 = 4.31E-9         |

| +UB1 = -7.61E-18                        | UC1 = -5.6E-11                            | AT = 3.3E4            |

| +WL = 0                                 | WLN = 1                                   | WW = 0                |

| +WWN = 1                                | WUL = 0                                   | LL = 0                |

| +LLN = 1                                | LW = 0                                    | LWN = 1               |

| +LWL = 0                                | CAPMOD = 2                                | XPART = 0.5           |

| +CGDO = 6.52E-10                        | CGS0 = 6.52E-10                           | CGBO = 1E-12          |

| +CJ = 1.157423E-3                       | PB = 0.8444261                            | MJ = 0.4063933        |

| +CJSW = 1.902456E-10                    |                                           | MJSW = 0.3550788      |

| +CJSWG = 4.22E-10                       | PBSWG = 0.8                               | MJSWG = 0.3550788     |

| +CF = 0                                 | PVTH0 = 1.4398E-3                         | PRDSW = 0.5073407     |

| +PK2 = 0<br>+PK2 = 2.190431E-3          | WKETA = 0.0442978                         | LKETA = -2.936093E-3  |

| +PKZ = 2.190451E-5<br>+PU0 = -0.9769623 | PUA = -4.34529E-11                        |                       |

| +PU0 = -0.9769623<br>+PVSAT = -50       | PUA = -4.34529E-11<br>PETA0 = 1.002762E-4 |                       |

| +PVSAT = -50<br>*                       | PETAU = 1.002/02E-4                       | PRETA = -0.740430E-3  |

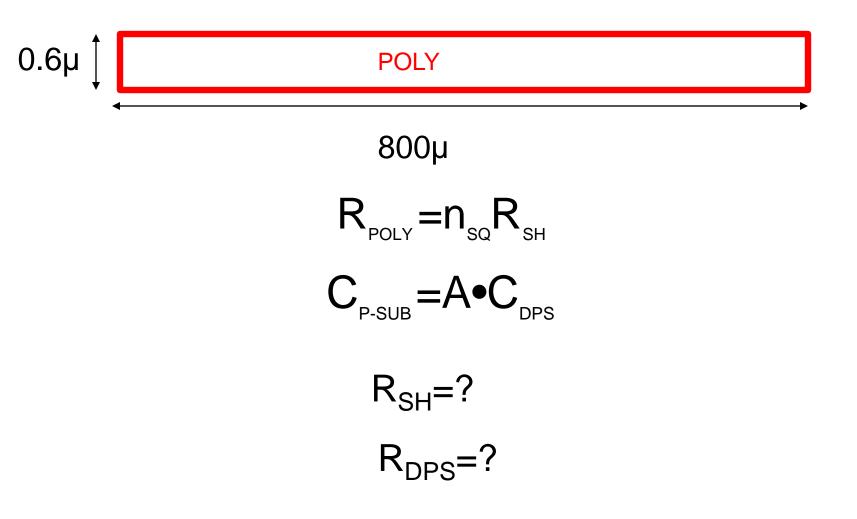

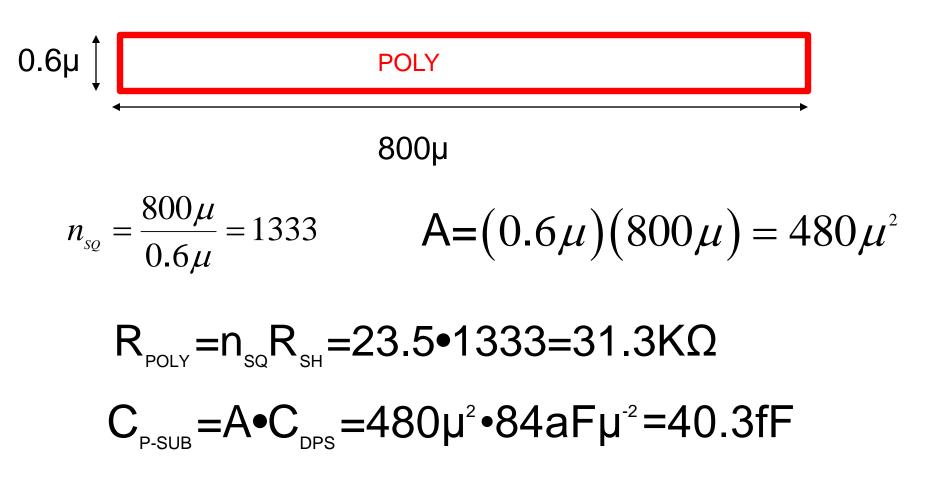

#### Example

Determine the resistance and capacitance of a Poly interconnect that is 0.6u wide and 800u long and compare that with the same interconnect if  $M_1$  were used. Assume a 0.18u process.

#### For 0.18u process

| PROCESS PARAMETERS<br>Sheet Resistance<br>Contact Resistance | N+<br>6.0<br>10.1 |      | .5 7. | $\overline{\mathbf{v}}$ | N+E<br>61 | BLK<br>L.Ø |     | Y+B<br>17. |    | M1<br>0.0 |       | )8 6 | hms/    |                      | 7Ω/□ |

|--------------------------------------------------------------|-------------------|------|-------|-------------------------|-----------|------------|-----|------------|----|-----------|-------|------|---------|----------------------|------|

| PROCESS PARAMETERS                                           | MЗ                | POL  | Y_HRI |                         | M4        |            | - 1 | 45         |    | M6        | N_1   | V    | UNI     | ••••                 |      |

| Sheet Resistance                                             | 0.08              | 99   | 91.5  |                         | 0.0       | 8          | 0   | .08        |    | 0.0       | 1 94  | 11   | ohm     | is/sq                |      |

| Contact Resistance                                           | 8.97              |      |       | 1                       | 4.0       | 9          | 18  | .84        |    | 21.44     | 4     |      | ohm     | IS                   |      |

| COMMENTS: BLK is silici                                      | de blo            | ck.  |       |                         |           |            |     |            |    |           |       |      | $C_{D}$ | <sub>PS</sub> =103 a | ſ∕µ² |

| CAPACITANCE PARAMETERS                                       | 5 N+              | P+   | POLY  |                         | M2        | ΜЗ         |     |            | M6 | R_W       | D_N_W | M5P  | N_W     |                      |      |

| Area (substrate)                                             | 998               | 1152 | 103   | 39                      | 19        | 13         | 9   | 8          | 3  |           | 129   |      | 12      | 7 aF/um^2            | )    |

| Area (N+active)                                              |                   |      | 8566  | 54                      | 21        | 14         | 11  | 10         | 9  |           |       |      |         | aF/um^2              |      |

| Area (P+active)                                              |                   |      | 8324  |                         |           |            |     |            |    |           |       |      |         | aF/um^2              |      |

| Area (poly)                                                  |                   |      |       | 64                      | 18        |            |     | 6          | 5  |           |       |      |         | aF/um^2              |      |

| Area (metal1)                                                |                   |      |       |                         | 44        | 16         |     | 7          | 5  |           |       |      |         | aF/um^2              |      |

| Area (metal2)                                                |                   |      |       |                         |           | 38         | 15  | 9          | 7  |           |       |      |         | aF/um^2              |      |

| Area (metal3)                                                |                   |      |       |                         |           |            | 40  |            | 9  |           |       |      |         | aF/um^2              |      |

| Area (metal4)                                                |                   |      |       |                         |           |            |     | 37         | 14 |           |       |      |         | aF/um^2              |      |

| Area (metal5)                                                |                   |      |       |                         |           |            |     |            | 36 |           |       | 1003 |         | aF/um^2              |      |

| Area (r well)                                                | 987               |      |       |                         |           |            |     |            |    |           |       |      |         | aF/um^2              |      |

| Area (d well)                                                |                   |      |       |                         |           |            |     |            |    | 574       |       |      |         | aF/um^2              |      |

| Area (no well)                                               | 139               |      |       |                         |           |            |     |            |    |           |       |      |         | aF/um^2              |      |

| Fringe (substrate)                                           | 244               | 201  |       | 18                      | 61        | 55         | 43  | 25         |    |           |       |      |         | aF/um                |      |

| Fringe (poly)                                                |                   |      |       | 69                      | 39        | 29         | 24  | 21         | 19 |           |       |      |         | aF/um                |      |

| Fringe (metal1)                                              |                   |      |       |                         | 61        | 35         |     | 23         | 21 |           |       |      |         | aF/um                |      |

| Fringe (metal2)                                              |                   |      |       |                         |           | 54         | 37  | 27         | 24 |           |       |      |         | aF/um                |      |

| Fringe (metal3)                                              |                   |      |       |                         |           |            | 56  | 34         | 31 |           |       |      |         | aF/um                |      |

| Fringe (metal4)                                              |                   |      |       |                         |           |            |     | 58         | 40 |           |       |      |         | aF/um                |      |

| Fringe (metal5)                                              |                   |      |       |                         |           |            |     |            | 61 |           |       |      |         | aF/um                |      |

| Overlap (P+active)                                           |                   |      | 652   |                         |           |            |     |            |    |           |       |      |         | aF/um                |      |

|                                                              |                   |      |       |                         |           |            |     |            |    |           |       |      |         |                      |      |

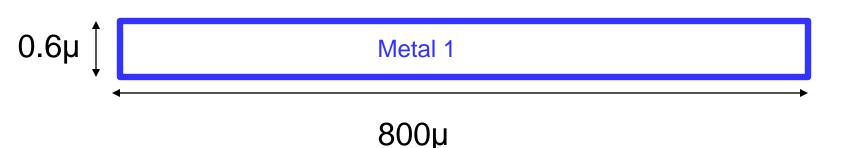

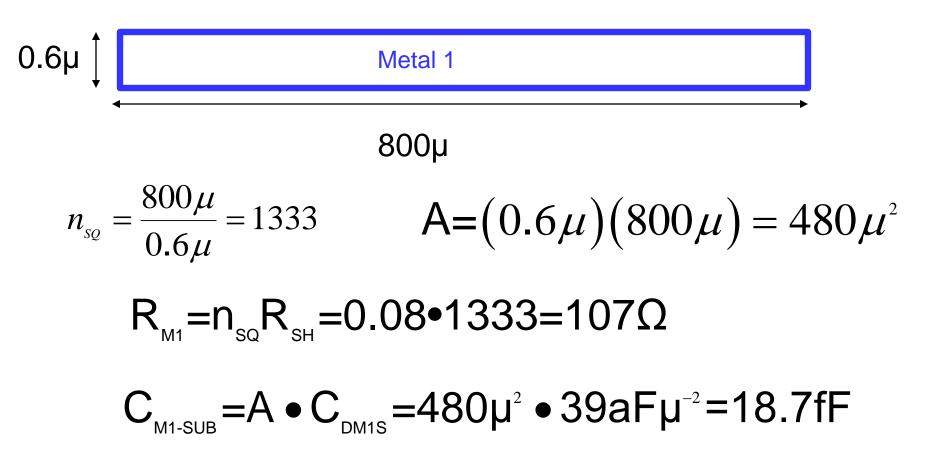

#### For 0.18u process

Example

Determine the resistance and capacitance of a Poly interconnect that is 0.6u wide and 800u long and compare that with the same interconnect if M<sub>1</sub> were used.

#### Example

Determine the resistance and capacitance of a Poly interconnect that is 0.6u wide and 800u long and compare that with the same interconnect if  $M_1$  were used.

#### For 0.18u process

| PROCESS PARAMETERS<br>Sheet Resistance<br>Contact Resistance                                                                                                                                                                                                                                                                                                                                   | 10.1 10                                      |                          | 61.0                                                                             | PLY+BLK<br>317.1                                                                    | M1 M2<br>0.08 0.08<br>4.18 | $hms$ R <sub>SH</sub> =0.08 $\Omega$ /                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROCESS PARAMETERS<br>Sheet Resistance<br>Contact Resistance                                                                                                                                                                                                                                                                                                                                   |                                              | Y_HRI<br>991.5           | M4<br>0.08<br>14.09                                                              | M5<br>0.08<br>18.84                                                                 | M6 N_W<br>0.01 94<br>21.44 |                                                                                                                                                                                                                                        |

| COMMENTS: BLK is silici                                                                                                                                                                                                                                                                                                                                                                        | ide block.                                   |                          |                                                                                  |                                                                                     |                            | C <sub>DPS</sub> =39 af/µ <sup>2</sup>                                                                                                                                                                                                 |

| CAPACITANCE PARAMETER<br>Area (substrate)<br>Area (N+active)<br>Area (P+active)<br>Area (poly)<br>Area (metal1)<br>Area (metal2)<br>Area (metal3)<br>Area (metal3)<br>Area (metal4)<br>Area (metal5)<br>Area (r well)<br>Area (d well)<br>Area (d well)<br>Area (no well)<br>Fringe (substrate)<br>Fringe (metal1)<br>Fringe (metal2)<br>Fringe (metal3)<br>Fringe (metal4)<br>Fringe (metal5) | S N+ P+<br>998 1152<br>987<br>139<br>244 201 | 103<br>8566<br>8324<br>6 | 39 19 13<br>54 21 14<br>54 18 10<br>44 16<br>38<br>18 61 55<br>59 39 29<br>61 35 | 11 10 9<br>7 6 5<br>10 7 5<br>15 9 7<br>40 15 9<br>37 14<br>36<br>43 25<br>24 21 19 | - <u>1</u> 29              | M5P N_W UNITS<br>127 aF/um^2<br>aF/um^2<br>aF/um^2<br>aF/um^2<br>aF/um^2<br>aF/um^2<br>aF/um^2<br>aF/um^2<br>aF/um^2<br>aF/um^2<br>aF/um^2<br>aF/um^2<br>aF/um<br>aF/um<br>aF/um<br>aF/um<br>aF/um<br>aF/um<br>aF/um<br>aF/um<br>aF/um |

| Overlap (P+active)                                                                                                                                                                                                                                                                                                                                                                             |                                              | 652                      |                                                                                  |                                                                                     |                            | aF/um                                                                                                                                                                                                                                  |

#### Example For 0.18u process

Determine the resistance and capacitance of a Poly interconnect that is 0.6u wide and 800u long and compare that with the same interconnect if  $M_1$  were used.

# IC Fabrication Technology

- Crystal Preparation

- Masking

- Photolithographic Process

- Deposition

- Etching

- Diffusion

- Ion Implantation

- Oxidation

- Epitaxy

- Polysilicon

- Contacts, Interconnect and Metalization

- 🔶 Planarization

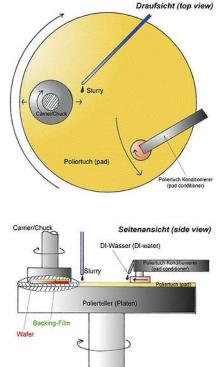

# Planarization

- Planarization used to keep surface planar during subsequent processing steps

- Important for creating good quality layers in subsequent processing steps

- Mechanically planarized

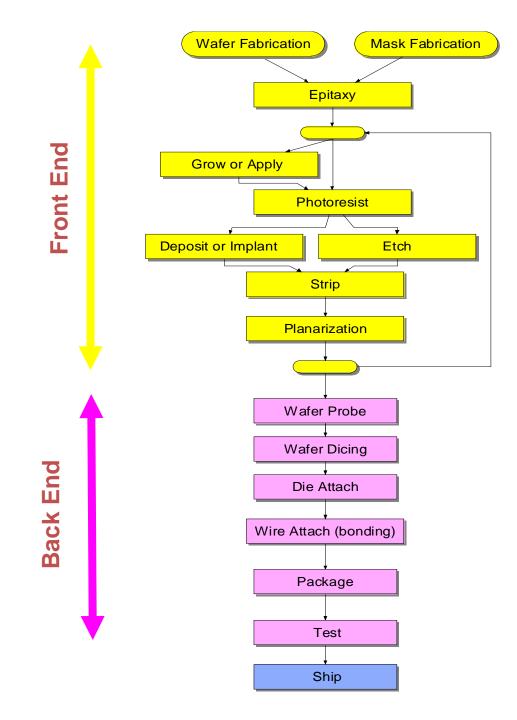

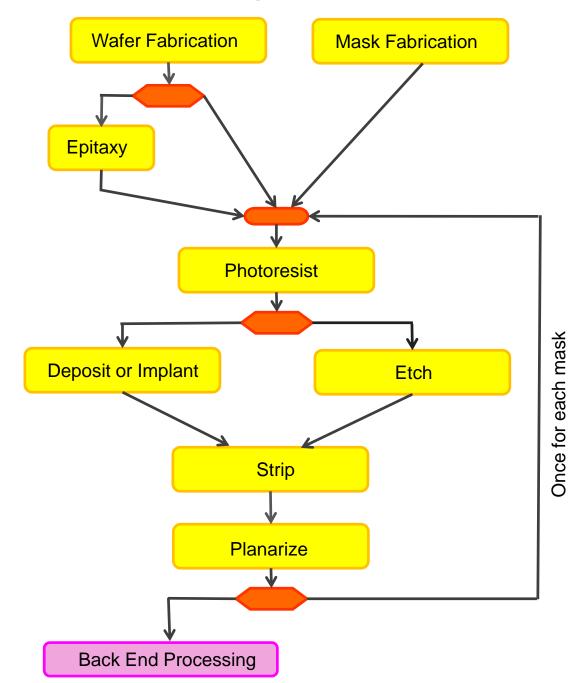

#### Generic Process Flow

#### **Front End Process Integration for Fabrication of ICs**

## Front-End Process Flow

- Front-end processing steps analogous to a "recipe" for manufacturing an integrated circuit

- Recipes vary from one process to the next but the same basic steps are used throughout the industry

- Details of the recipe are generally considered proprietary

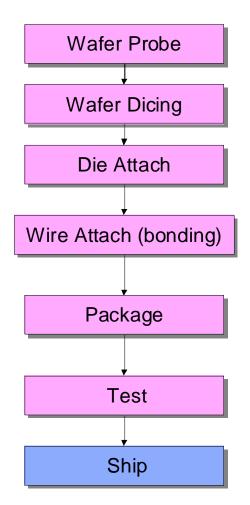

#### **Back-End Process Flow**

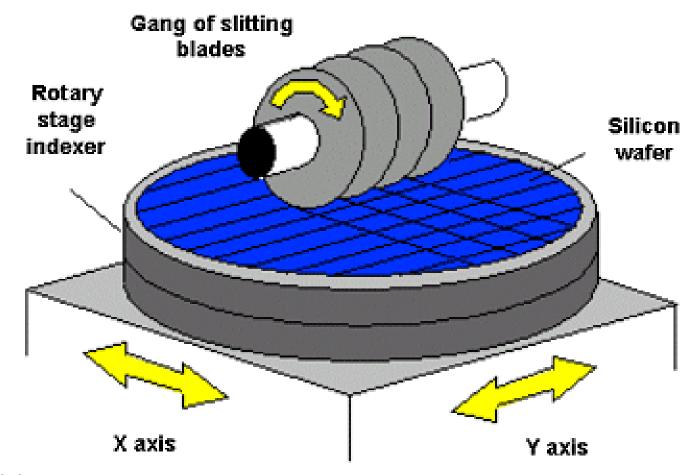

# Wafer Dicing

www.renishaw.com

# Die Attach

- 1. Eutectic

- 2. Pre-form

- 3. Conductive Epoxy

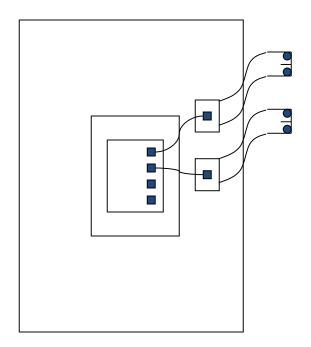

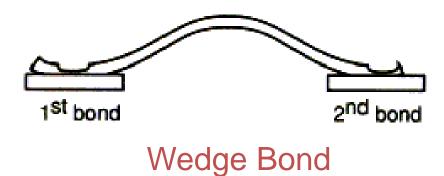

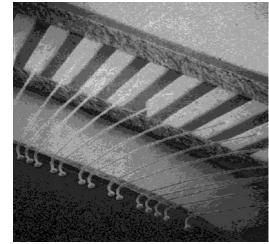

### **Electrical Connections (Bonding)**

- Wire Bonding

- Bump Bonding

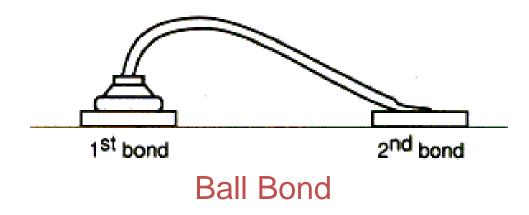

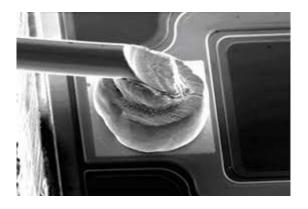

# Wire – gold or aluminum $25 \mu$ in diameter

Excellent Annimation showing process at :

http://www.kns.com/\_Flash/CAP\_BONDING\_CYCLE.swf

www.kns.com

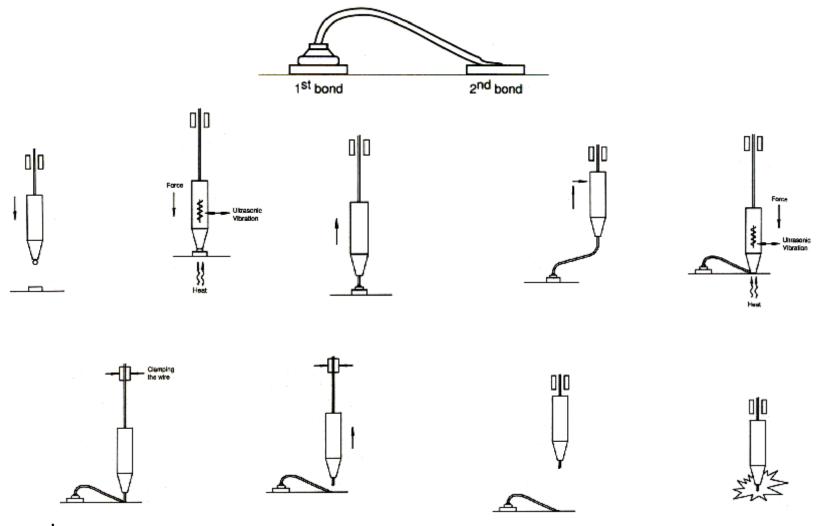

### **Ball Bonding Steps**

www.kns.com

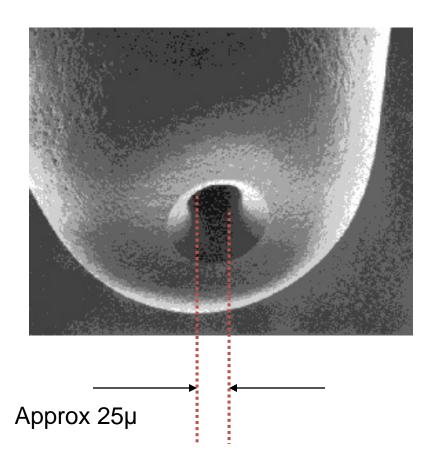

### **Ball Bonding Tip**

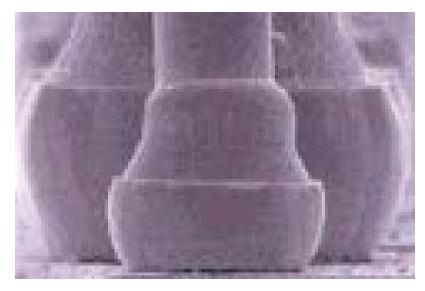

**Ball Bond**

#### **Termination Bond**

#### **Ball Bond Photograph**

## **Bump Bonding**

www.secap.org

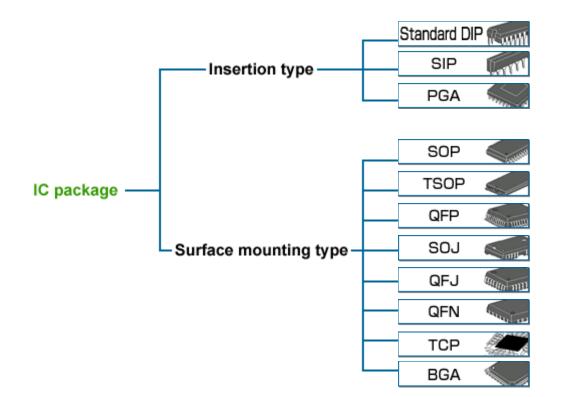

# Packaging

- 1. Many variants in packages now available

- 2. Considerable development ongoing on developing packaging technology

- 3. Cost can vary from few cents to tens of dollars

- 4. Must minimize product loss after packaged

- 5. Choice of package for a product is serious business

- 6. Designer invariably needs to know packaging plans and package models

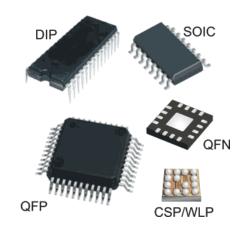

# Packaging

www.necel.com

# Packaging

www.necel.com

#### Pin Pitch Varies with Package Technology

#### All measurements are nominal in [mm].

| Name                   | Pin pitch | Size         | Height |

|------------------------|-----------|--------------|--------|

| DIP or DIL             | 2.54      |              |        |

| SOIC-16                | 1.27      | 3.9 x 10     | 1.72   |

| SSOP                   | 0.635     |              |        |

| TSSOP54-II             | 0.8       | 12.7 x 22.22 | ~1     |

| PLCC44                 | 1.27      |              |        |

| PQ208 <sup>[1]</sup>   | 0.50      | 28 x 28      | 3.4    |

| TQFP64                 | 0.40      | 7 x 7        | 1.0    |

| TQFP144 <sup>[2]</sup> | 0.50      | 20 x 20      | 1.0    |

| 128PQFP                | 0.50      | 23.23 x 14.0 | 3.15   |

http://www.electroiq.com/index/display/packaging-articledisplay/234467/articles/advanced-packaging/volume-14/issue-8/features/the-back-end-process/materials-andmethods-for-ic-package-assemblies.htm

#### From Wikipedia, Sept 20, 2010

http://en.wikipedia.org/wiki/List\_of\_chip\_carriers

### Many standard packages available today:

http://www.interfacebus.com/Design\_Pack\_types.html

BCC: Bump Chip Carrier BGA: Ball Grid Array; BGA graphic BOFP: Bumpered Quad Flat Pack CABGA/SSBGA: Chip Array/Small Scale Ball Grid Array CBGA: Ceramic Ball Grid Array CFP: Ceramic Flat Pack CPGA: Ceramic Pin Grid Array, CPGA Graphic CQFP: Ceramic Quad Flat Pack, CQFP Graphic TBD: Ceramic Lead-Less Chip Carrier DFN: Dual Flat Pack, No Lead **DLCC:** Dual Lead-Less Chip Carrier (Ceramic) ETOFP: Extra Thin Quad Flat Package FBGA: Fine-pitch Ball Grid Array fpBGA: Fine Pitch Ball Grid Array HSBGA: Heat Slug Ball Grid Array JLCC: J-Leaded Chip Carrier (Ceramic) J-Lead Picture LBGA: Low-Profile Ball Grid Array LCC: Leaded Chip Carrier LCC Graphic LCC: Leaded Chip Carrier Un-formed LCC Graphic LCCC: Leaded Ceramic Chip Carrier; LFBGA: Low-Profile, Fine-Pitch Ball Grid Array LGA: Land Grid Array, LGA uP [Pins are on the Motherboard, not the socket] LLCC: Leadless Leaded Chip Carrier LLCC Graphic LOFP: Low Profile Quad Flat Package MCMBGA: Multi Chip Module Ball Grid Array MCMCABGA: Multi Chip Module-Chip Array Ball Grid Array MLCC: Micro Lead-frame Chip Carrier

PBGA: Plastic Ball Grid Array PLCC: Plastic Leaded Chip Carrier PQFD: Plastic Quad Flat Pack PQFP: Plastic Quad Flat Pack PSOP: Plastic Small-Outline Package PSOP graphic **QFP:** Quad Flatpack **QFP** Graphics **QSOP:** Quarter Size Outline Package [Quarter Pitch Small Outline Package] SBGA: Super BGA - above 500 Pin count SOIC: Small Outline IC SO Flat Pack: Small Outline Flat Pack IC SOJ: Small-Outline Package [J-Lead]; J-Lead Picture SOP: Small-Outline Package; SOP IC, Socket SSOP: Shrink Small-Outline Package TBGA: Thin Ball Grid Array TOFP: Thin Quad Flat Pack TOFP Graphic **TSOP:** Thin Small-Outline Package **TSSOP:** Thin Shrink Small-Outline Package TVSOP: Thin Very Small-Outline Package VOFB: Very-thin Quad Flat Pack

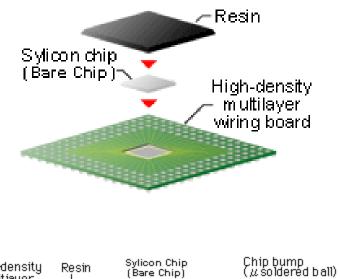

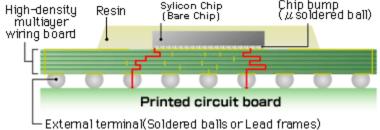

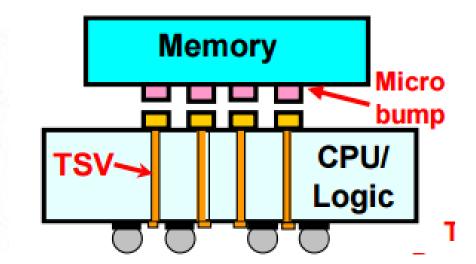

Considerable activity today and for years to come on improving packaging technology

- Multiple die in a package

- Three-dimensional chip stacking

- Multiple levels of interconnect in stacks

- Through silicon via technology

- Power and heat management

- Cost driven and cost constrained

The following few slides come from a John Lau presentation

Www.sematech.org/meetings/archives/symposia/10187/Session2/04\_Lau.pdf

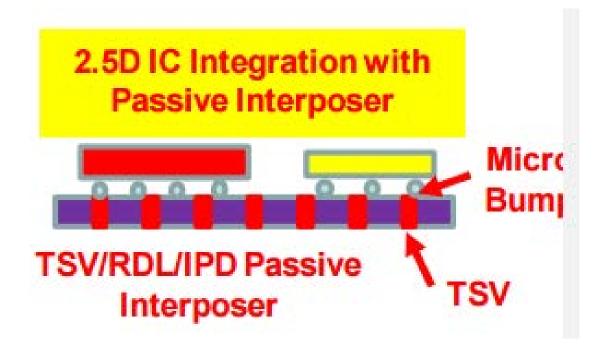

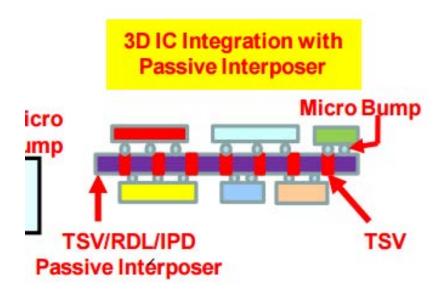

#### TSV Interposer: The Most Cost-Effective Integrator for 3D IC Integration

John H. Lau Electronics & Optoelectronics Research Laboratories Industrial Technology Research Institute (ITRI) Chutung, Hsinchu, Taiwan 310, R.O.C. <u>886-3591-3390, johnlau@itri.org.tw</u>

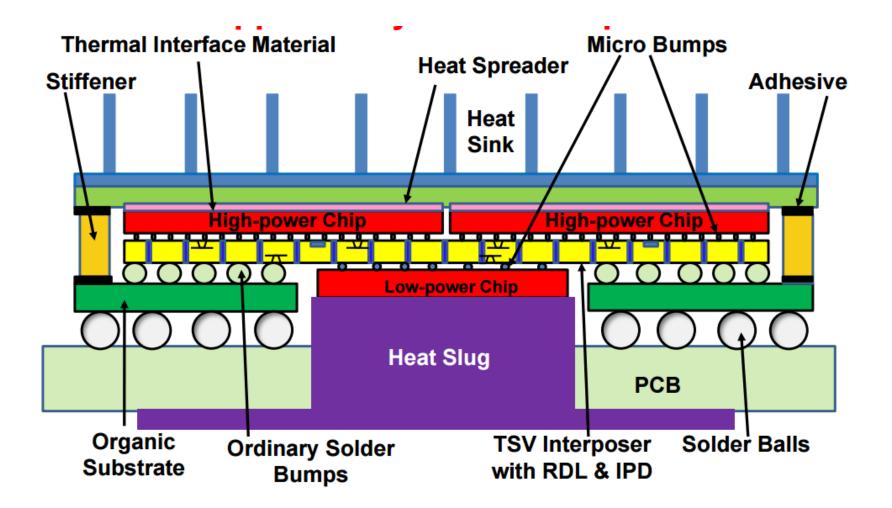

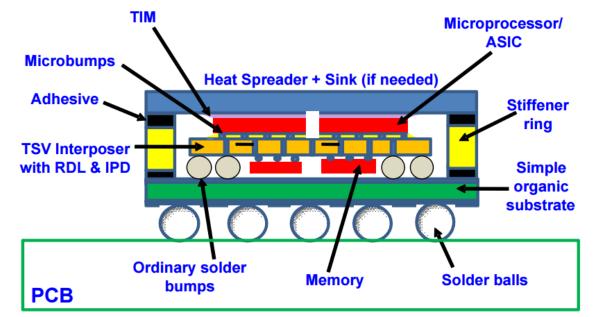

#### TSV passive interposer supporting high-power chips (e.g., microprocessor and logic) on its top side and low-power chips (e.g., memory) on its bottom side

Special underfills are needed between the Cu -filled interposer and all the chips. Ordinary underfills are needed between the interposer and the organic substrate.

```

ASME InterPACK2011-52189 (Lau)

```

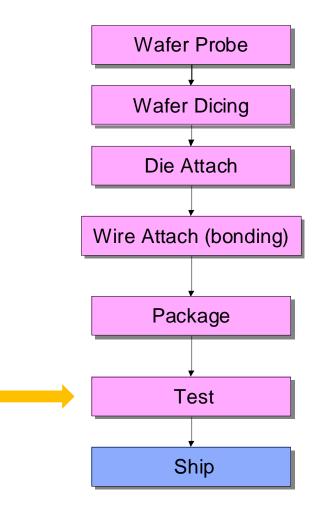

## **Back-End Process Flow**

## **Testing of Integrated Circuits**

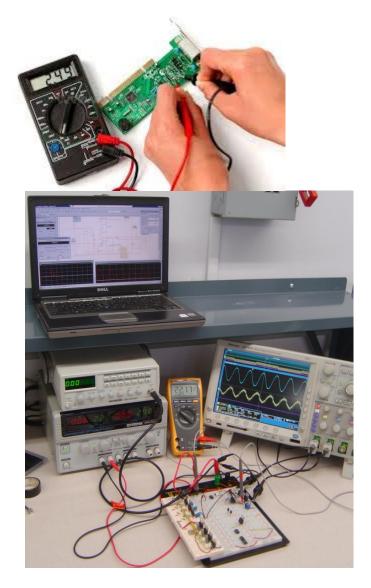

Bench testing used to qualify parts for production

Most integrated circuits are tested twice during production

- Wafer Probe Testing

- Quick test for functionality

- Usually does not include much parametric testing

- Relatively fast and low cost test

- Package costs often quite large

- Critical to avoid packaging defective parts

- Packaged Part Testing

- Testing costs for packaged parts can be high

- Extensive parametric tests done at package level for many parts

- Data sheet parametrics with Max and Min values are usually tested on all Ics

- Data sheet parametrics with Typ values are seldom tested

- Occasionally require testing at two or more temperatures but this is costly

- Critical to avoid packaging defective parts

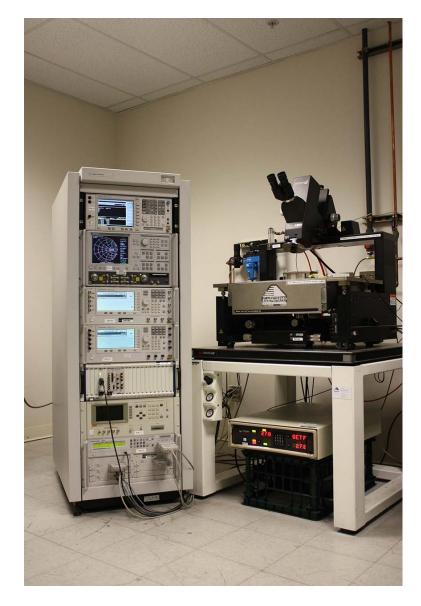

### **Bench Test Environment**

### **Bench Test Environment**

Photo courtesy of Texas Instruments

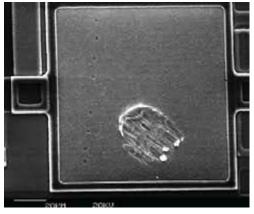

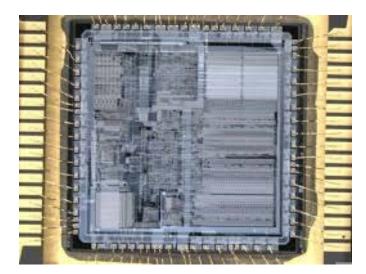

### Probe Test

Probes on section of probe card

### Probe Test

Pad showing probe marks

Pad showing bonding wire

Die showing wire bonds to package cavity

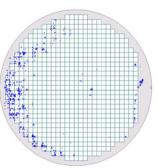

#### **Probe Test**

Production probe test facility

Goal to Identify defective die on wafer

#### Typical ATE System (less handler)

Main Frame

#### Automated Test Equipment (ATE)

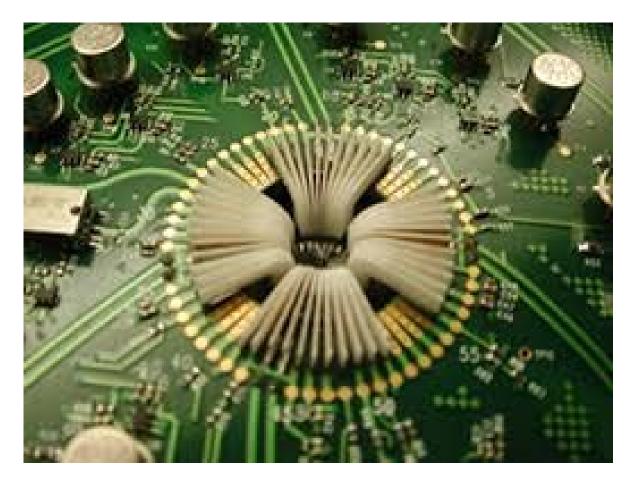

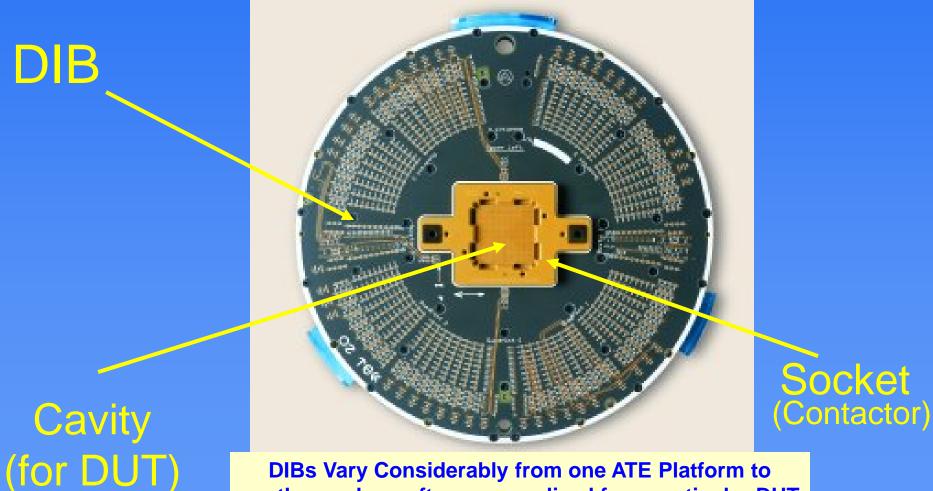

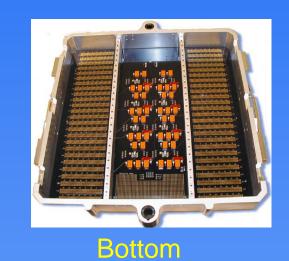

## **Device Interface Board - DIB** (Load Board)

**DIBs Vary Considerably from one ATE Platform to** another and are often personalized for a particular DUT

## Octal Site DIB

Flex Octal (Teradyne)

Top

## **Final Test**

# End of Lecture 11