# EE 330 Lecture 41

# **Digital Circuits**

- Propagation Delay With Multiple Levels of Logic

- Overdrive

# **Digital Circuit Design**

- Hierarchical Design

- Basic Logic Gates

- Properties of Logic Families

- Characterization of CMOS

Inverter

- Static CMOS Logic Gates

- Ratio Logic

- Propagation Delay

- Simple analytical models

- Elmore Delay

- Sizing of Gates

Propagation Delay with Multiple Levels of Logic

- Optimal driving of Large

Capacitive Loads

- Power Dissipation in Logic Circuits

- Other Logic Styles

- Array Logic

- Ring Oscillators

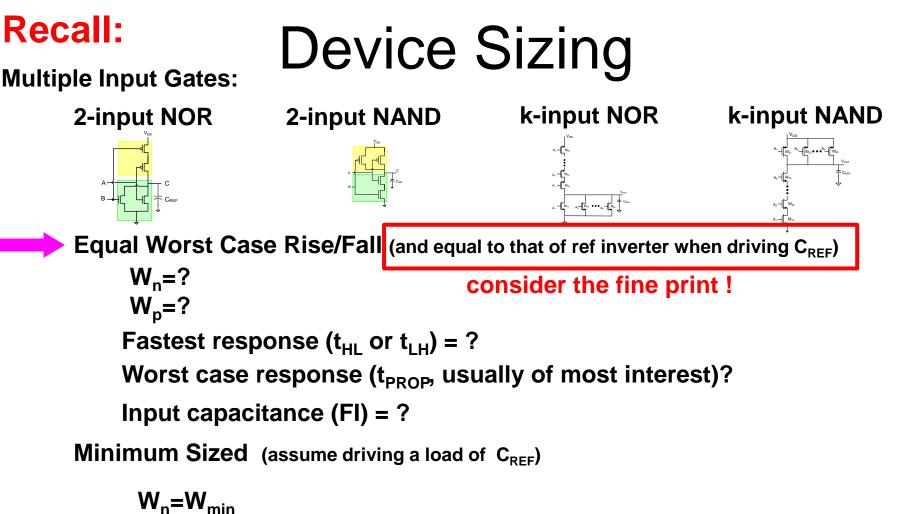

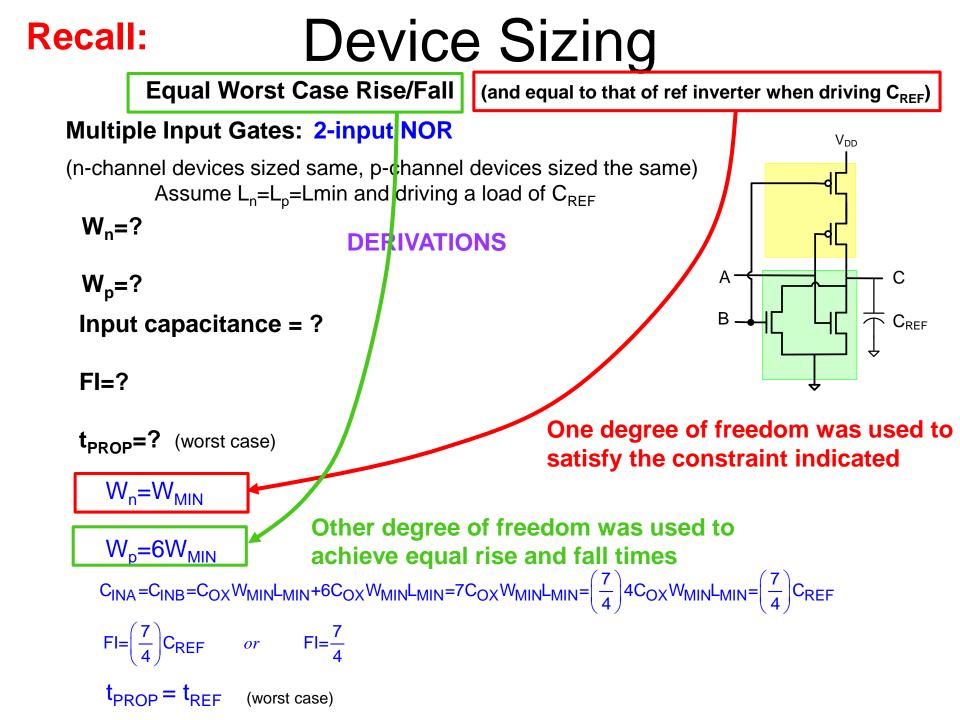

Assume all gates sized for equal worst-case rise/fall times

For n levels of logic between A and F

$$\mathbf{t}_{\mathsf{PROP}} = \sum_{k=1}^{\mathsf{n}} \mathbf{t}_{\mathsf{PROP}}(k)$$

Analysis strategy : Express delays in terms of those of reference inverter

Assume:

- all gates sized for equal worst-case rise/fall times

- all gates sized to have rise and fall times equal to that of ref inverter when driving C<sub>REF</sub>

**Observe:**

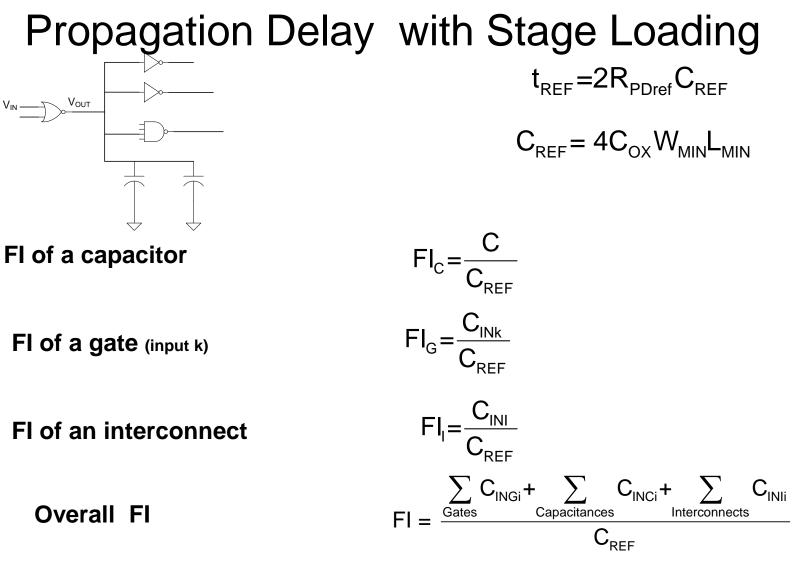

Propagation delay of these gates will be scaled by the ratio of the total load capacitance on each gate to C<sub>REF</sub>

What loading will a gate see?

- Input capacitance to other gates

- Any load capacitors

- Parasitic interconnect capacitnaces

FI can be expressed either in units of capacitance or normalized to  $C_{REF}$ Most commonly FI is normalized but must determine from context If gates sized to have same drive as ref inverter  $t_{prop-k} = t_{REF} \bullet FI_{LOAD-k}$

Assume all gates sized for equal worst-case rise/fall times

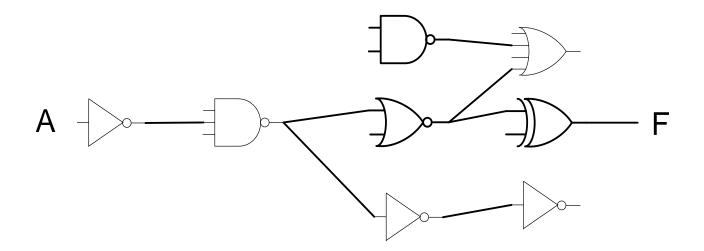

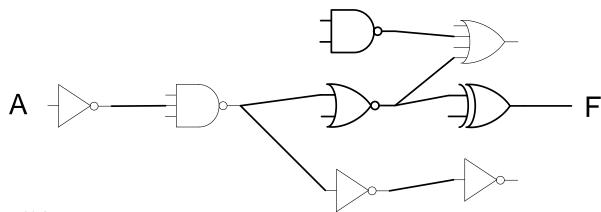

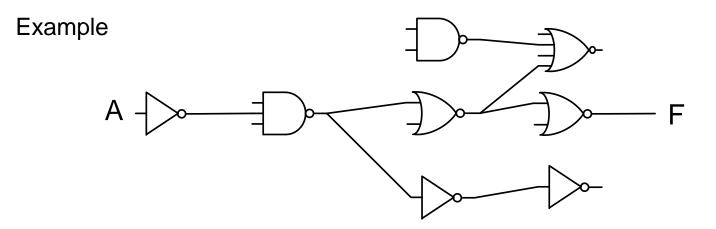

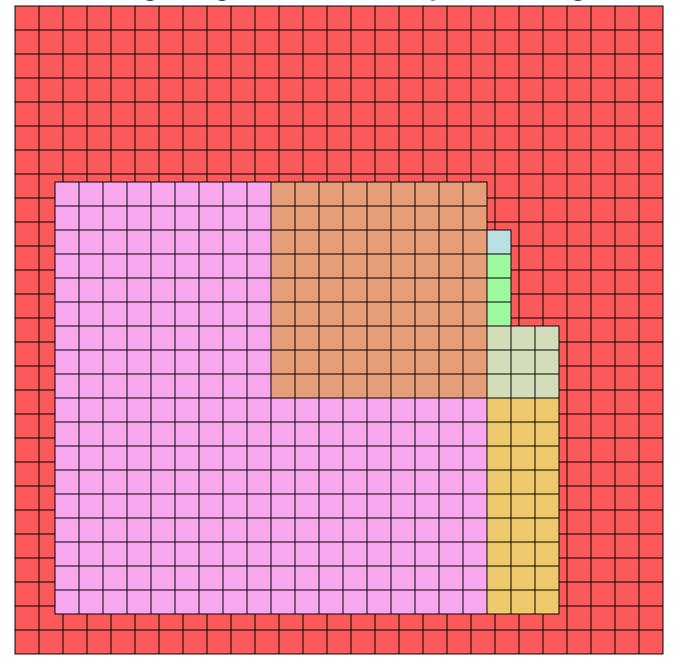

Assume all gate drives are the same as that of reference inverter Neglect interconnect capacitance, assume load of 10C<sub>REF</sub> on F output

Determine propagation delay from A to F

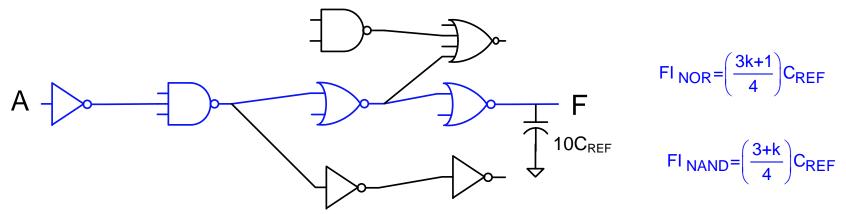

Assume all gates sized for equal worst-case rise/fall times Assume all gate drives are the same as that of reference inverter Neglect interconnect capacitance, assume load of 10C<sub>REF</sub> on F output Determine propagation delay from A to F

#### What loading will a gate see?

**Derivation:**

$$FI_{2} = \frac{6}{4}C_{REF} \qquad FI_{3} = C_{REF} + \frac{7}{4}C_{REF} \qquad FI_{4} = \frac{7}{4}C_{REF} + \frac{13}{4}C_{REF} \qquad FI_{LOAD} = FI_{"5"} = 10C_{REF}$$

10C<sub>REF</sub>

Example

Assume all gates sized for equal worst-case rise/fall times Assume all gate drives are the same as that of reference inverter Neglect interconnect capacitance, assume load of 10C<sub>RFF</sub> on F output

Determine propagation delay from A to F

DERIVATIONS

$$\begin{aligned} \mathsf{FI}_{2} = & \frac{6}{4} \mathsf{C}_{\mathsf{REF}} & \mathsf{FI}_{3} = \mathsf{C}_{\mathsf{REF}} + \frac{7}{4} \mathsf{C}_{\mathsf{REF}} & \mathsf{FI}_{4} = \frac{7}{4} \mathsf{C}_{\mathsf{REF}} + \frac{13}{4} \mathsf{C}_{\mathsf{REF}} & \mathsf{FI}_{5} = 10 \mathsf{C}_{\mathsf{REF}} \\ t_{\mathsf{PROP1}} = & \frac{6}{4} t_{\mathsf{REF}} & t_{\mathsf{PROP2}} = \left(1 + \frac{7}{4}\right) t_{\mathsf{REF}} & t_{\mathsf{PROP3}} = \left(\frac{7}{4} + \frac{13}{4}\right) t_{\mathsf{REF}} & t_{\mathsf{PROP4}} = 10 t_{\mathsf{REF}} \\ t_{\mathsf{PROP4}} = & \sum_{k=1}^{n} t_{\mathsf{PROPk}} = t_{\mathsf{REF}} \sum_{k=1}^{n} \mathsf{FI}_{(k+1)} = t_{\mathsf{REF}} \left(\frac{6}{4} + \frac{11}{4} + \frac{20}{4} + 10\right) = t_{\mathsf{REF}} \left(19.25\right) \end{aligned}$$

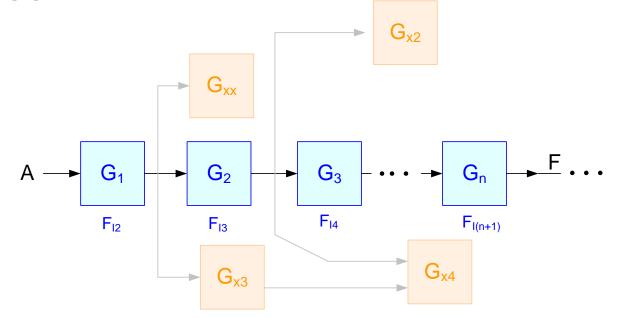

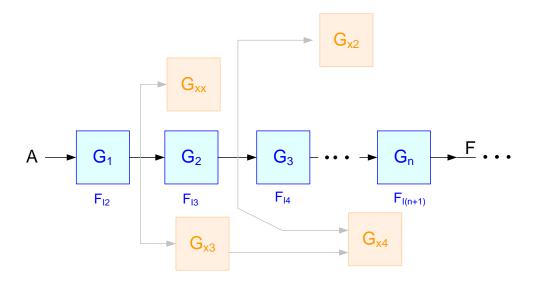

### Propagation Delay Through Multiple Stages of Logic with Stage Loading

(assuming gate <u>drives</u> are all same as that of reference inverter)

Identify the gate path from A to F

Propagation delay from A to F:

$$t_{PROP} = t_{REF} \sum_{k=1}^{n} FI_{(k+1)}$$

This approach is analytically manageable, provides modest accuracy and is "faithful"

# **Digital Circuit Design**

- Hierarchical Design

- Basic Logic Gates

- Properties of Logic Families

- Characterization of CMOS Inverter

- Static CMOS Logic Gates

- Ratio Logic

- Propagation Delay

- Simple analytical models

- Elmore Delay

- Sizing of Gates

- Propagation Delay with Multiple Levels of Logic

- Optimal driving of Large Capacitive Loads

- Power Dissipation in Logic Circuits

- Other Logic Styles

- Array Logic

- Ring Oscillators

# What if the propagation delay is too long (or too short)?

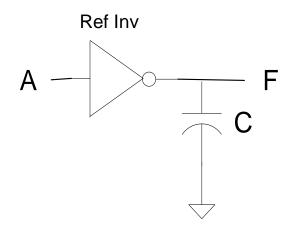

Propagation delay from A to F:

$$t_{PROP} = t_{REF} \sum_{k=1}^{n} FI_{(k+1)}$$

$$t_{PROPk} = t_{REF} FI_{(k+1)}$$

$W_p = W_{min}$

Fastest response  $(t_{HL} \text{ or } t_{LH}) = ?$ Slowest response  $(t_{HL} \text{ or } t_{LH}) = ?$ Worst case response  $(t_{PROP}, \text{ usually of most interest})?$ Input capacitance (FI) = ?

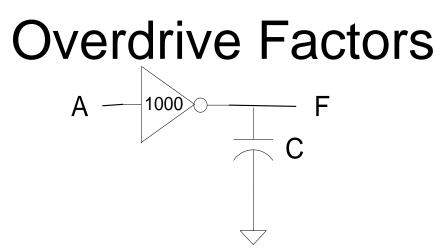

# **Overdrive Factors**

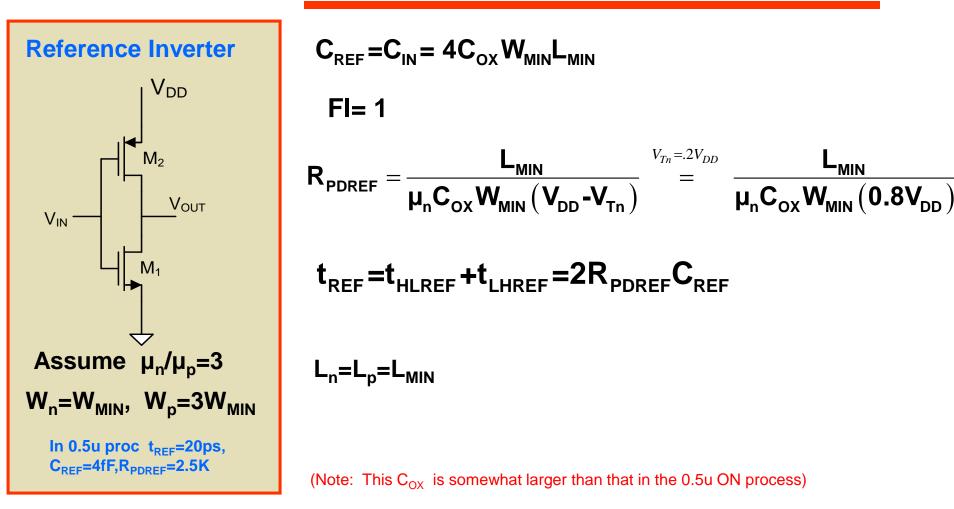

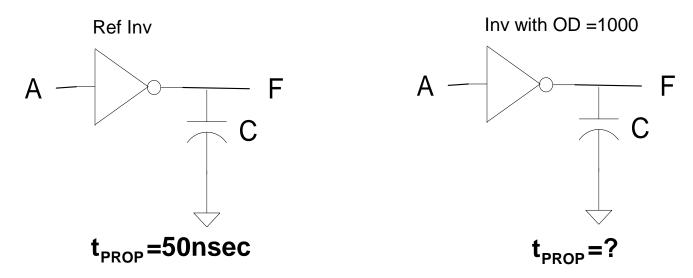

Example: Determine t<sub>prop</sub> in 0.5u process if C=10pF In 0.5u proc t<sub>REF</sub>=20ps, C<sub>REF</sub>=4fF,R<sub>PDREF</sub>=2.5K

$$\mathbf{t}_{\mathsf{PROP}} = \mathbf{t}_{\mathsf{REF}} \bullet \mathsf{FI} = \mathbf{t}_{\mathsf{REF}} \bullet \frac{10\,pF}{4\,fF} = \mathbf{t}_{\mathsf{REF}} \bullet 2500$$

t<sub>PROP</sub> =20ps • 2500 = 50nsec

#### Note this is unacceptably long !

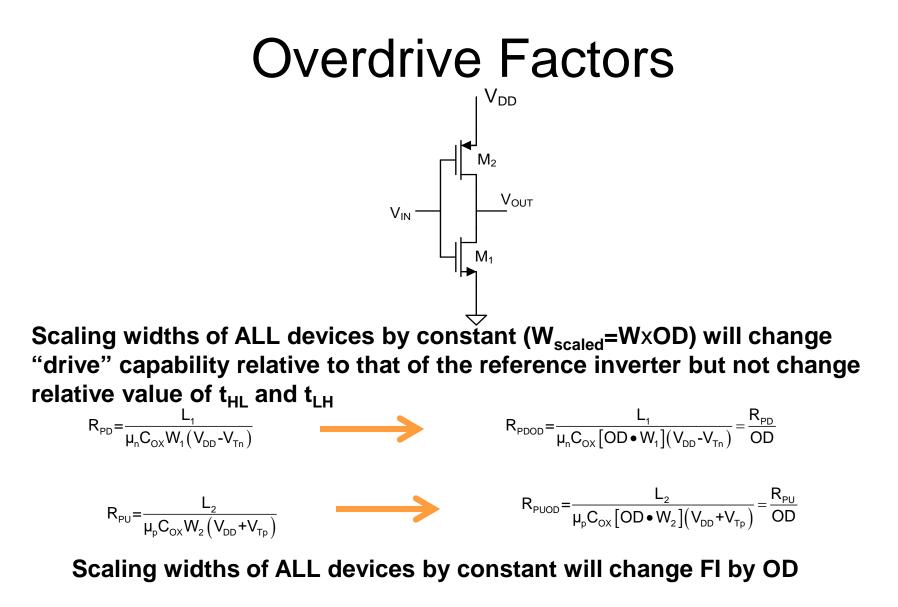

$C_{IN} = C_{OX} (W_1 L_1 + W_2 L_2)$

$C_{\text{INOD}} = C_{\text{OX}} \left( \left[ O \ D \bullet W_1 \right] L_1 + \left[ O \ D \bullet W_2 \right] L_2 \right) = O \ D \bullet C_{\text{IN}}$

# **Overdrive Factors**

**Example:** Determine  $t_{prop}$  in 0.5u process if C=10pF and OD=1000

$$\mathbf{t}_{\mathsf{PROP}} = \mathbf{t}_{\mathsf{REF}} \bullet \mathsf{FI} \bullet \frac{1}{\mathsf{OD}} = \mathbf{t}_{\mathsf{REF}} \bullet \frac{10\,pF}{4\,fF} = \mathbf{t}_{\mathsf{REF}} \bullet 2500$$

$$\mathbf{t}_{\mathsf{PROP}} = \mathbf{t}_{\mathsf{REF}} \bullet \mathsf{FI} \bullet \frac{1}{\mathsf{OD}} = \mathbf{t}_{\mathsf{REF}} \bullet \frac{10\,pF}{4\,fF} \bullet \frac{1}{1000} = \mathbf{t}_{\mathsf{REF}} \bullet 2.5$$

Note sizing the inverter with the OD improved delay by a factor of 1000 !

- By definition, the factor by which the W/L of all devices are scaled above those of the reference inverter is termed the overdrive factor, OD

- Scaling widths by overdrive factor DECREASES resistance by same factor

- Scaling all widths by a constant does not compromise the symmetry between the rise and fall times (i.e. t<sub>HL</sub>=t<sub>LH</sub>)

- Judicious use of overdrive can dramatically improve the speed of digital circuits

- Large overdrive factors are often used

- Scaling widths by overdrive factor INCREASES input capacitance by same factor - So is there any net gain in speed?

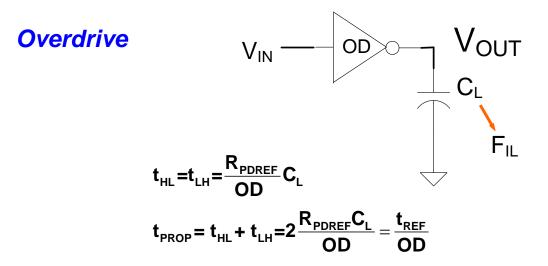

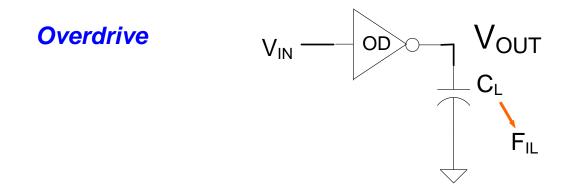

### Propagation Delay with Over-drive Capability

#### Asymmetric Overdrive

Define the Asymmetric Overdrive Factors of the stage to be the factor by which PU and PD resistors are scaled relative to those of the reference inverter.

$$R_{PDEFF} = \frac{R_{PDREF}}{OD_{HL}} \qquad R_{PUEFF} = \frac{R_{PUREF}}{OD_{LH}}$$

$$t_{HL} = \frac{R_{PDREF}}{OD_{HL}}C_{L} \qquad t_{LH} = \frac{R_{PDREF}}{OD_{LH}}C_{L}$$

$$t_{PROP} = t_{HL} + t_{LH} = \frac{R_{PDREF}}{OD_{HL}}C_{L} + \frac{R_{PDREF}}{OD_{LH}}C_{L} = R_{PDREF}C_{L} \left[\frac{1}{OD_{HL}} + \frac{1}{OD_{LH}}\right] = \frac{t_{REF}}{2} \left[\frac{1}{OD_{HL}} + \frac{1}{OD_{LH}}\right]F_{IL}$$

### Propagation Delay with Over-drive Capability

If inverter with OD is sized for equal rise/fall,  $OD_{HL}=OD_{LH}=OD$

$$\mathbf{t}_{\mathsf{PROP}} = \mathbf{R}_{\mathsf{PDREF}} \mathbf{C}_{\mathsf{L}} \left[ \frac{1}{\mathbf{OD}_{HL}} + \frac{1}{\mathbf{OD}_{LH}} \right] = \mathbf{R}_{\mathsf{PDREF}} \mathbf{C}_{\mathsf{L}} \frac{\mathbf{2}}{\mathbf{OD}} = \mathbf{t}_{\mathsf{REF}} \frac{\mathbf{F}_{\mathsf{IL}}}{\mathbf{OD}}$$

OD may be larger or smaller than 1

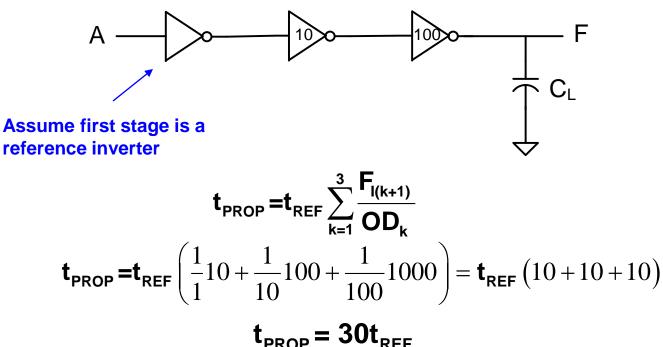

# Propagation Delay with Over-drive Capability

#### Example

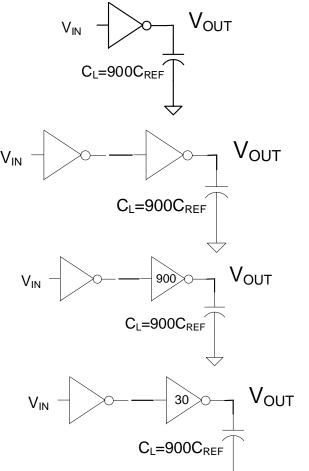

Compare the propagation delays. Assume the OD is 900 in the third case and 30 in the fourth case. Don't worry about the extra inversion at this time.

$$t_{PROP} = 900t_{REF}$$

$$\mathbf{t}_{\mathsf{PROP}} = \mathbf{t}_{\mathsf{REF}} + \mathbf{900t}_{\mathsf{REF}} = \mathbf{901t}_{\mathsf{REF}}$$

$\mathbf{t}_{\text{PROP}} \texttt{=} \textbf{900t}_{\text{REF}} + \mathbf{t}_{\text{REF}} = \textbf{901t}_{\text{REF}}$

$$\mathbf{t}_{\mathsf{PROP}} = \mathbf{30t}_{\mathsf{REF}} + \mathbf{30t}_{\mathsf{REF}} = \mathbf{60t}_{\mathsf{REF}}$$

- Dramatic reduction in t<sub>PROP</sub> is possible (input is driving same in last 3 cases)

- Will later determine what optimal number of stages and sizing is

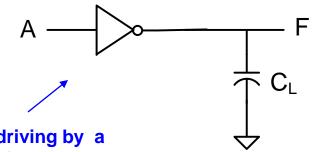

Example

Assume C<sub>L</sub>=1000C<sub>REF</sub>

Assume driving by a reference inverter

t<sub>PROP</sub>=?

In 0.5u proc  $t_{REF}$ =20ps, C<sub>REF</sub>=4fF,R<sub>PDREF</sub>=2.5K

Example

Assume driving by a reference inverter

t<sub>PROP</sub>=1000t<sub>RFF</sub>

$t_{PROP}$  is too long !

Assume C<sub>L</sub>=1000C<sub>REF</sub>

In 0.5u proc  $t_{REF}$ =20ps, C<sub>REF</sub>=4fF,R<sub>PDREF</sub>=2.5K

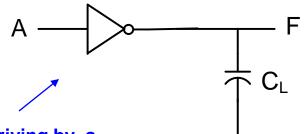

#### Example

Assume  $C_1 = 1000C_{RFF}$

Assume first stage is a reference inverter

t<sub>PROP</sub>=?

$$\mathbf{t}_{\mathsf{PROP}} = \mathbf{t}_{\mathsf{REF}} \sum_{k=1}^{2} \frac{\mathbf{F}_{\mathsf{I}(k+1)}}{\mathsf{OD}_{\mathsf{k}}}$$

$$\mathbf{t}_{\mathsf{PROP}} = \mathbf{t}_{\mathsf{REF}} \left( \frac{1}{1} 1000 + \frac{1}{1000} 1000 \right) = \mathbf{t}_{\mathsf{REF}} \left( 1000 + 1 \right)$$

$$\mathbf{t}_{\mathsf{PROP}} = \mathbf{t}_{\mathsf{REF}} \left( 1001 \right)$$

Delay of second inverter is really small but overall delay is even longer than before!

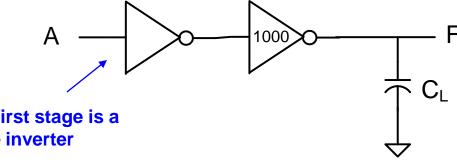

Example

Assume C<sub>L</sub>=1000C<sub>REF</sub>

Dramatic reduction is propagation delay (over a factor of 30!)

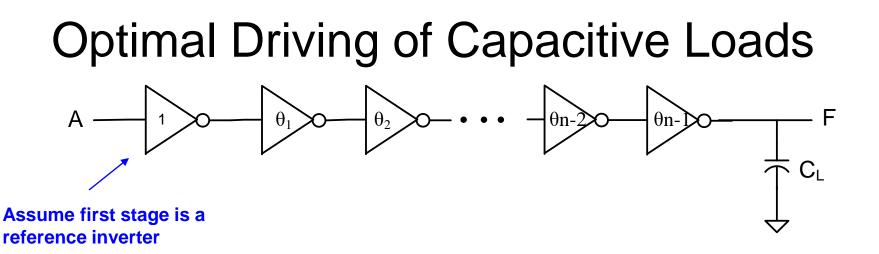

What is the fastest way to drive a large capacitive load?

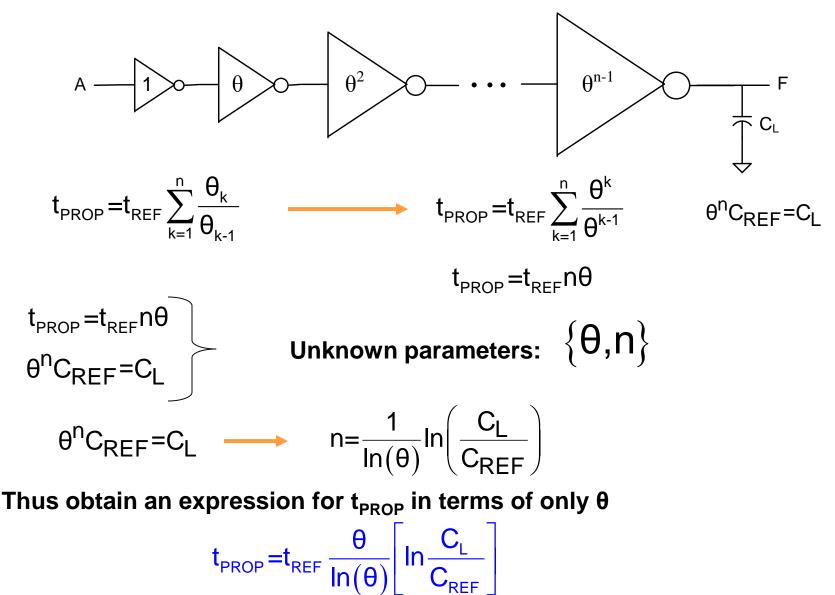

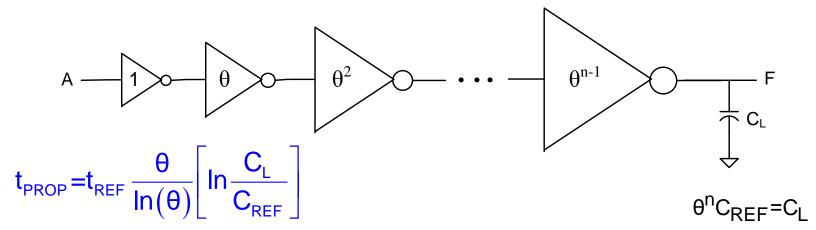

Need to determine the number of stages, n, and the OD factors for each stage to minimize  $t_{PROP}$ .

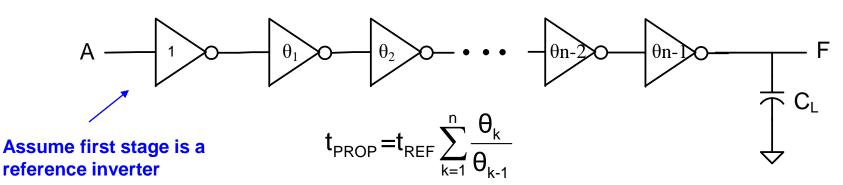

where  $\theta_0 = 1$ ,  $\theta_n = C_L / C_{REF}$

This becomes an n-parameter optimization (minimization) problem !

Unknown parameters:  $\{\theta_1, \theta_2, ..., \theta_{n-1}, n\}$

An n-parameter nonlinear optimization problem is generally difficult !!!!

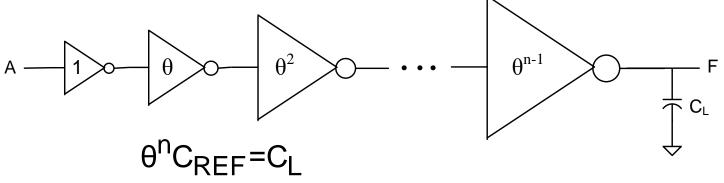

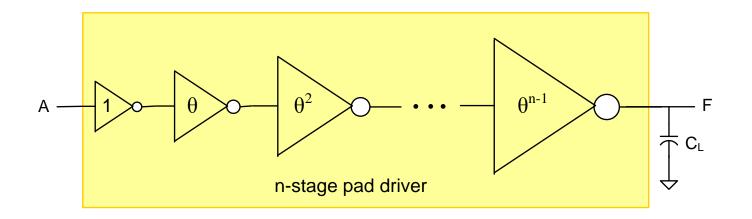

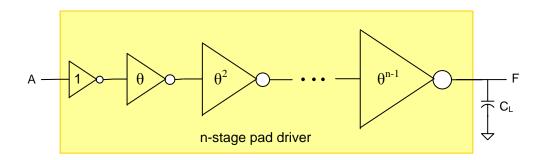

Order reduction strategy : Assume overdrive of stages increases by the same factor clear until the load

This becomes a 2-parameter optimization (minimization) problem ! Unknown parameters:  $\{\theta, n\}$

One constraint :  $\theta^{n}C_{REF} = C_{L}$

One degree of freedom

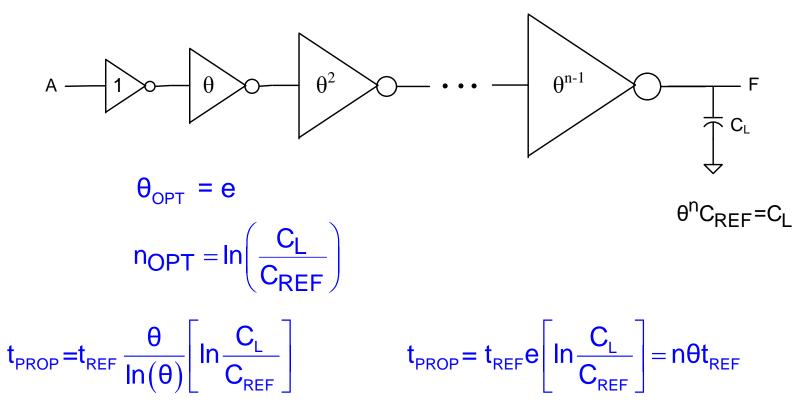

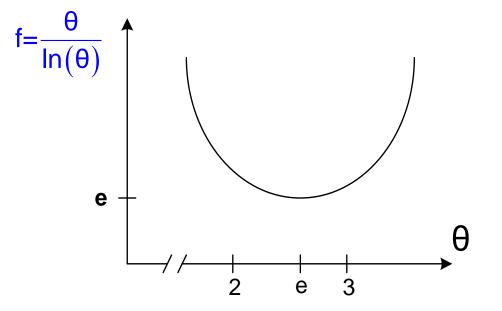

Is suffices to minimize the function  $f(\theta) = \frac{\nabla}{\ln(\theta)}$  $\frac{df}{d\theta} = \frac{\ln(\theta) - \theta \cdot \left(\frac{1}{\theta}\right)}{\left(\ln(\theta)\right)^2} = 0$  $\ln(\theta) - 1 = 0 \qquad \rightarrow \quad \theta = e$  $n = \frac{1}{\ln(\theta)} \ln\left(\frac{C_L}{C_{\text{PEE}}}\right) \qquad \rightarrow \quad n = \ln\left(\frac{C_L}{C_{\text{PEE}}}\right)$

- minimum at  $\theta$ =e but shallow inflection point for 2< $\theta$ <3

- practically pick  $\theta$ =2,  $\theta$ =2.5, or  $\theta$ =3

- since optimization may provide non-integer for n, must pick close integer

- Often termed a pad driver

- Often used to drive large internal busses as well

- Generally included in standard cells or in cell library

- Device sizes can become very large

- Odd number of stages will cause signal inversion but usually not a problem

Example: Design a pad driver for driving a load capacitance of 10pF, determine  $t_{PROP}$  for the pad driver, and compare this with the propagation delay for driving the pad with a minimum-sized reference inverter to 0.5 u proc t<sub>REF</sub>=20ps,

$$n_{OPT} = In \left(\frac{C_L}{C_{REF}}\right) = In \left(\frac{10pF}{4fF}\right) = 7.8$$

C<sub>REE</sub>=4fF,R<sub>PDREE</sub>=2.5K

$$W_{nk} = 2.5^{k-1} \bullet W_{REF}, \qquad W_{pk} = 3 \bullet 2.5^{k-1} \bullet W_{REF}$$

Example: Design a pad driver for driving a load capacitance of 10pF, determine  $t_{PROP}$  for the pad driver, and compare this with the propagation delay for driving the pad with a minimum-sized

reference inverter. In 0.5u proc t<sub>REF</sub>=20ps,

$C_{REF}=4fF, R_{PDREF}=2.5K$   $W_{nk}=2.5^{k-1} \bullet W_{REF}, W_{pk}=3 \bullet 2.5^{k-1} \bullet W_{REF}$

$$V_{REF} = W_{MIN} \quad L_n = L_p = L_{MIN}$$

| k | n-channel |      | p-channel   |

|---|-----------|------|-------------|

| 1 | 1         | WMIN | 3 VVMIN     |

| 2 | 2.5       | WMIN | 7.5 WMIN    |

| 3 | 6.25      | WMIN | 18.75 WMIN  |

| 4 | 15.6      | WMIN | 46.9 W/MIN  |

| 5 | 39.1      | WMIN | 117.2 WMIN  |

| 6 | 97.7      | WMIN | 293.0 WMIN  |

| 7 | 244.1     | WMIN | 732.4 WMIN  |

| 8 | 610.4     | WMIN | 1831.1 WMIN |

#### Note devices in last stage are very large !

Example: Design a pad driver for driving a load capacitance of 10pF, determine  $t_{PROP}$  for the pad driver, and compare this with the propagation delay for driving the pad with a minimum-sized reference inverter to 0.5 u proc t\_{REF}=20ps,

$C_{REF}=4fF,R_{PDREF}=2.5K$   $W_{nk}=2.5^{k-1} \bullet W_{REF},$   $W_{pk}=3 \bullet 2.5^{k-1} \bullet W_{REF}$

$t_{PROP} \cong n\theta t_{REF} = 8 \cdot 2.5 \cdot t_{REF} = 20 t_{REF}$

More accurately:

$$\mathbf{t}_{\mathsf{PROP}} = \mathbf{t}_{\mathsf{REF}} \left( \sum_{k=1}^{7} \theta + \frac{1}{\theta^{7}} \frac{\mathbf{C}_{\mathsf{L}}}{\mathbf{C}_{\mathsf{REF}}} \right) = \mathbf{t}_{\mathsf{REF}} \left( 17.5 + \frac{1}{610} 2500 \right) = 21.6 \mathbf{t}_{\mathsf{REF}}$$

Example: Design a pad driver for driving a load capacitance of 10pF, determine  $t_{PROP}$  for the pad driver, and compare this with the propagation delay for driving the pad with a minimum-sized reference inverter,  $0.5u \text{ proc } t_{REF}=20\text{ps}, C_{REF}=4fF, R_{PDREF}=2.5\text{K}$   $W_{nk}=2.5^{k-1} \cdot W_{REF}, W_{pk}=3 \cdot 2.5^{k-1} \cdot W_{REF}$

If driven directly with the minimum-sized reference inverter

$$t_{PROP} = t_{REF} \frac{C_L}{C_{REF}} = 2500 t_{REF}$$

Note an improvement in speed by a factor of

$$r = \frac{2500}{20} = 125$$

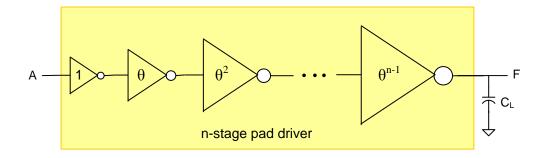

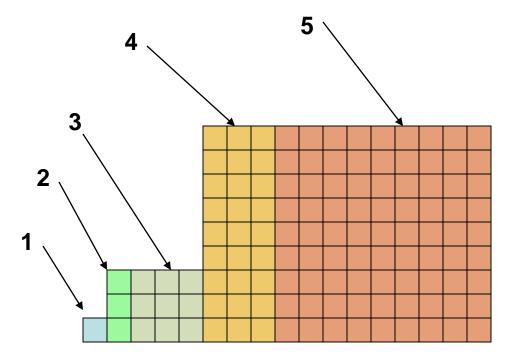

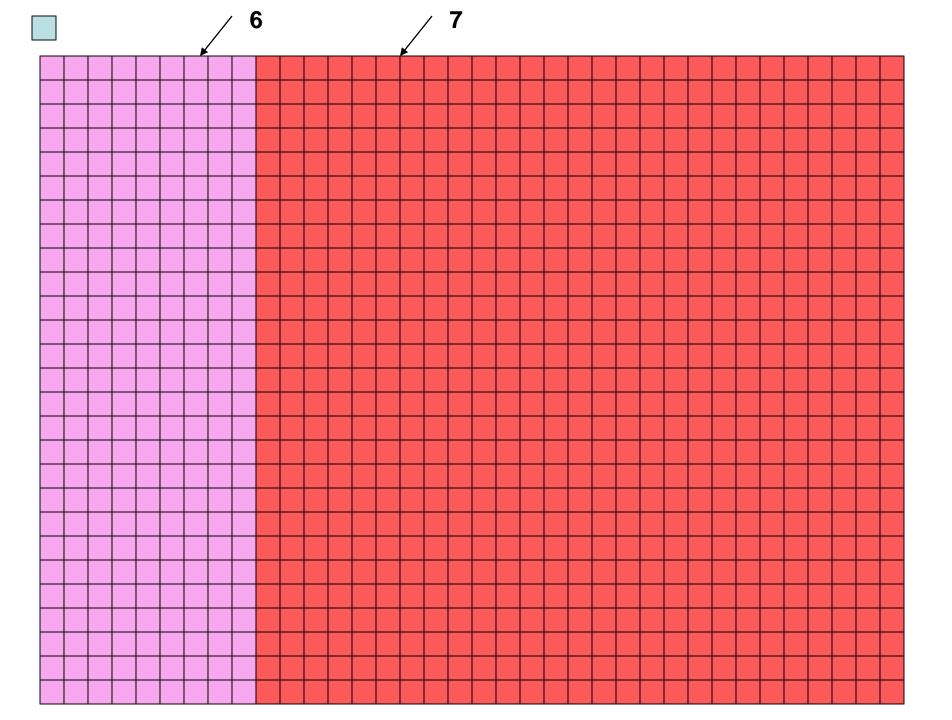

# Pad Driver Size Implications

#### Consider a 7-stage pad driver and assume $\theta = 3$

#### Area of Last Stage Larger than that of all previous stages combined!

# **End of Lecture 41**