#### 1.Introduction

If the automobile had followed the same development cycle as the computer, a Rolls-Royce would today cost \$100, get one million miles to the gallon and explode once a year

## Semiconductor processing

- Semiconductor fabrication

- Layout fundamental

- Semiconductor testing

- Semiconductor assembling

# Different Electrical Tests for IC Production (From Design Stage to Packaged IC)

| Test                       | Stage of IC<br>Manufacture | Wafer- or<br>Chip-Level | Test Description                                                                                                                                                                                     |

|----------------------------|----------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IC Design Verification     | Pre-Production             | Wafer level             | Characterize, debug and verify new chip design to insure it meets specifications.                                                                                                                    |

| In-Line Parametric<br>Test | Wafer fabrication          | Wafer level             | Production process verification test performed early in the fabrication cycle (near front-end of line) to monitor process.                                                                           |

| Wafer Sort (Probe)         | Wafer fabrication          | Wafer level             | Product functional test to verify each die meets product specifications.                                                                                                                             |

| Burn-In Reliability        | Packaged IC                | Packaged<br>chip level  | ICs powered up and tested at elevated temperature to stress product to detect early failures (in some cases, reliability testing is also done at the wafer level during in-line parametric testing). |

| Final Test                 | Packaged IC                | Packaged chip level     | Product functionality test using product specifications.                                                                                                                                             |

Digital IC 4/57

#### **Automated Electrical Tester**

Digital IC 5/57

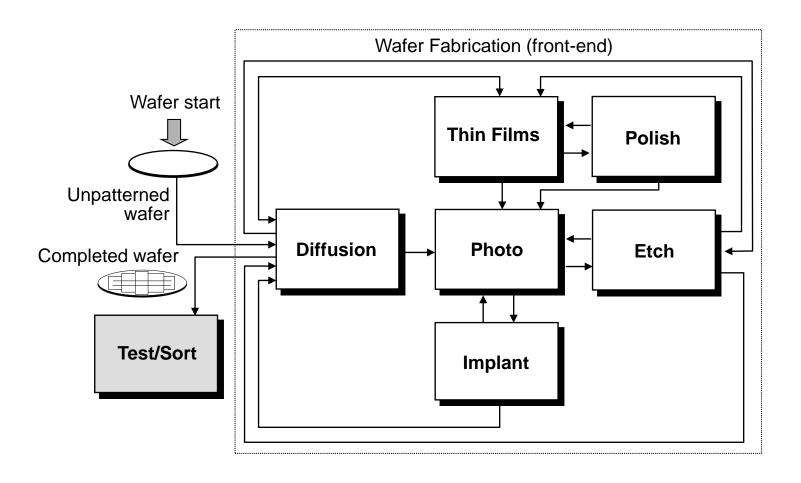

#### Wafer Fab Process Flow with Test

Digital IC 6/57

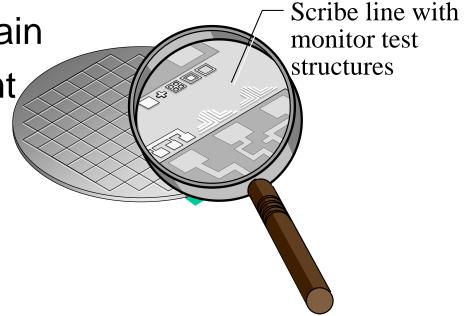

#### Wafer Test

- In-line Parametric Test (a.k.a. wafer electrical test, WET)

- In-line test structure

- In-line test type

In-line test data explain

In-line test equipment

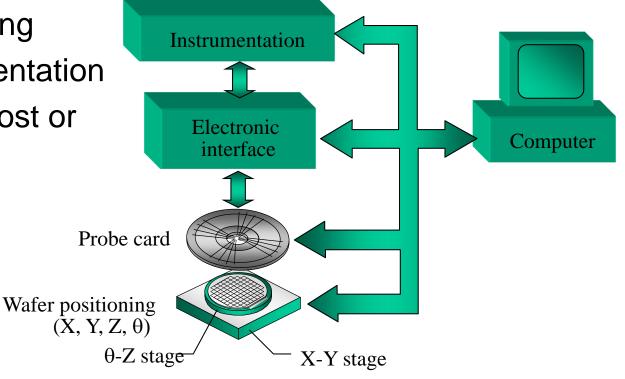

# In-line Parametric Test Systems

- Probe card interface

- Wafer positioning

- Tester instrumentation

- Computer as host or server/network

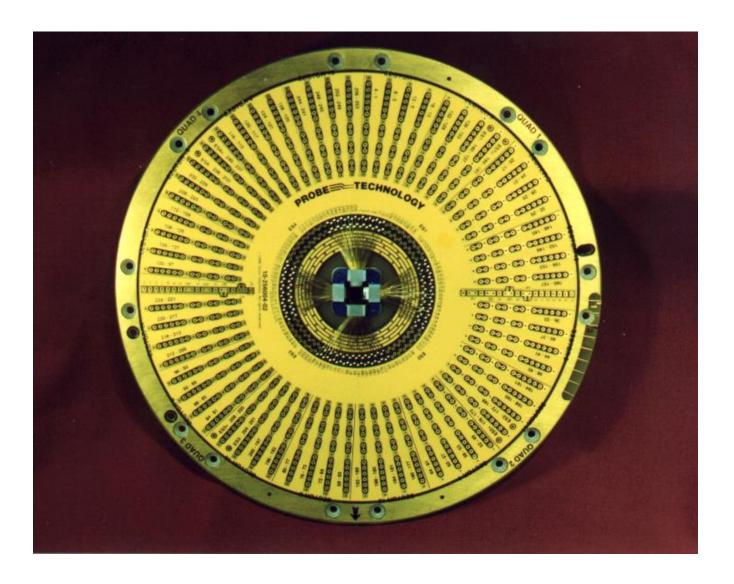

#### **Probe Card for Automatic Tester**

Digital IC 9/57

#### **Examples of Test Structure**

| Test Structure                        | Fault Measurement                                                                  |  |  |

|---------------------------------------|------------------------------------------------------------------------------------|--|--|

| Discrete transistors                  | Leakage current, breakdown voltage, threshold voltage and effective channel length |  |  |

| Various line widths                   | Critical dimensions                                                                |  |  |

| Box in a box                          | Critical dimensions and overlay registration                                       |  |  |

| Serpentine structure over oxide steps | Continuity and bridging                                                            |  |  |

| Resistivity structure                 | Film thickness                                                                     |  |  |

| Capacitor array structure             | Insulator materials and oxide integrity                                            |  |  |

| Contact or via string                 | Contact resistance and connections                                                 |  |  |

Digital IC 10/57

#### **Data Trends**

- The same die location keeps failing a parameter on a wafer.

- The same parameter is consistently failing on different wafers.

- There is excessive variation (e.g., > 10%) in measurement data from wafer to wafer.

- Lot-to-lot failure for the same parameter, indicating a major process problem.

Digital IC 11/57

#### Wafer Sort

- Wafer Sort (a.k.a. wafer probe)

- DC testing

- Output checking

- Function testing

- The Objectives of Wafer Sort

- Chip functionality: verify the operation of all chip functions to insure only good chips are sent to the next IC manufacturing stage of assembly and packaging.

- Chip sorting: sort good chips based on their operating speed performance (this is done by testing at several voltages and varying timing conditions).

- Fab yield response: Provide important fab yield information to assess and improve the performance of the overall fabrication process.

- Test coverage: Achieve high test coverage of the internal device nodes at the lowest cost.

Digital IC 12/57

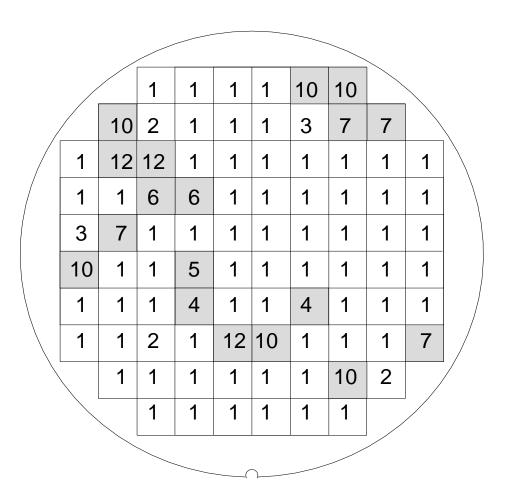

#### Wafer Bin Map with Bin Failures

Device: Example

Lot: Example

Wafer: 200 mm

Layer: Hardware Bins

Yield: 79.54%

Good: 70 Total: 88

Good

Bad

Digital IC 13/57

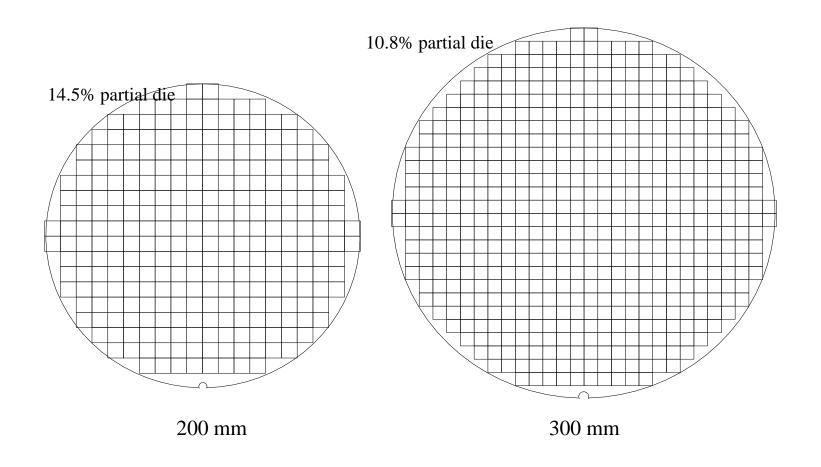

#### Reduced Partial Die on Large Wafer

Digital IC 14/57

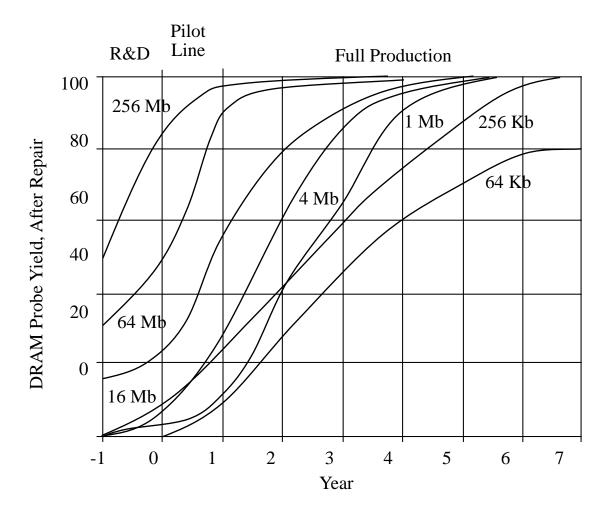

#### Reduced Time to Product Maturity for DRAM Production

Digital IC 15/57

# Semiconductor processing

- Semiconductor fabrication

- Layout fundamental

- Semiconductor testing

- Semiconductor assembling

## Packaging Requirements

- Electrical: Low parasitics

- Mechanical: Reliable and robust

- Thermal: Efficient heat removal

- Economical: Cheap

Digital IC 17/57

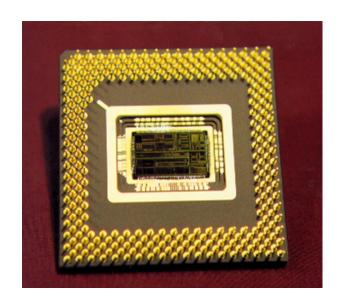

# Important Functions of IC Packaging

- Protection from the environment and handling damage.

- Interconnections for signals into and out of the chip.

- Physical support of the chip.

- Heat dissipation.

Digital IC 18/57

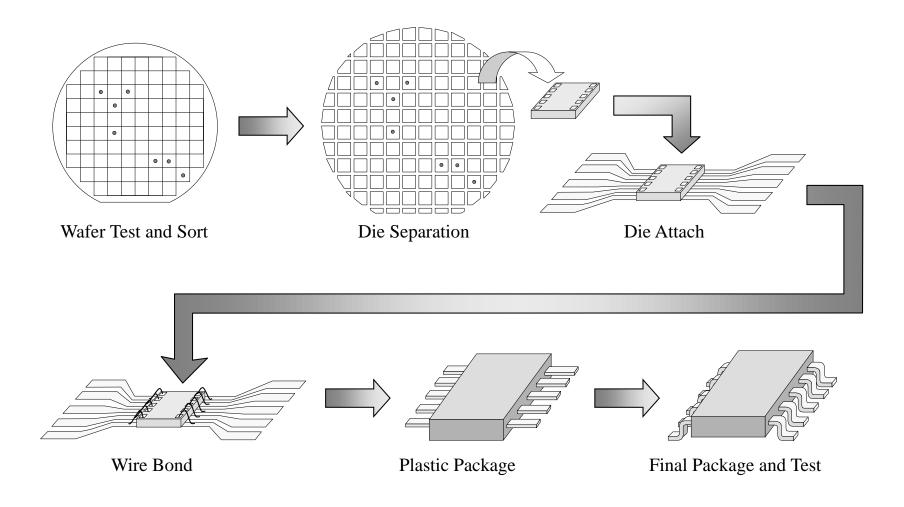

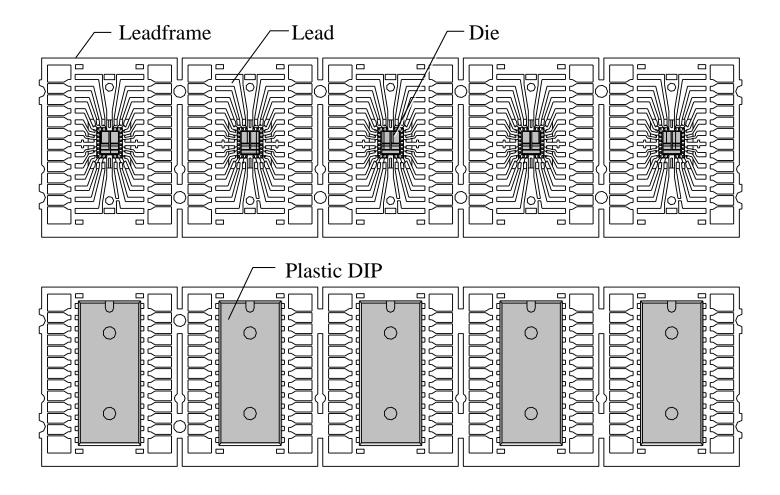

#### Traditional Assembly and Packaging

Digital IC 19/57

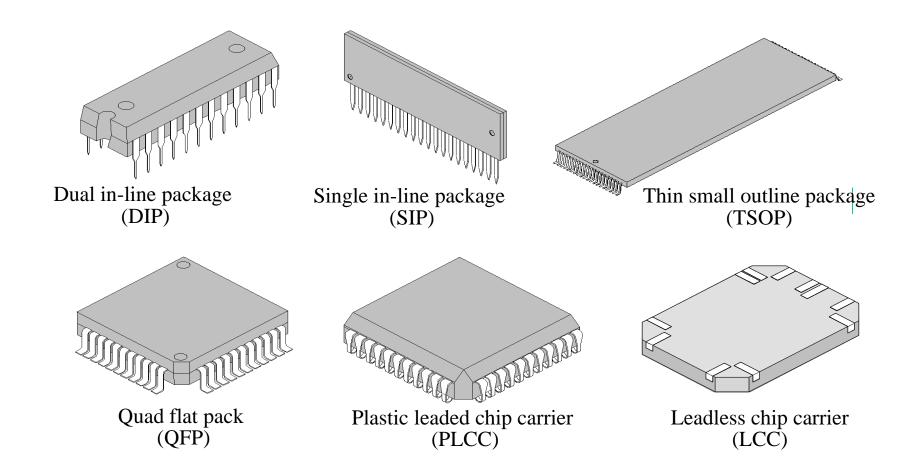

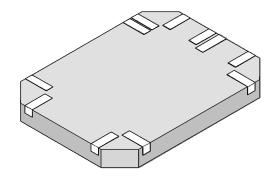

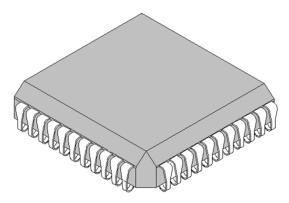

#### Typical IC Packages

Digital IC

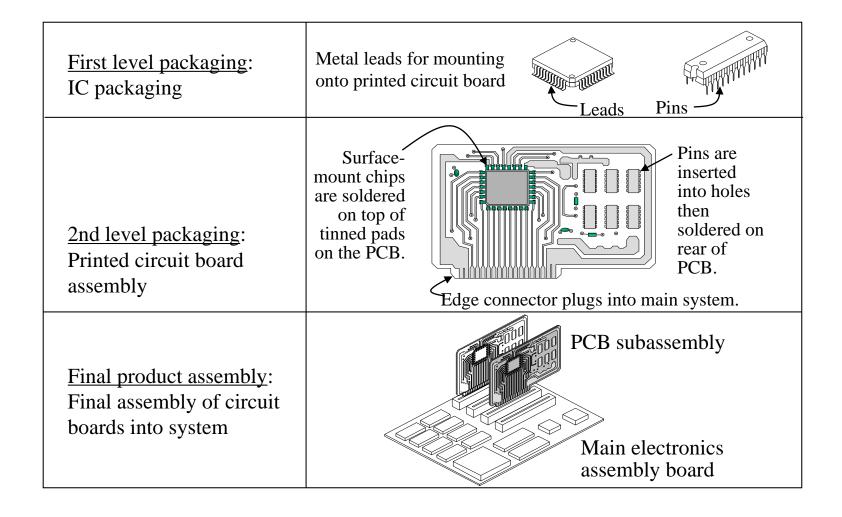

#### Levels of IC Packaging

Digital IC 21/57

### **Traditional Assembly**

- Wafer preparation (backgrind)

- Die separation

- Die attach

- Wire bonding

Digital IC 22/57

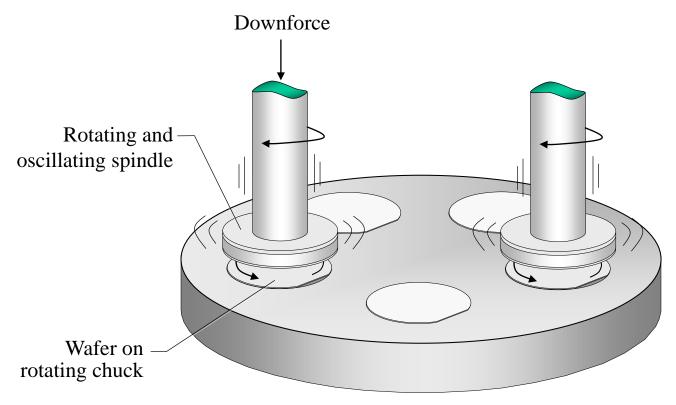

#### Schematic of the Backgrind Process

Table rotates only during indexing of wafers

Digital IC 23/57

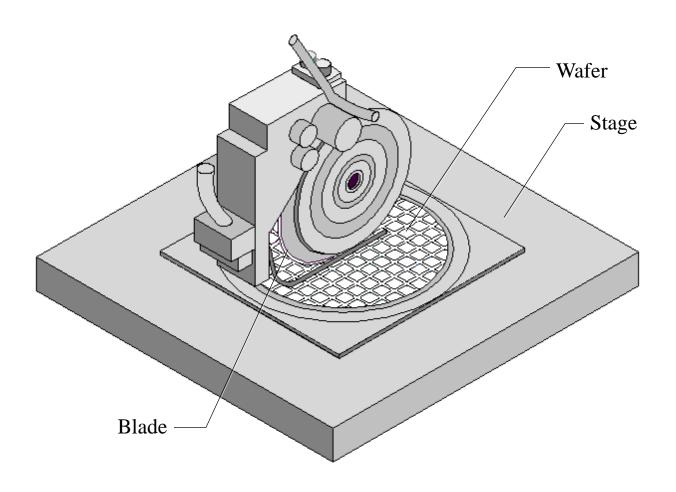

#### Wafer Saw and Sliced Wafer

Digital IC 24/57

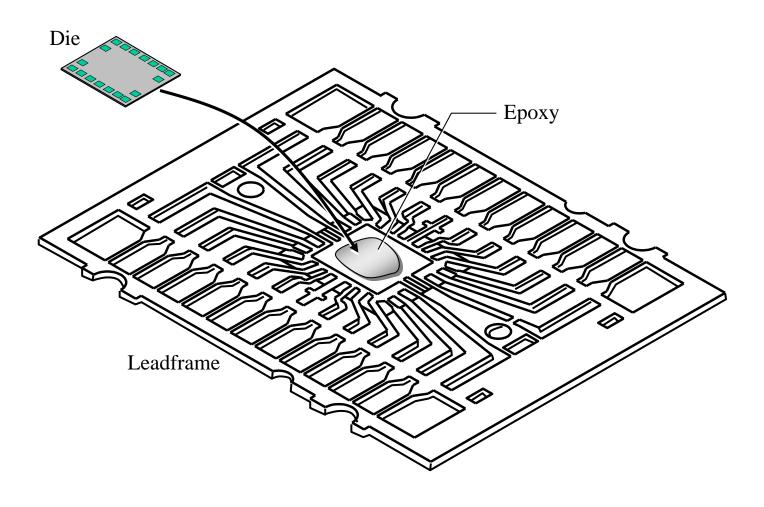

#### Typical Leadframe for Die Attach

Digital IC 25/57

#### **Epoxy Die Attach**

Digital IC 26/57

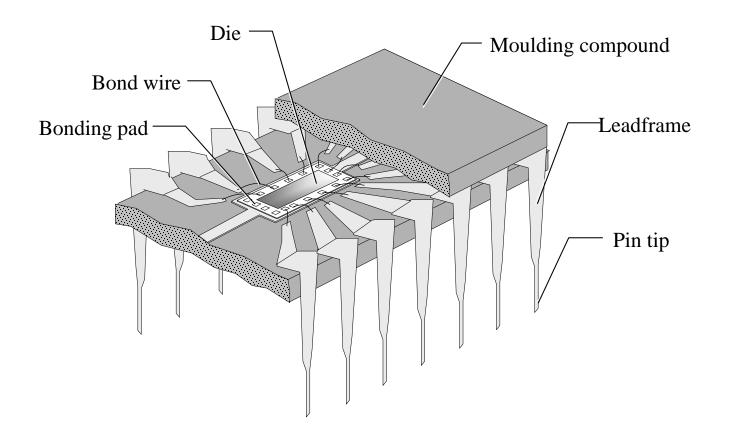

# Wires Bonded from Chip Bonding Pads to Leadframe

Digital IC 27/57

#### Wirebonding Chip to Leadframe

Digital IC 28/57

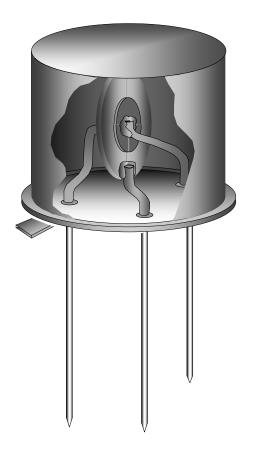

# Traditional Packaging

- Plastic Packaging

- Ceramic Packaging

- TO-Style Metal Package(old)

Digital IC 29/57

# General package mode

Plastic Dual In-Line Package (DIP) for Pin-In-Hole (PIH)1970s-1980s

Thin Small Outline Package (TSOP)

Memory and smartcard Single InLine Memory Module (SIMM)

Single In-Line Package (SIP), decreasing capacity and cost Memory application

## General package mode

Quad Flatpack (QFP) with Gull Wing Surface Mount Leads

Leadless Chip Carrier (LCC)

Plastic Leaded Chip Carrier (PLCC) with J-Leads for Surface Mount

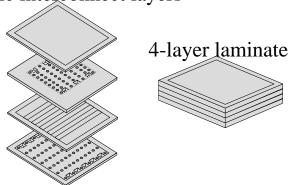

Laminated Refractory Ceramic Process Sequence

Ceramic interconnect layers

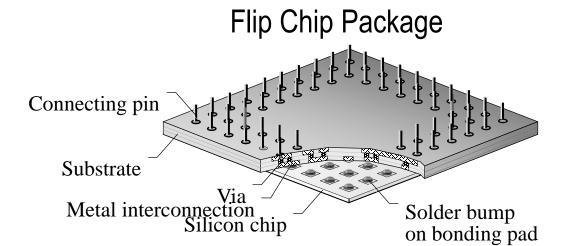

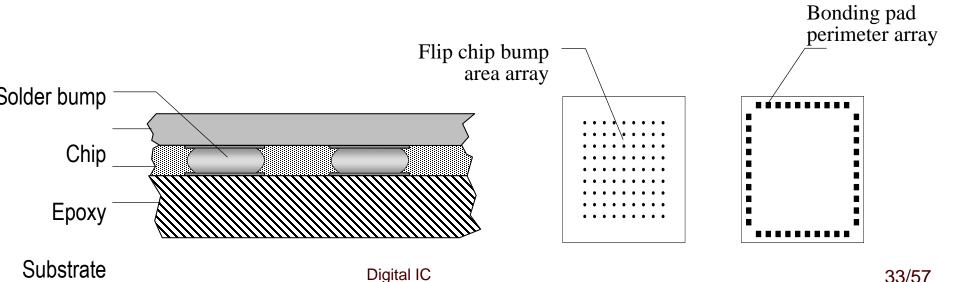

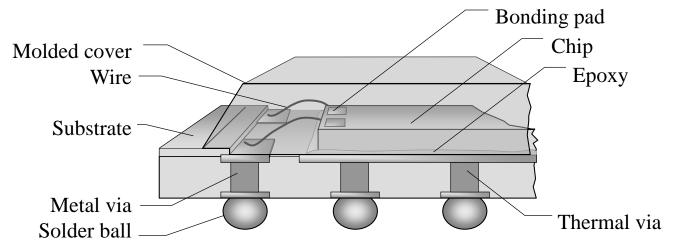

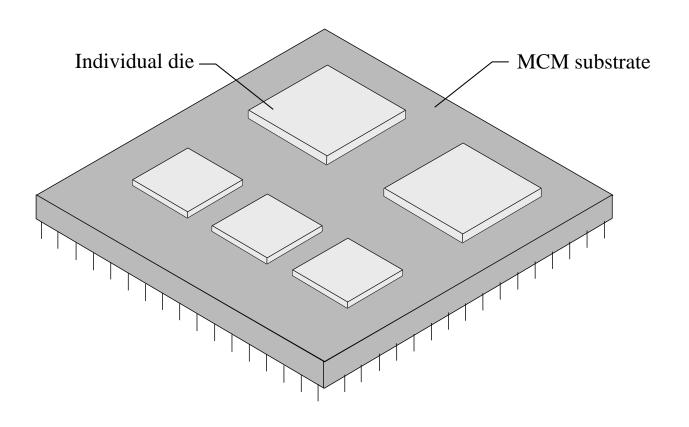

# Advanced Packaging

- Flip chip

- Ball grid array (BGA)

- Chip on board (COB)

- Tape automated bonding (TAB)

- Multichip modules (MCM)

- Chip scale packaging (CSP)

- Wafer-level packaging

#### **Advanced Packaging**

#### Flip Chip Area Array Solder **Bumps Versus Wirebond**

33/57

#### **Ball Grid Array**

Digital IC 34/57

#### Multichip Module (MCM)

Digital IC 35/57