### EE 434 Lecture 7

**Technology Files**

### Quiz 5

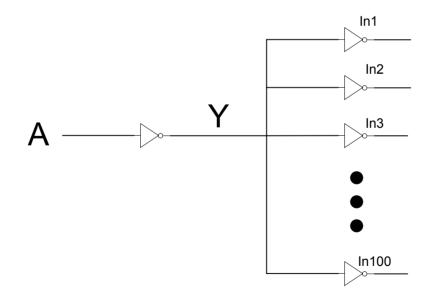

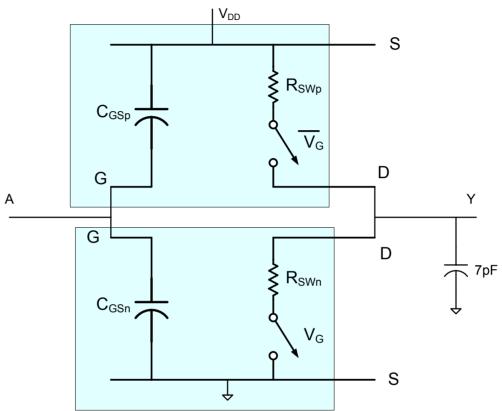

A CMOS inverter is driving a 100 CMOS inverters. Determine the rise and fall times at the output of this inverter if the input is driven by an ideal square wave. Assume the n-channel transistors in the inverters are modeled with an improved switch-level model with input capacitance of 20fF and a channel resistance of 1K $\Omega$  and the p-channel resistors use the same model but with corresponding parameters of 50fF and 2K  $\Omega$ .

### Quiz 5

A CMOS inverter is driving a 100 CMOS inverters. Determine the rise and fall times at the output of this inverter if the input is driven by an ideal square wave. Assume the n-channel transistors in the inverters are modeled with an improved switch-level model with input capacitance of 20fF and a channel resistance of 1K $\Omega$  and the p-channel resistors use the same model but with corresponding parameters of 50fF and 2K  $\Omega$ .

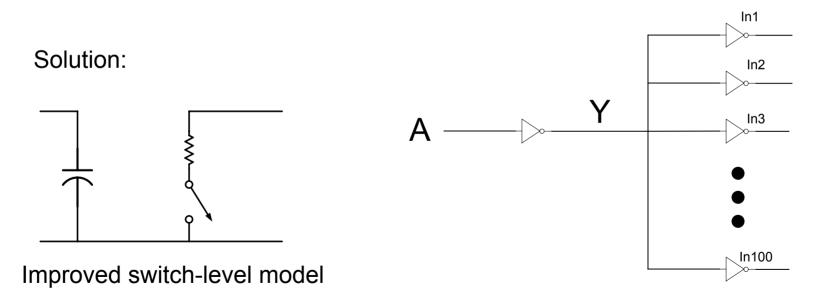

$$\begin{split} t_{\text{HL}} &\cong R_{\text{SWn}} C_{\text{L}} = 1 \text{K} \bullet 7 \text{pF} = 7 \text{nsec} \\ t_{\text{LH}} &\cong R_{\text{SWp}} C_{\text{L}} = 2 \text{K} \bullet 7 \text{pF} = 14 \text{nsec} \end{split}$$

### **Review from Last Time**

- Improved switch-level model can be used to predict rise and fall times in digital circuits

- Stick diagrams often useful for determining placement and routing strategies

- Gives insight

- Not included as a cell view in integrated tool flows

# **Technology Files**

- Provide Information About Process

- Process Flow

- Model Parameters

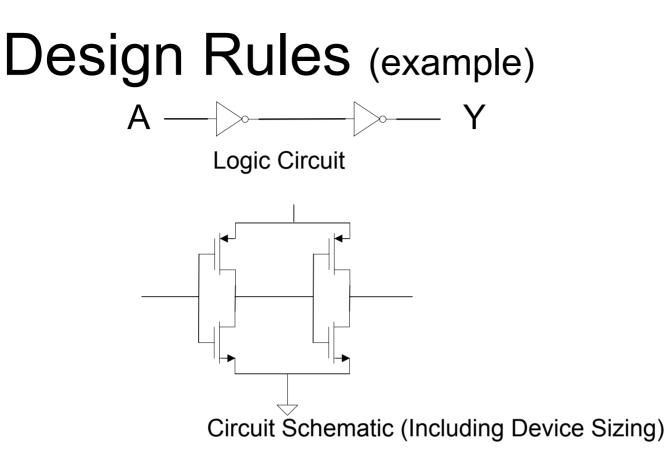

- Design Rules

- Serve as Interface Between Design Engineer and Process Engineer

- Insist on getting information that is deemed important for a design

- Limited information available in academia

- Foundries often sensitive to who gets access to information

- Customer success and satisfaction is critical to foundries

# **Technology Files**

- Process Flow (will discuss next week)

- Model Parameters (will discuss in detail after device models are introduced)

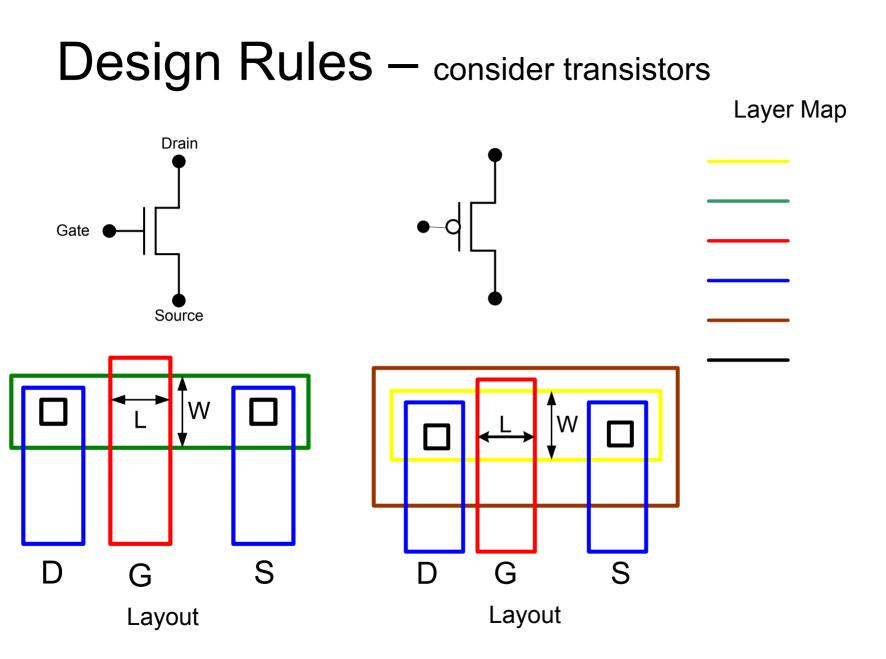

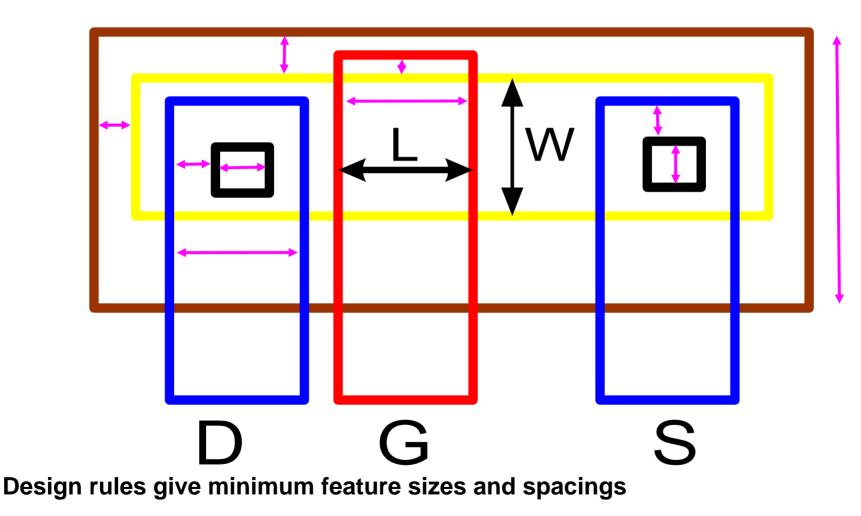

- Design Rules

Give minimum feature sizes, spacing, and other constraints that are acceptable in a process

• Very large number of devices can be reliably made with the design rules of a process

• Yield and performance unpredictable and often low if rules are violated

Compatible with design rule checker in integrated toolsets

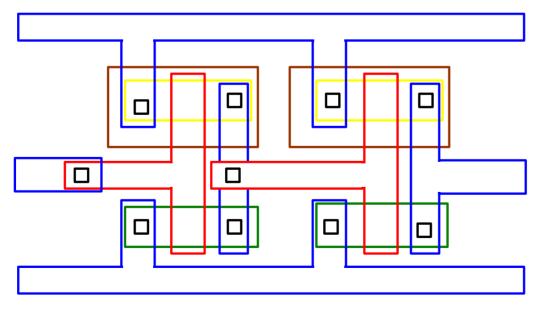

Layout always represented in a top view in two dimensions

Designers generally do layouts to minimize size of circuit subject to design rule constraints (because yield, cost, and performance usually improve)

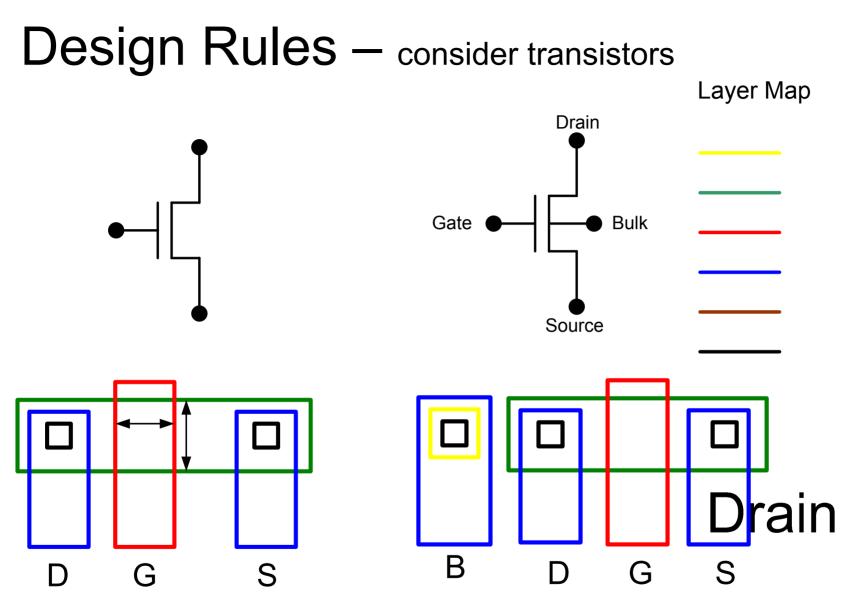

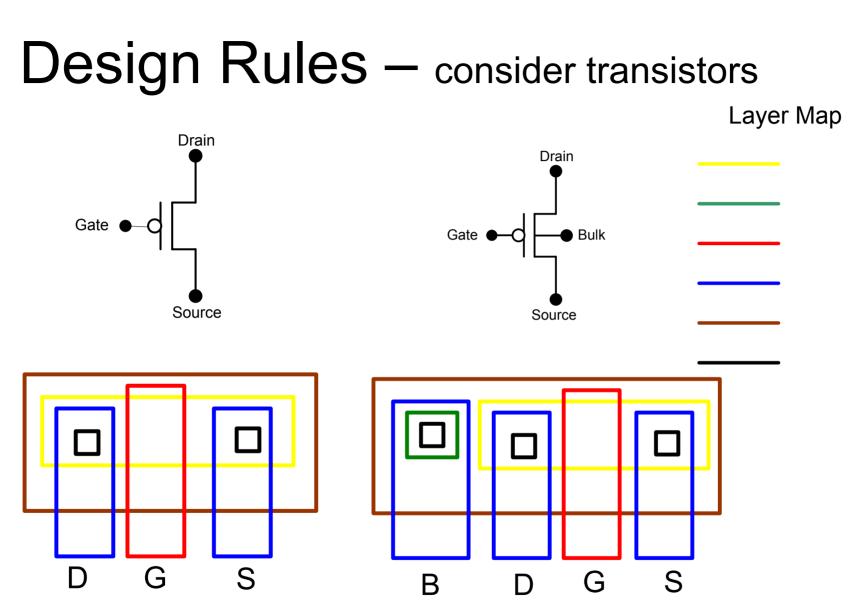

- Bulk connection needed

- Single bulk connection can often be used for several (many) transistors

- Bulk connection needed

- Single bulk connection can often be used for several (many) transistors is they share the same well

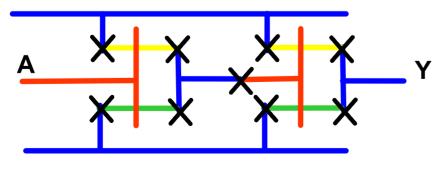

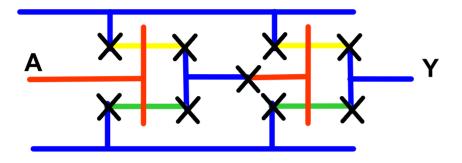

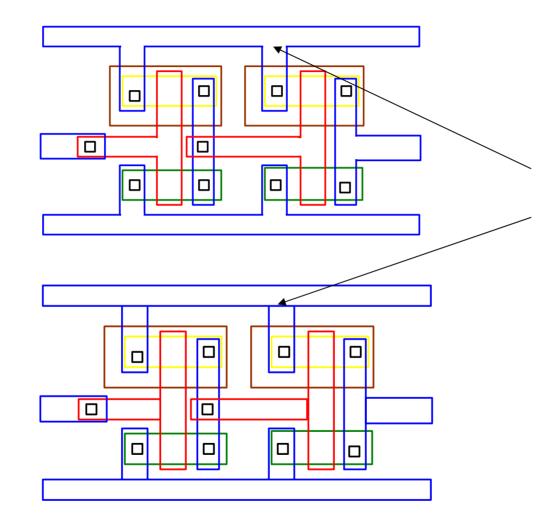

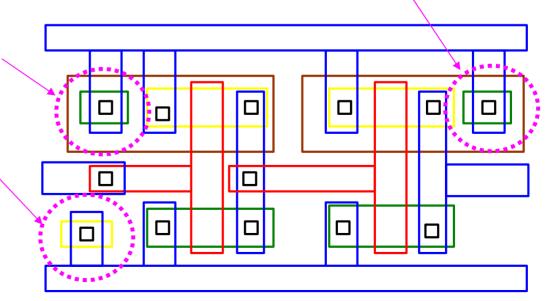

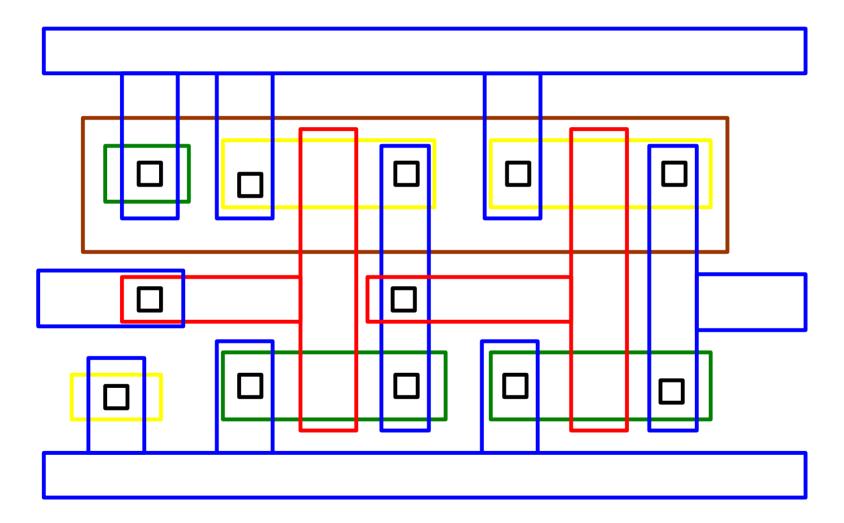

Stick Diagram

Layout

- Polygons merged in Geometric Description File (GDF)

- Separate rectangles generally more convenient to represent

- Design rules must be satisfied throughout the design

- DRC runs incrementally during layout in most existing tools to flag most problems

DRC can catch layout errors but not circuit design errors

What is wrong with this layout ? Bulk connections missing!

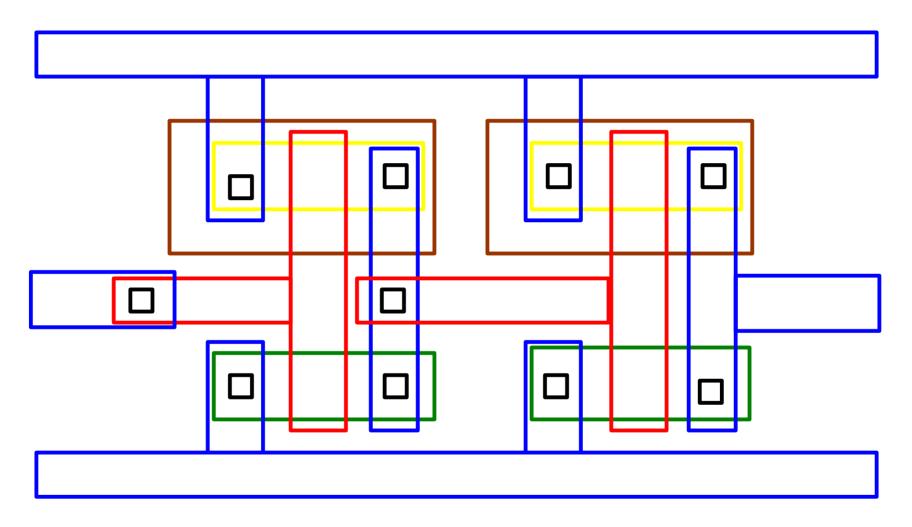

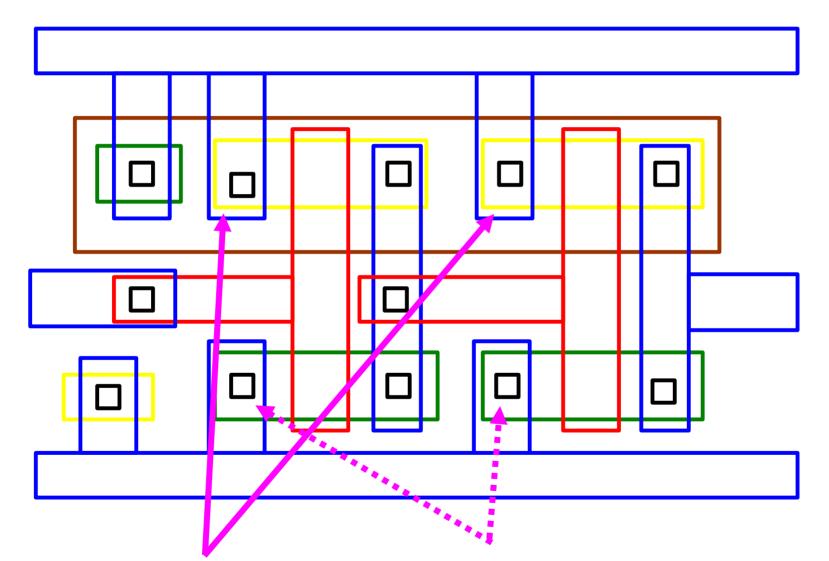

- Note diffusions needed for bulk connections

- Note p-well connections increase area a significant amount

- $\bullet$  Note p-wells are both connected to  $V_{\text{DD}}$  in this circuit

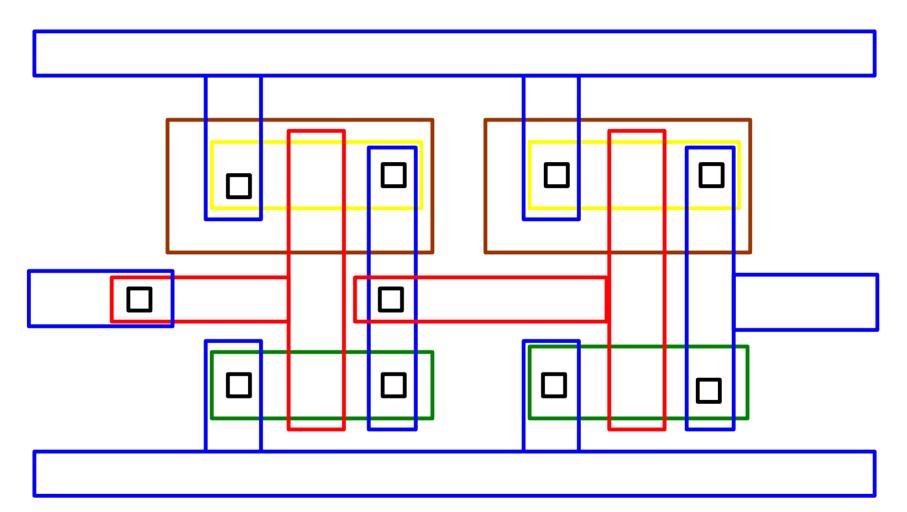

Layout with shared p-well reduces area

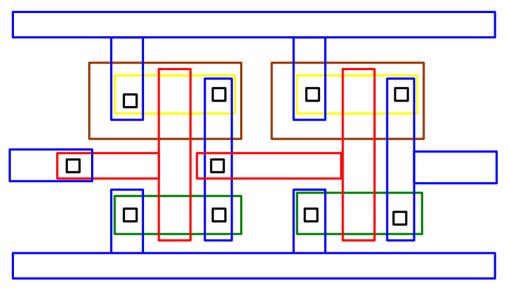

Shared p-active can be combined to reduce area

Shared n-active can be combined to reduce area

- Design rules can be given in absolute dimensions for every rule

- Design rules can be parameterized and given relative to a parameter

- Makes movement from one process to another more convenient

- Easier for designer to remember

- Some penalty in area efficiency

- Often termed  $\lambda$ -based design rules

- Typically  $\lambda$  is  $1\!\!\!/_2$  the minimum feature size in a process

See <u>www.MOSIS.org</u> for design rules

### The MOSIS Service 50,000 designs and more than 20 years of experience

Schedule - Prices - Contacts - About Us - Site Map

#### About MOSIS

What Is MOSIS MOSIS User Group Customer Support Contact MOSIS

#### Products

I.C. Fabrication Request for Quote Packaging, Assembly Design Rule Check Educational Program <u>MEMS</u> 3rd Party Services

#### **Getting Started**

Create Account Select a Process Design a Circuit Send a P.O. Submit a Design

#### **After Submission**

Get Project Status Get Run Status Send a Report Additional Parts

#### Information

Price List Fabrication Schedule Design Rules Design Flows Electrical Parameters Layer Maps Processes Available SPICE Parameters

#### Documents

Proprietary Agreements and Access Requests Academic Institutions

#### Other

Web Forms FAQs

### Welcome to MOSIS

MOSIS is an integrated circuit fabrication service where you can purchase prototype and small-volume production quantities of integrated circuits and related products.

related products. MOSIS lowers the cost of fabrication by combining designs from many customers onto multi-project wafers, thereby significantly decreasing the cost of each design.

| New MOSIS Users                      | Experienced<br>MOSIS Users |

|--------------------------------------|----------------------------|

| Purchasing<br>Agents                 | Design and Test            |

| <u>Educational</u><br><u>Program</u> | Export Program             |

Fabrication Processes

AMIS - austriamicrosytems - IBM - TSMC

All Fabricators

#### Fabrication Schedule

AUG 15: AMI\_ABN AUG 15: TSMC 0.25 AUG 15: IBM 8RF-LM AUG 22: AMI 12T100 AUG 29: TSMC 0.18 AUG 29: AMS S35D4 AUG 29: Ommic GaAS SEP 06: AMI\_C5 SEP 12: IBM 5HP/AM SEP 12: IBM 5HP/AM SEP 12: AMS C35B4

#### Search MOSIS

Search

#### Most Visited Pages

01. <u>Design Rules</u> 02. <u>Price List</u> 03. <u>Schedule</u> 04. <u>Processes</u> 05. <u>Test Data</u> 06. <u>IC Orders</u> 07. <u>About MOSIS</u> 08. <u>Spice FAQ</u> 09. <u>Packaging</u> 10. Design Issues

### The MOSIS Service 50,000 designs and more than 20 years of experience

Schedule - Prices - Contacts - About Us - Site Map

Home --> Design --> Rules

#### About MOSIS

What Is MOSIS MOSIS User Group Customer Support Contact MOSIS

#### Products

I.C. Fabrication Request for Quote Packaging, Assembly Design Rule Check Educational Program MEMS 3rd Party Services

#### **Getting Started**

<u>Create Account</u> <u>Select a Process</u> <u>Design a Circuit</u> <u>Send a P.O.</u> <u>Submit a Design</u>

#### After Submission

Get Project Status Get Run Status Send a Report Additional Parts

#### Information

Price List Fabrication Schedule Design Rules Design Flows Electrical Parameters Layer Maps Processes Available SPICE Parameters

#### Documents

Proprietary Agreements and Access Requests Academic Institutions

#### Other

Web Forms FAQs Projects submitted to MOSIS for fabrication can be designed using either

vendor-independent, scalable rules (MOSIS SCMOS Rules), or design rules specific to a process.

### Vendor and MOSIS SCMOS Design Rules

#### Vendor Rules

Vendors consider their rules, process specifications, and SPICE parameters proprietary and make them available to MOSIS commercial account holders in different ways.

#### SCMOS Rules

MOSIS Scalable CMOS (SCMOS) is a set of logical layers together with their design rules, which provide a nearly process- and metric-independent interface to all CMOS fabrication processes available through MOSIS.

#### Related Links

- Fabrication Schedule

- Customer Support

- MOSIS Products

#### Fabrication Schedule

AUG 15: AMI\_ABN AUG 15: TSMC 0.25 AUG 15: IBM 8RF-LM AUG 22: AMI I2T100 AUG 29: TSMC 0.18 AUG 29: AMS S35D4 AUG 29: Ommic GaAs SEP 06: AMI\_C5 SEP 12: IBM 5HP/AM SEP 12: IBM 5RF-DM SEP 12: AMS C35B4

More...

#### Search MOSIS

Search

#### Most Visited Pages

- 01. Design Rules

- 02. Price List

- 03. Schedule

- 04. Processes

- 05. Test Data

- 06. IC Orders

- 07. About MOSIS

- 08. Spice FAQ

- 09. Packaging

- 10. Design Issues

See <u>www.MOSIS.org</u> for design rules

- Some of these files are on class WEB site

SCMOS Rules Updated Sept 2005.pdf

- Mosis Rules Pictoral.pdf