#### EE 434 Lecture 23

#### Models for Computer Simulation Bipolar Small Signal Device Models

#### Quiz 15

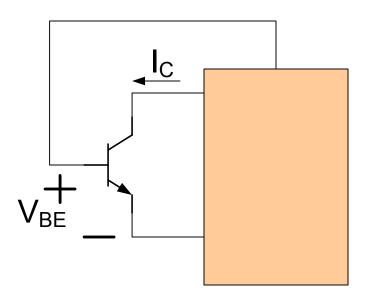

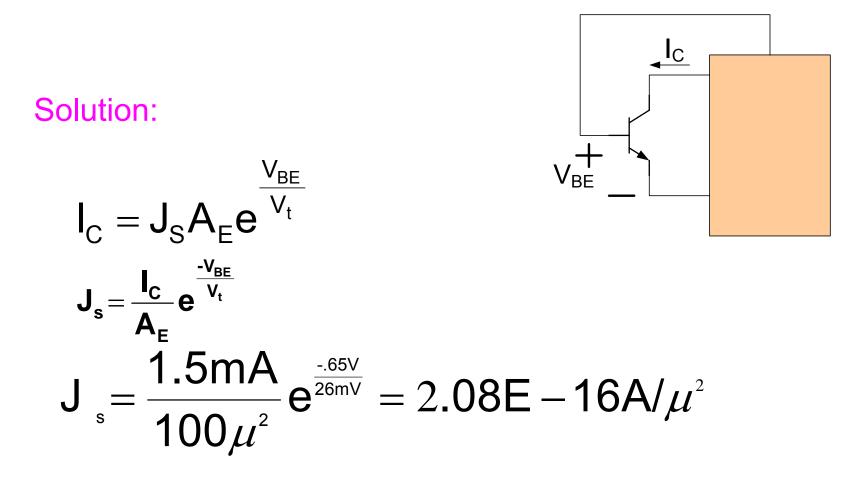

The collector current IC was accurately measured to be 1.5mA and the  $V_{BE}$  was measured to be 0.65V. What is the J<sub>S</sub> for the process if the emitter area is 100u<sup>2</sup>? Assume operation at room temperature.

# And the number is .... 1 <sup>8</sup> <sup>7</sup> 5 3 <sup>6</sup> 9 4 2

# And the number is .... <sup>8</sup> <sup>7</sup> <sup>5</sup> 3 <sup>6</sup> <sup>9</sup> 4 <sup>2</sup>

1

#### Quiz 15

The collector current IC was accurately measured to be 1.5mA and the  $V_{BE}$  was measured to be 0.65V. What is the J<sub>S</sub> for the process if the emitter area is 100u<sup>2</sup>? Assume operation at room temperature.

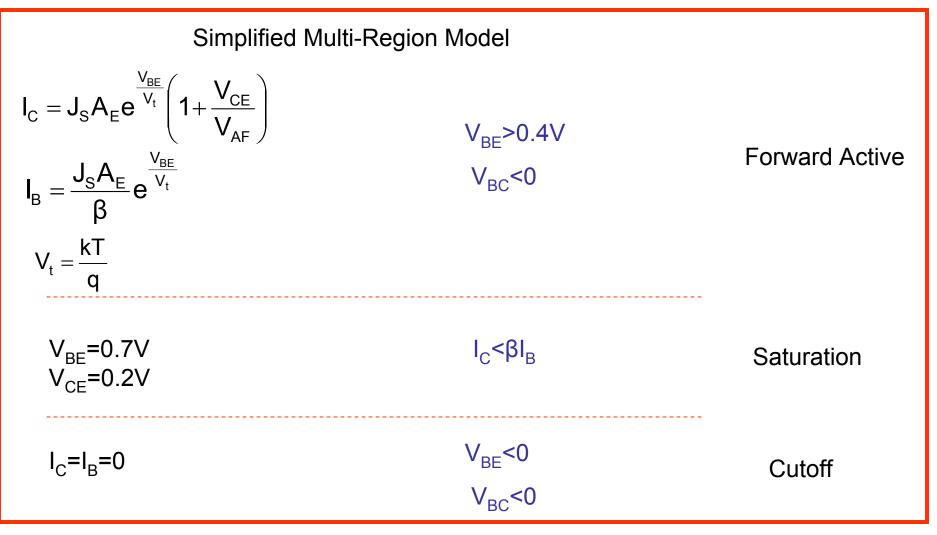

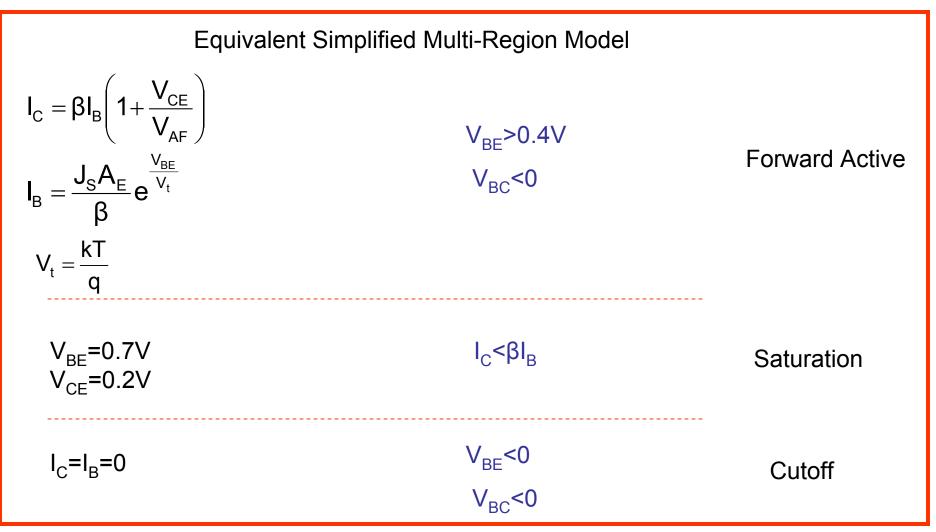

#### Review from Last Time Simple dc model

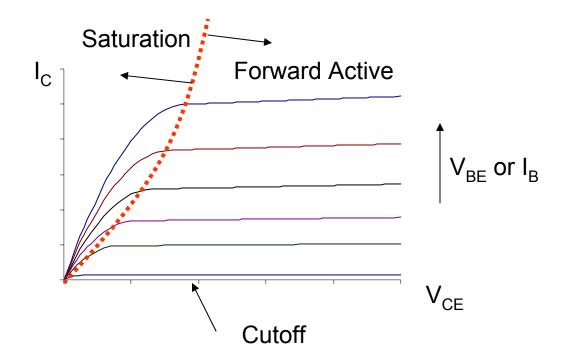

**Typical Output Characteristics**

Forward Active region of BJT is analogous to Saturation region of MOSFET Saturation region of BJT is analogous to Triode region of MOSFET

#### Review from Last Time Improved dc model

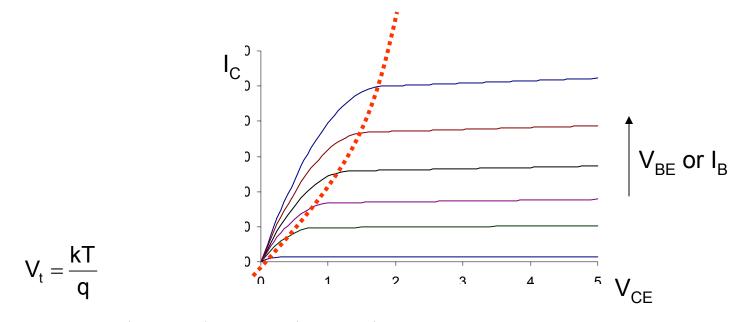

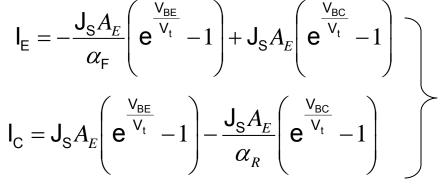

Valid in All regions of operation V<sub>AF</sub> effects can be added Not mathematically easy to work with Note dependent variables changes Termed Ebers-Moll model Reduces to previous model in FA region

#### Review from Last Time

# Simple dc model

A small portion of the operating region is missed with this model but seldom operate in the missing region

#### Review from Last Time Simple dc model

A small portion of the operating region is missed with this model but seldom operate in the missing region

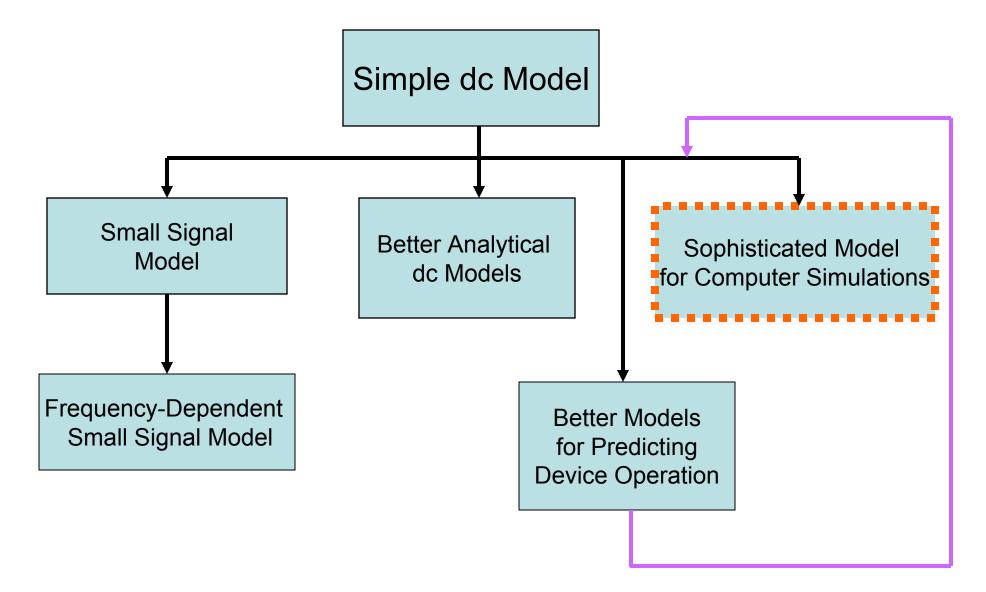

## Models for Computer<sub>G</sub>Simulation

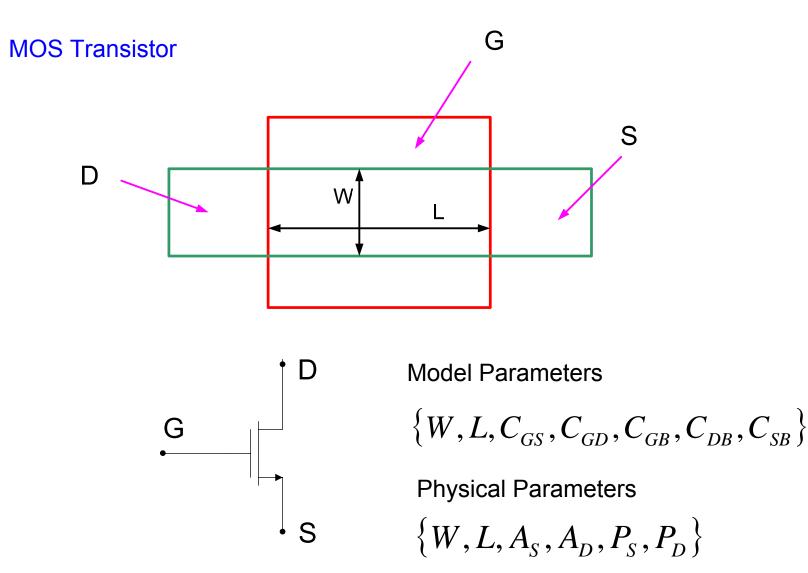

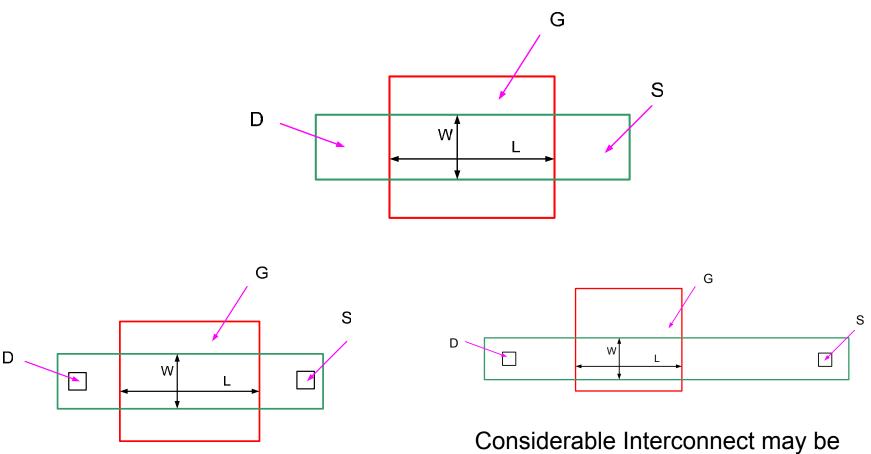

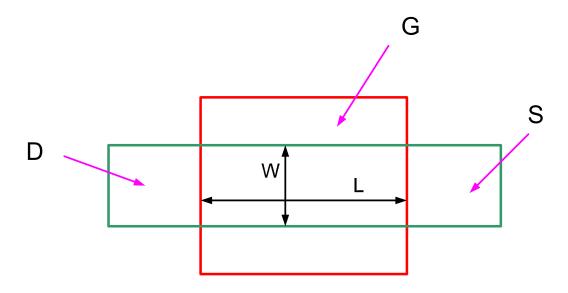

**MOS Transistor**

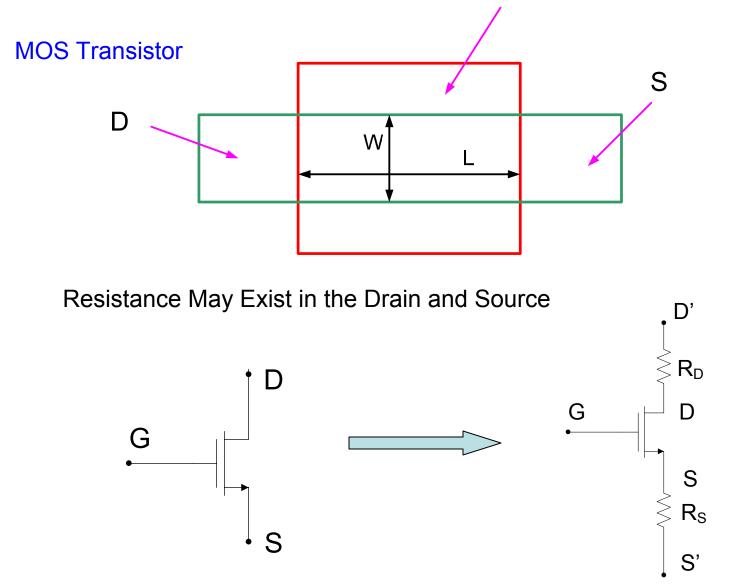

Resistance May Exist in the Drain and Source

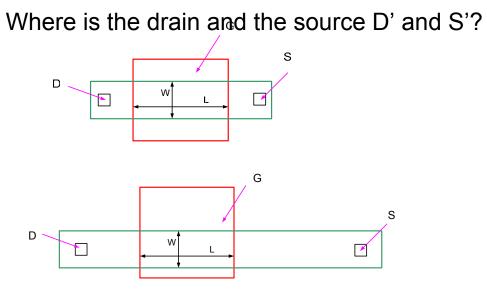

Where is the drain and the source D' and S'?

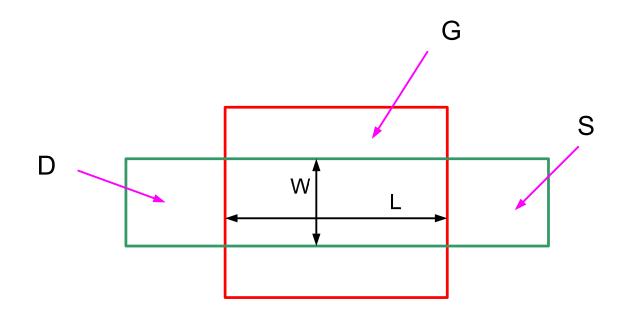

MOS Transistor

Where is the drain and the source D' and S'?

MOS Transistor

Where is the drain and the source D' and S'?

made with diffusions

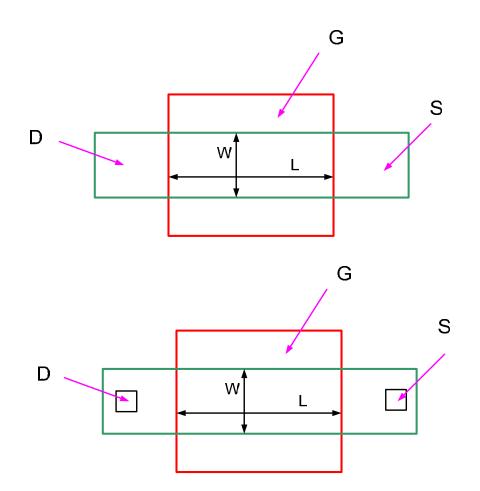

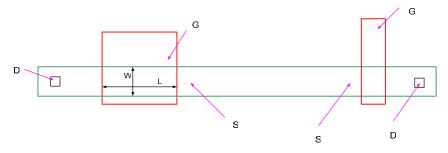

MOS Transistor

Considerable Interconnect may be made with diffusions

Drain and source boundary assignments is not unique !!

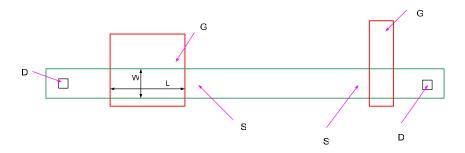

MOS Transistor

Where is the drain and the source D' and S'?

Drain and source boundary assignments is not unique !!

So, how are boundary assignments made?

However you want !!

But eventually must either include all parasitics as either part of devices or as parts of interconnects

#### **MOS Transistor**

**Model Parameters**

$$\{W, L, R_S, R_D, C_{GS}, C_{GD}, C_{GB}, C_{DB}, C_{SB}\}$$

**Physical Parameters**

$$\left\{W, L, N_{RS}, N_{RD}, A_{S}, A_{D}, P_{S}, P_{D}\right\}$$

MOS Transistor Models for SImulation

**Physical Parameters**

$$\left\{W, L, N_{RS}, N_{RD}, A_{S}, A_{D}, P_{S}, P_{D}\right\}$$

- Separate Process Part of Model from Instantiation part of Model

- Use one Process File for Entire Process and Specify only Physical Geometric Parameters for Each Device

MOS Transistor Models for SImulation

**Physical Parameters**

$$\left\{W, L, N_{RS}, N_{RD}, A_{S}, A_{D}, P_{S}, P_{D}\right\}$$

MOS Models for Simulation Level 1 Level 2 Level 3 BSIM 3 BSIM 4 PSP

Hierarchy Used in Models