# EE 434 Lecture 34

Logic Design

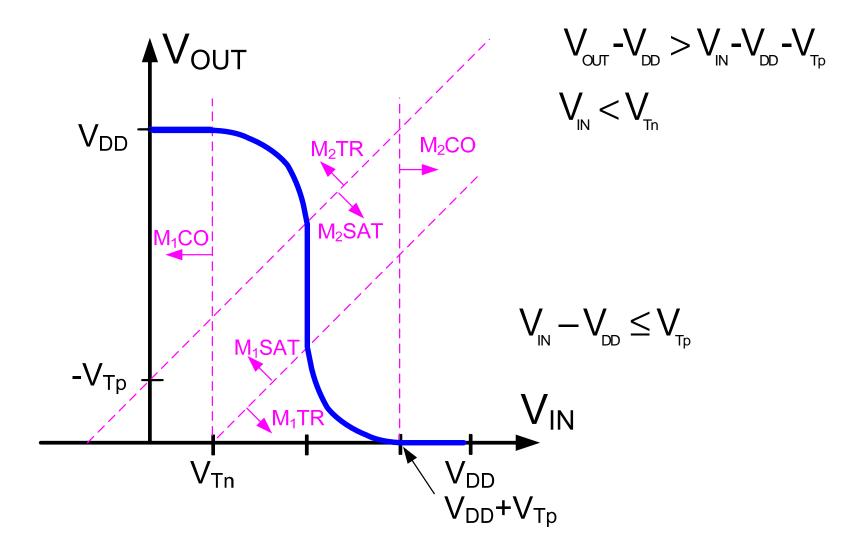

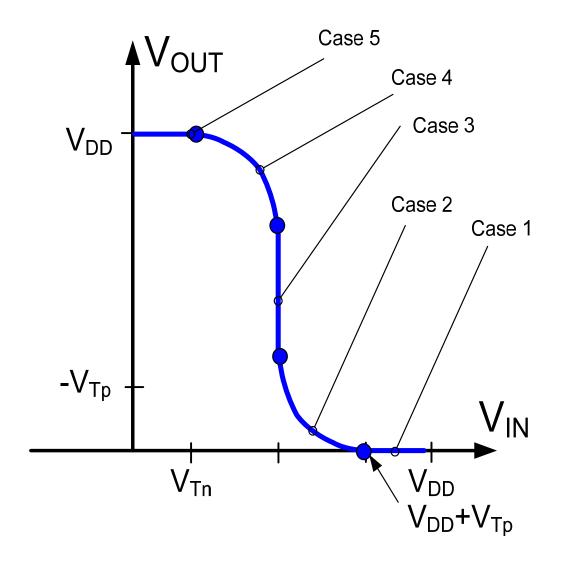

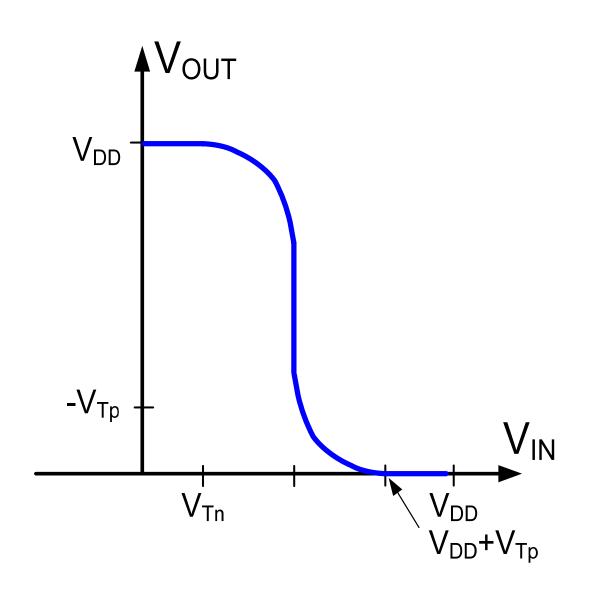

# Transfer characteristics of the static CMOS inverter (Neglect λ effects)

Case 5  $M_1$  cutoff,  $M_2$  triode

# Transfer characteristics of the static CMOS inverter (Neglect λ effects)

Transfer characteristics of the static CMOS inverter (Neglect λ effects)

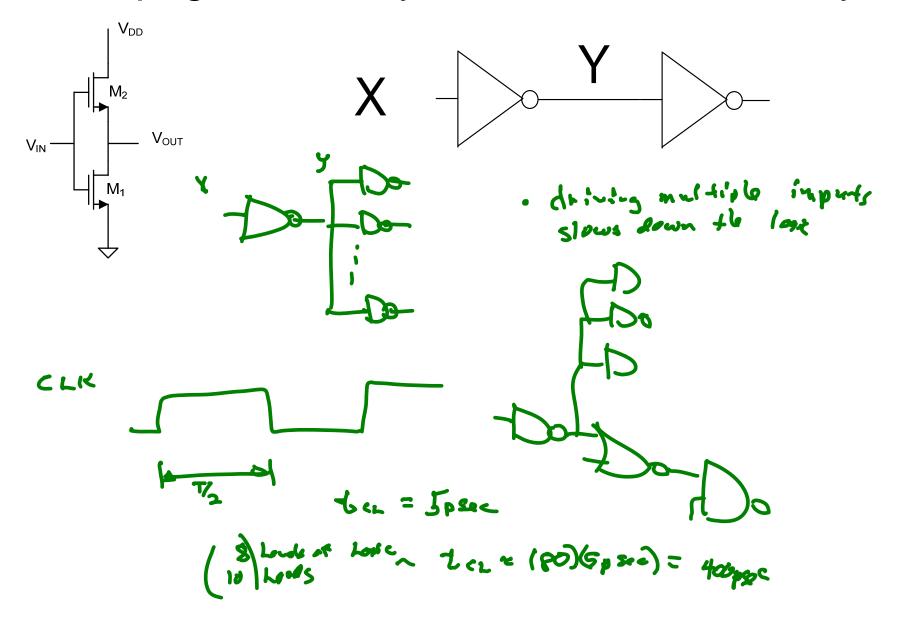

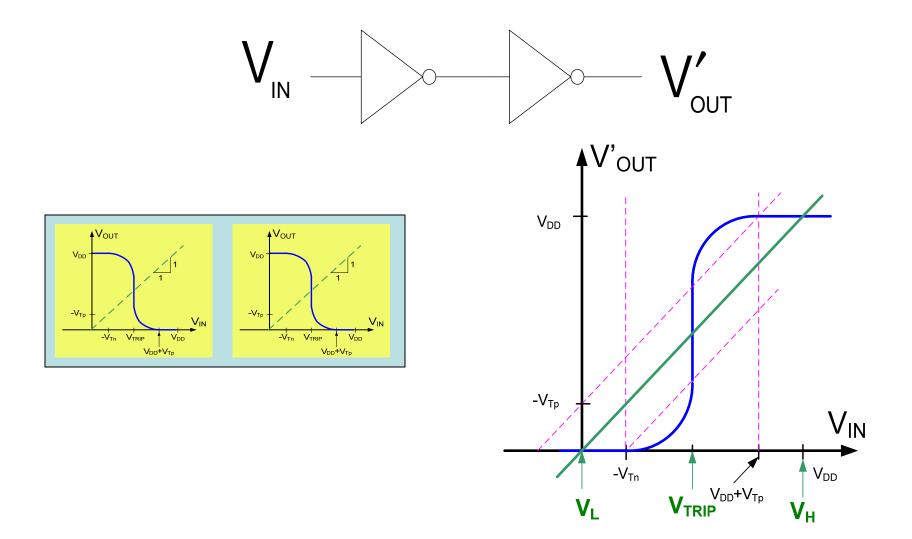

## Review from last time: Inverter Transfer Characteristics of Inverter Pair

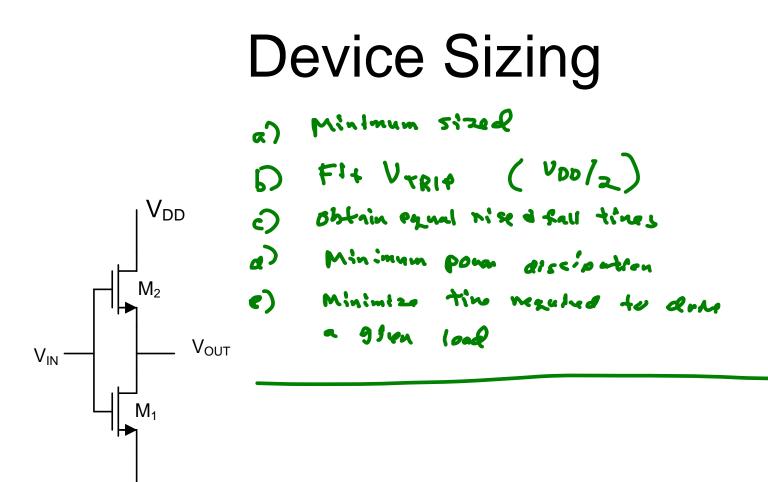

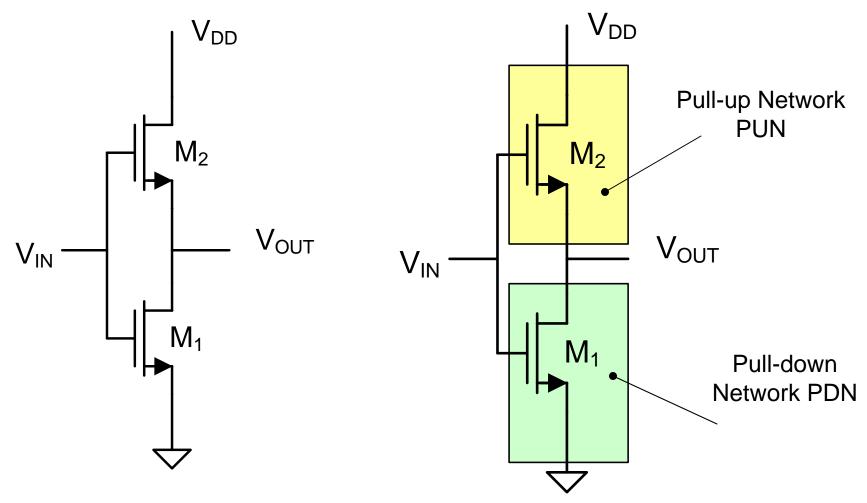

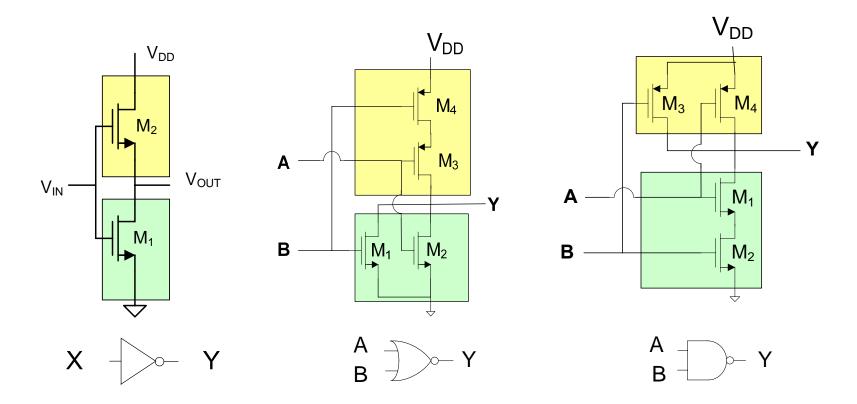

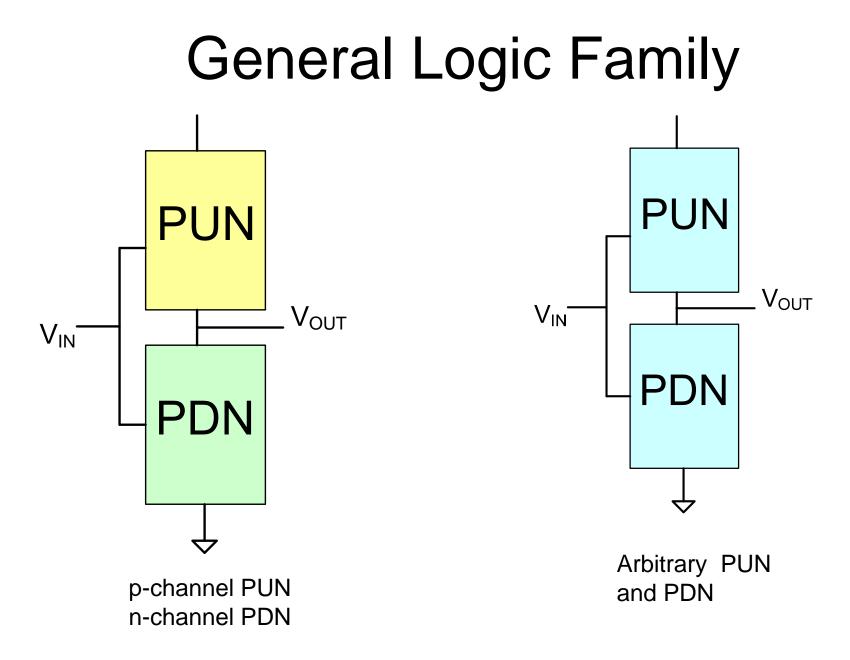

# Static CMOS Logic Family

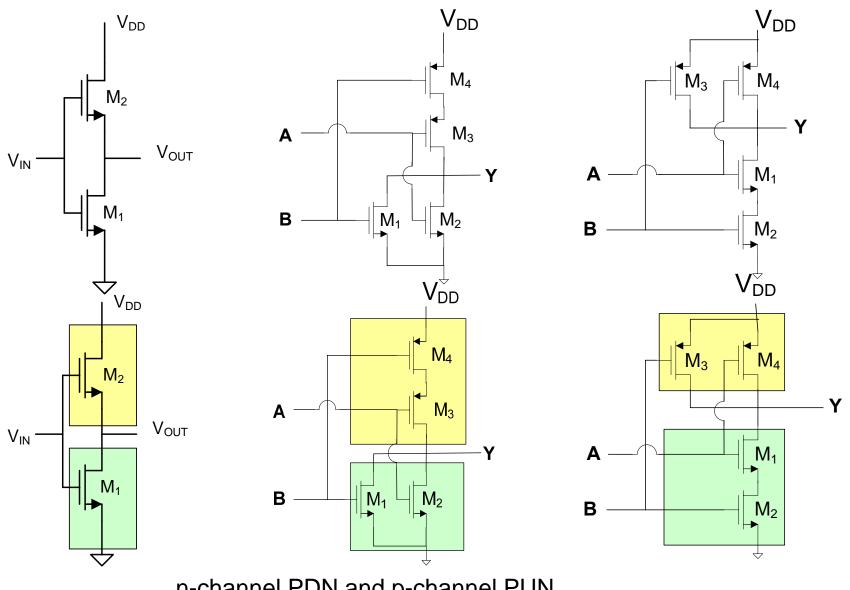

Observe PUN is p-channel, PDN is n-channel

Static CMOS Logic Family

n-channel PDN and p-channel PUN

## Static CMOS Logic Family

- Any number of inputs can be added to NAND or NOR Gates

- NAND and NOR Logic Families are Complete

- Can now build ANY combinational logic function !

# **Other CMOS Logic Families**

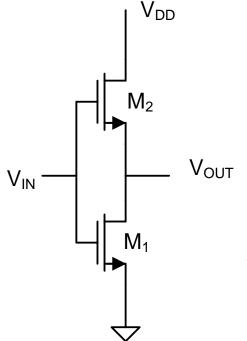

## Static Power Dissipation in Static CMOS Family

When  $V_{OUT}$  is Low,  $I_{D1}=0$

When  $V_{OUT}$  is High,  $I_{D2}=0$

Thus, P<sub>STATIC</sub>=0

This is a key property of the static CMOS Logic Family and is the major reason Static CMOS Logic is so dominant

It can be shown that this zero static power dissipation property can be preserved if the PUN is comprised of n-channel devices, the PDN is comprised of n-channel devices and they are never both driven into the conducting states at the same time

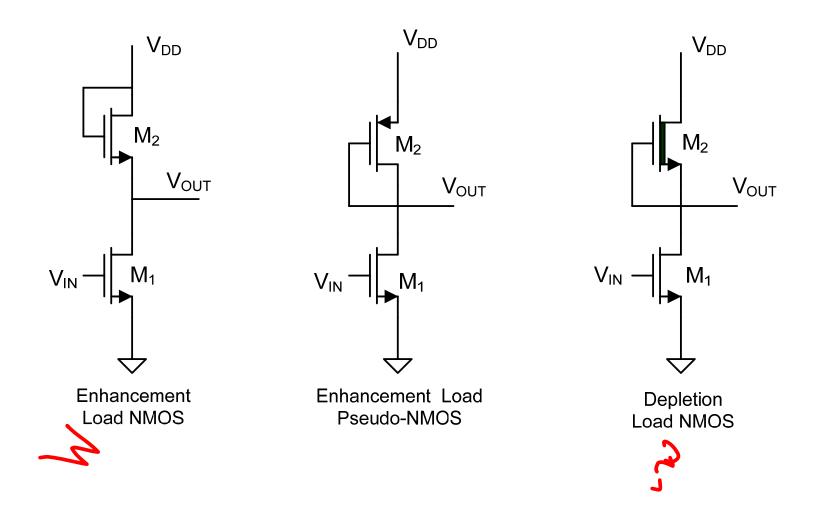

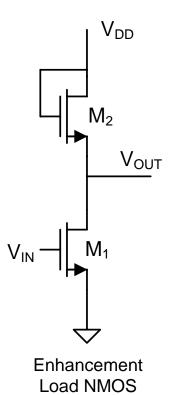

## Static Power Dissipation in Ratio Logic Families

Example:

Assume V<sub>DD</sub>=5V V<sub>T</sub>=1V,  $\mu C_{OX}$ =10<sup>-4</sup>A/V<sup>2</sup>, W<sub>1</sub>/L<sub>1</sub>=1 and M<sub>2</sub> sized so that V<sub>L</sub>=V<sub>Tn</sub>

P<sub>L</sub>=(5V)(0.25mA)=1.25mW

If a circuit has 100,000 gates and half of them are in the  $V_{OUT}=V_L$  state, the static power dissipation will be

$$P_{STATIC} = \frac{1}{2} 10^5 \bullet 1.25 mW = 62.5W$$

This power dissipation is way too high and would be even larger in circuits with 100 million or more gates – the level of integration common in SoC circuits today

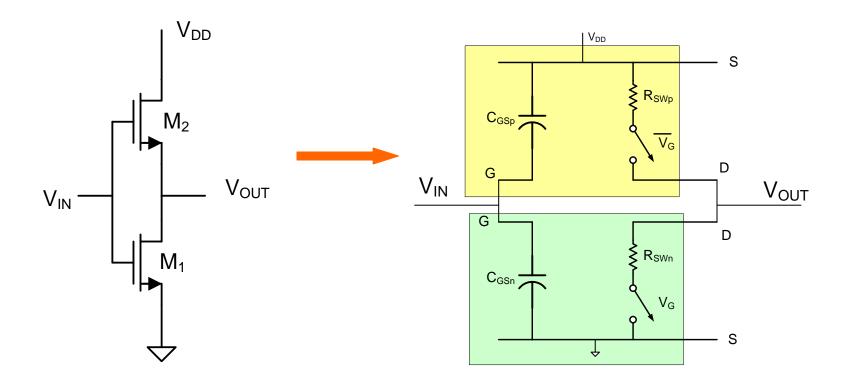

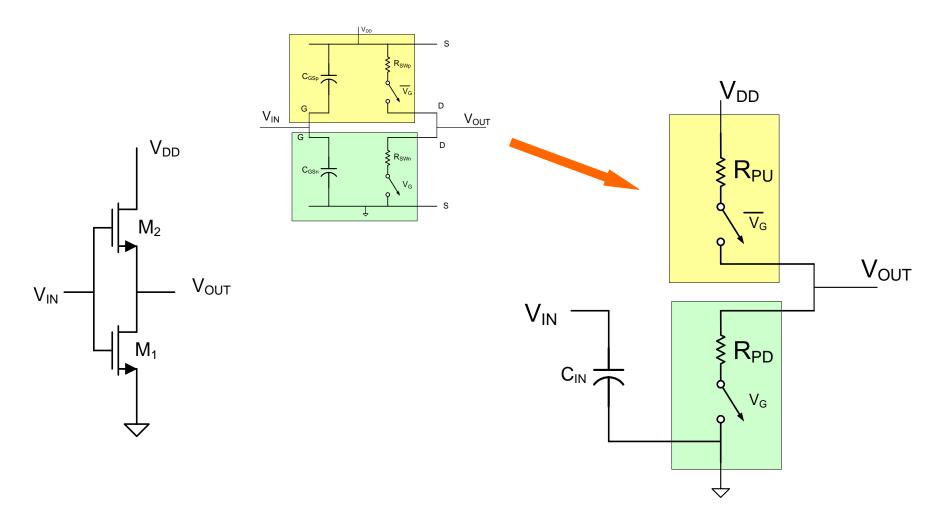

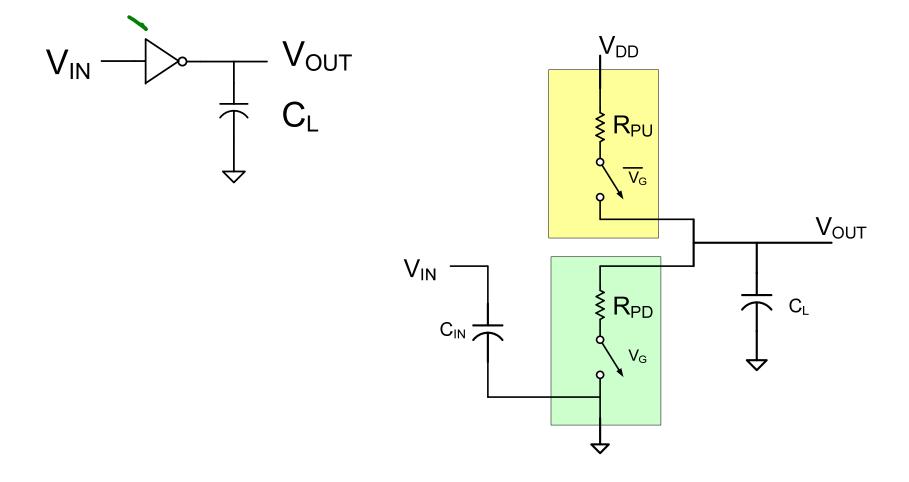

## Propagation Delay in Static CMOS Family

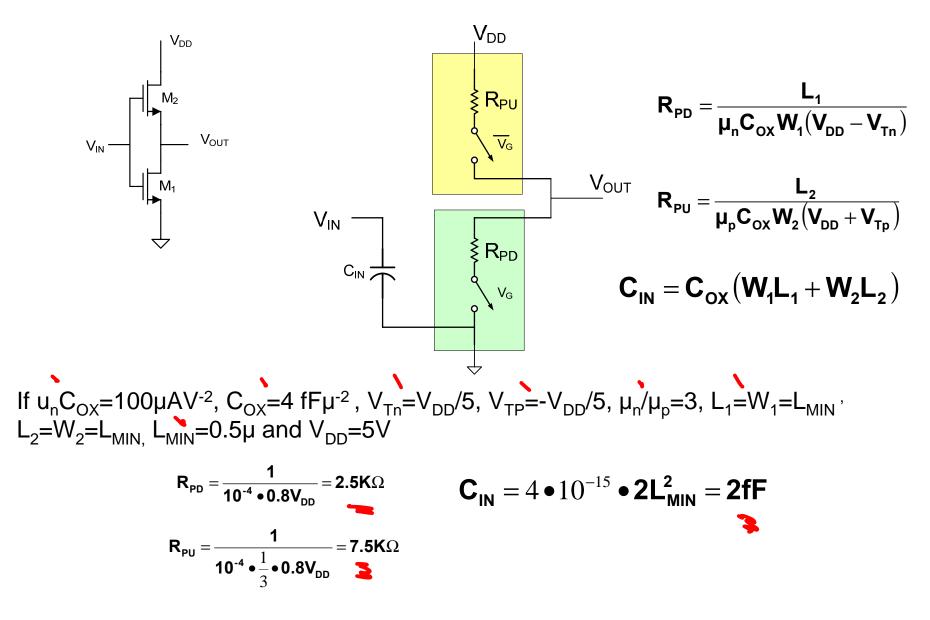

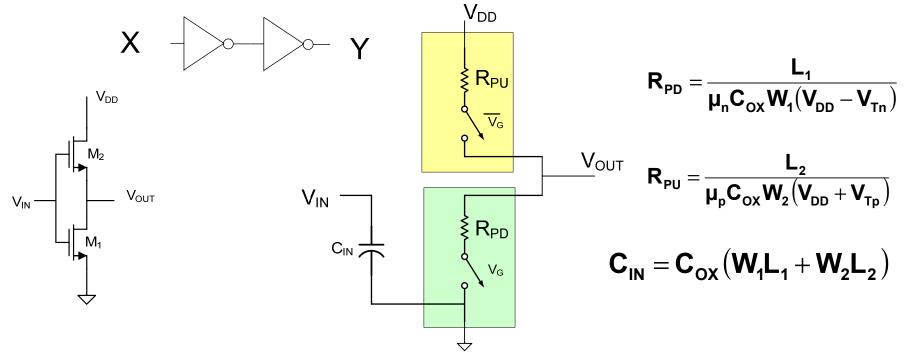

Switch-level model of Static CMOS inverter (neglecting diffusion parasitics)

## Propagation Delay in Static CMOS Family

Switch-level model of Static CMOS inverter (neglecting diffusion parasitics)

If  $u_n C_{OX} = 100 \mu AV^{-2}$ ,  $C_{OX} = 4 \text{ fF} \mu^{-2}$ ,  $V_{Tn} = V_{DD}/5$ ,  $V_{TP} = -V_{DD}/5$ ,  $\mu_n/\mu_p = 3$ ,  $L_1 = W_1 = L_{MIN}$ ,  $L_2 = W_2 = L_{MIN}$ ,  $L_{MIN} = 0.5 \mu$  and  $V_{DD} = 5V$

$$R_{PD} = \frac{1}{10^{-4} \cdot 0.8V_{DD}} = 2.5K\Omega$$

$$C_{IN} = 4 \cdot 10^{-15} \cdot 2L_{MIN}^{2} = 2fF$$

$$R_{PU} = \frac{1}{10^{-4} \cdot \frac{1}{3} \cdot 0.8V_{DD}} = 7.5K\Omega$$

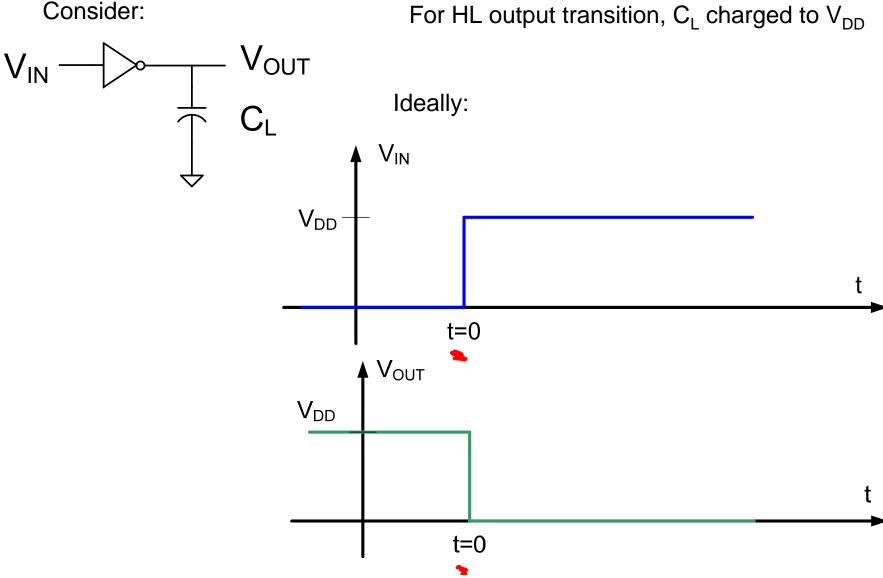

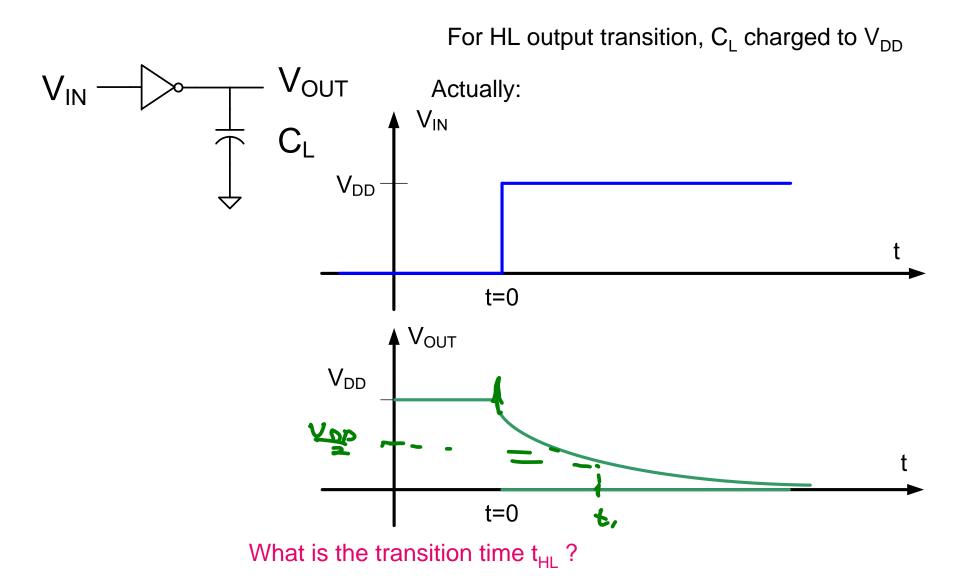

Consider:

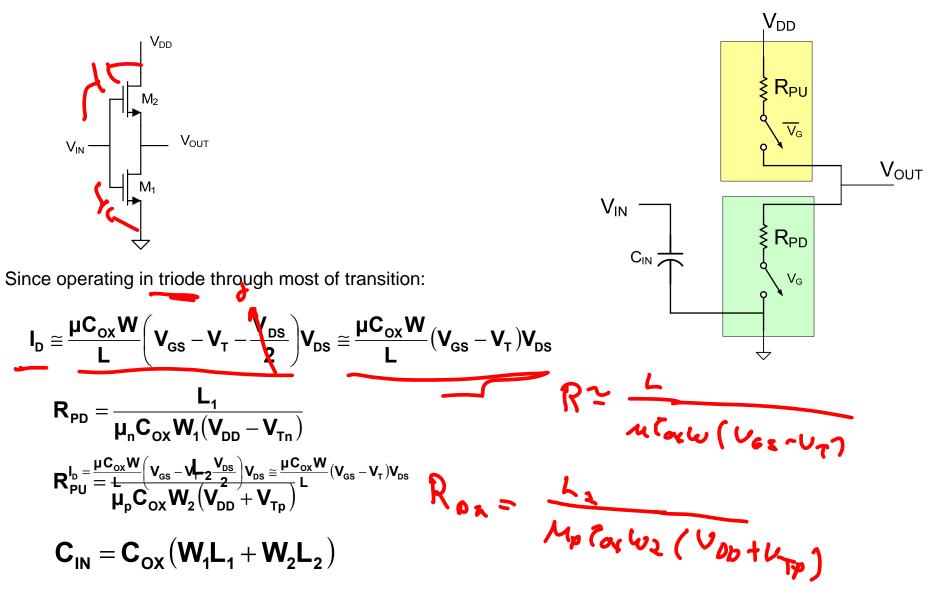

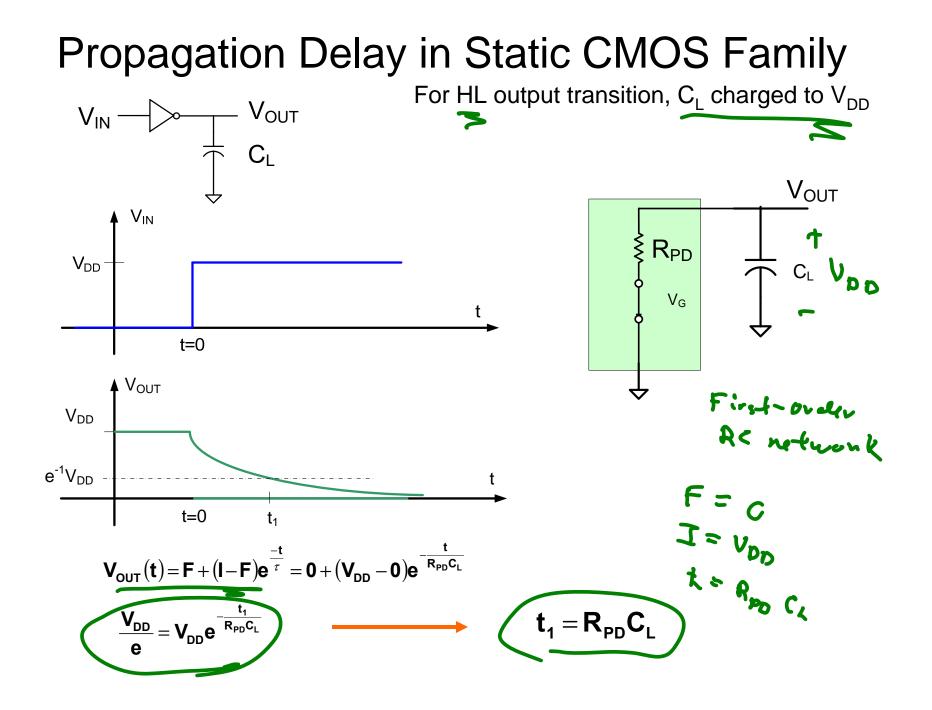

#### Propagation Delay in Static CMOS Family For HL output transition, $C_L$ charged to $V_{DD}$ −−−− V<sub>OUT</sub> ↑ C<sub>L</sub> $V_{\text{OUT}}$ $V_{IN}$ ξ $R_{\text{PD}}$ $V_{DD}$ T <sup>C∟</sup> $V_{G}$ t t=0 V<sub>OUT</sub> $\Rightarrow$ $V_{DD}$ $e^{-1}V_{DD}$ t=0 t<sub>1</sub> $\mathbf{t}_{\mathsf{HL}} \cong \mathbf{R}_{\mathsf{PD}}\mathbf{C}_{\mathsf{L}}$ > $\mathbf{t}_{\mathsf{LH}} \cong \mathbf{R}_{\mathsf{PU}}\mathbf{C}_{\mathsf{L}}$ tHL = O ROOCL 0=1

$V_{IN} = V_{OUT}$   $V_{IN} = R_{PS} C_{L}$   $V_{IN} = R_{PS} C_{L}$  $C_{L} = C_{IN} = (o_{Y}(w, L_{1} + w_{2}, L_{2}))$ = (2.5K) (2 FF) = 5ps -6 HL = ?  $t_{LH} = R_{PH} (L)$  = (1.5K)(2FF) = 15psec  $t_{CL} = t_{HL} + t_{LH} = 20psec$ -6-4 = ? If al mainan 51 ......

= fin = 20 CH2