#### Propagation Delay in Logic Circuits

# **Device Sizing**

**Sizing Strategies**

- Minimum Size

- Fixed  $V_{TRIP}$

- Equal rise-fall times (equal worst-case rise and fall times)

- Minimum power dissipation

- Minimum time required to drive a given load

- Minimum input capacitance

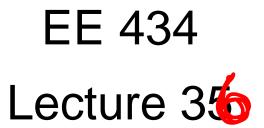

4 design variables  $\{W_1, W_2, L_1, L_2\}$ Invariably will select  $L_1 = L_2 = L_{MIN}$ 2 degrees of freedom  $\{W_1, W_2\}$

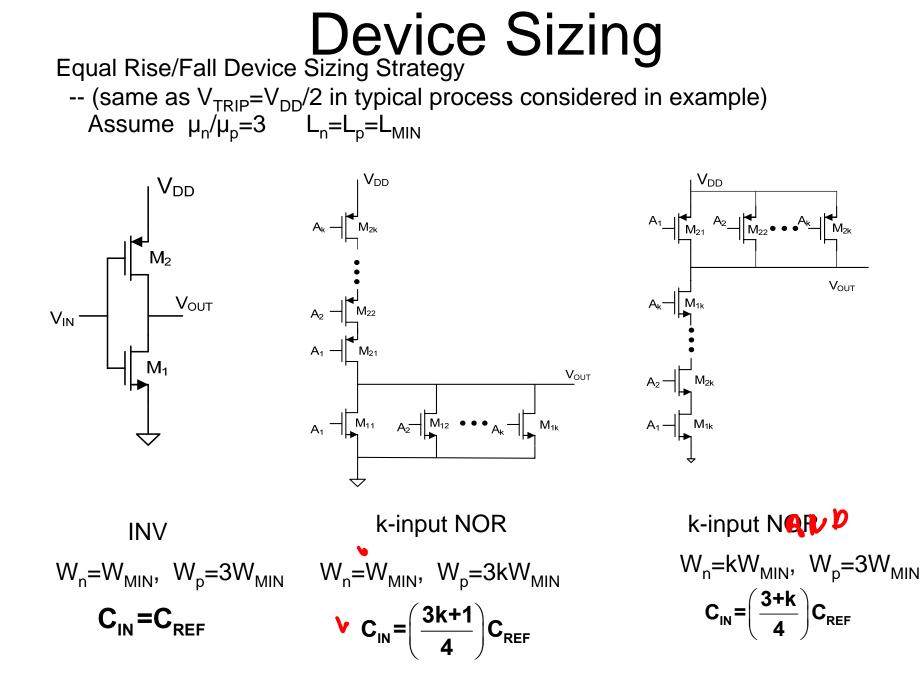

### **Device Sizing**

Equal Rise/Fall Device Sizing Strategy

-- (same as  $V_{TRIP} = V_{DD}/2$  in typical process considered in example)

$V_{IN}$

## Device Sizing

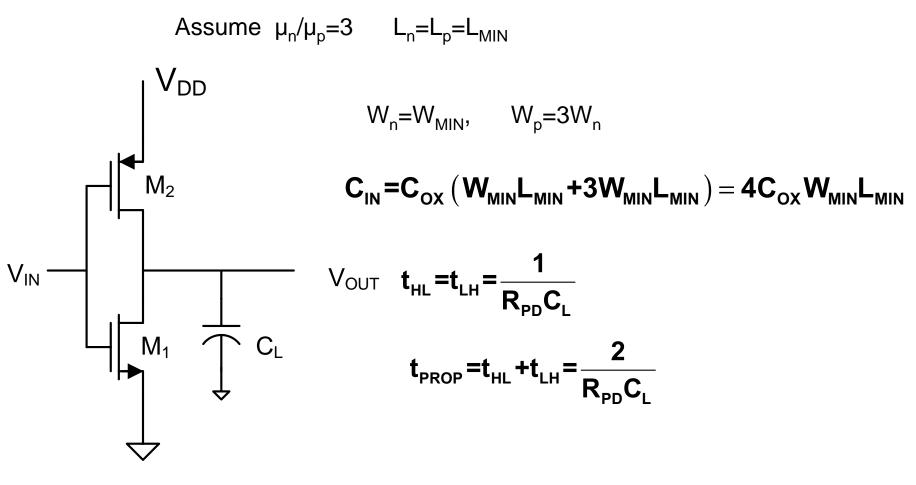

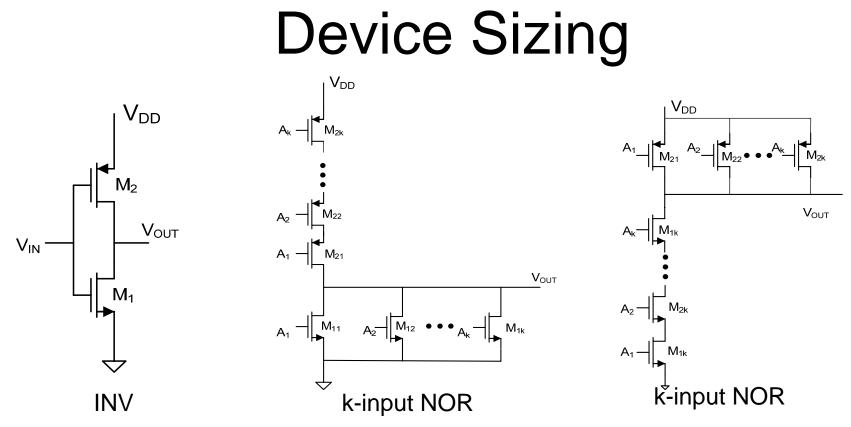

The reference inverter

# **Device Sizing**

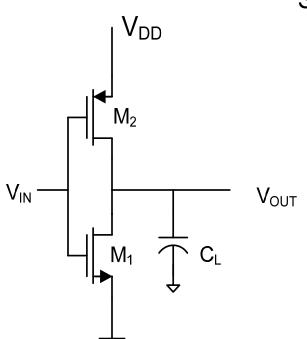

The reference inverter pair Assume  $\mu_n/\mu_p=3$   $L_n=L_p=L_{MIN}$   $W_n=W_{MIN}$ ,  $W_p=3W_n$  $\begin{array}{c} & \begin{array}{c} & & \\ & M_2 \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ &$ V<sub>IN</sub> –  $\mathbf{R}_{PDREF} = \frac{L_{MIN}}{\mu_{n}C_{OX}W_{MIN}(V_{DD} - V_{Tn})} \stackrel{V_{Tn} = .2V_{DD}}{=} \frac{L_{MIN}}{\mu_{n}C_{OX}W_{MIN}(0.8V_{DD})}$  $t_{REF} = t_{HLREF} + t_{LHREF} = \frac{2}{R_{PDRFF}C_{RFF}}$  $C_{IN} = C_{RFF} = 4C_{OX}W_{MIN}L_{MIN}$

$C_{\rm IN}$  for  $N_{\rm AND}$  gates is considerably smaller than for NOR gates for equal worst-case rise and fall times

$C_{IN}$  for minimulm-sized structures is independent of number of inputs and much smaller than CIN for the equal rise/fall time case  $R_{PU}$  gets very large for minimum-sized NOR gate

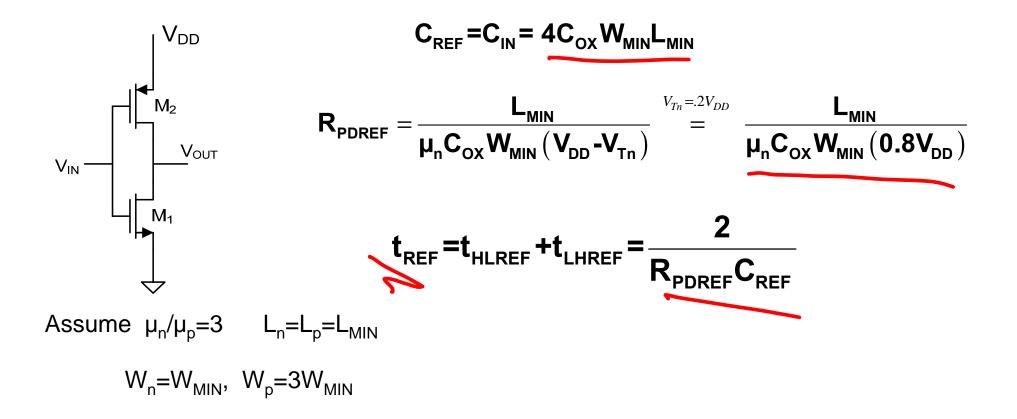

Analysis strategy : Express delays in terms of those of reference inverter

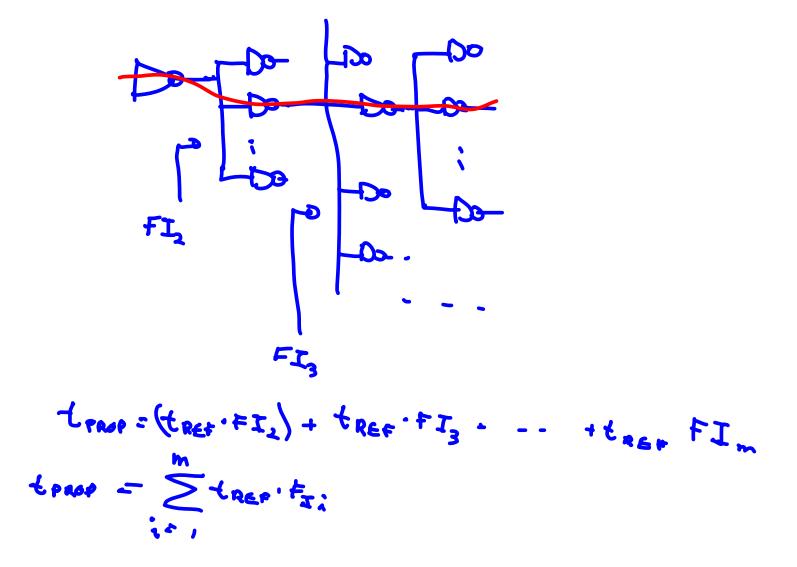

Assume m is even  $\frac{1}{1} + \frac{1}{1} + \frac{1}{1$

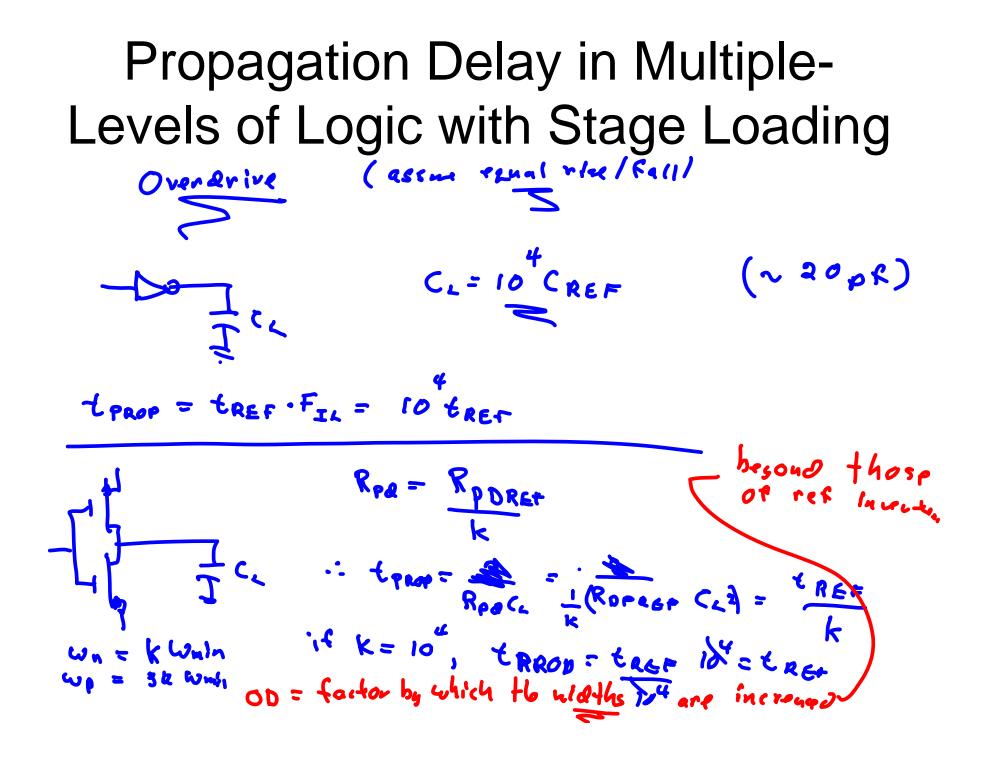

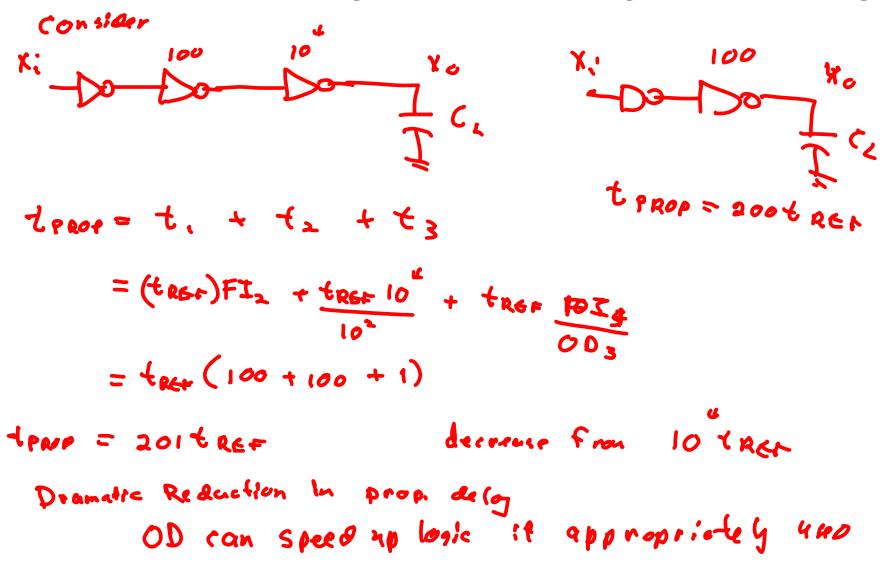

Propagation Delay in Multiple-Levels of Logic with Stage Loading an OD factor of K will Decrease the delay by a factor of K ! (:) but: may have a problem Quiving the Invorter with a large 00 すら OD Lenoe = last · FI2 + Last . FI 34 FI = 104 00=10" = 10 tref + tref  $= t_{REF}(1+10^4)$ slight in prop. delay

- How many chacos !

- How much OD on each stap

- · Extremely big W/L natios proceed when very large OD

- but almost always justifiqble when speck Anstations and present

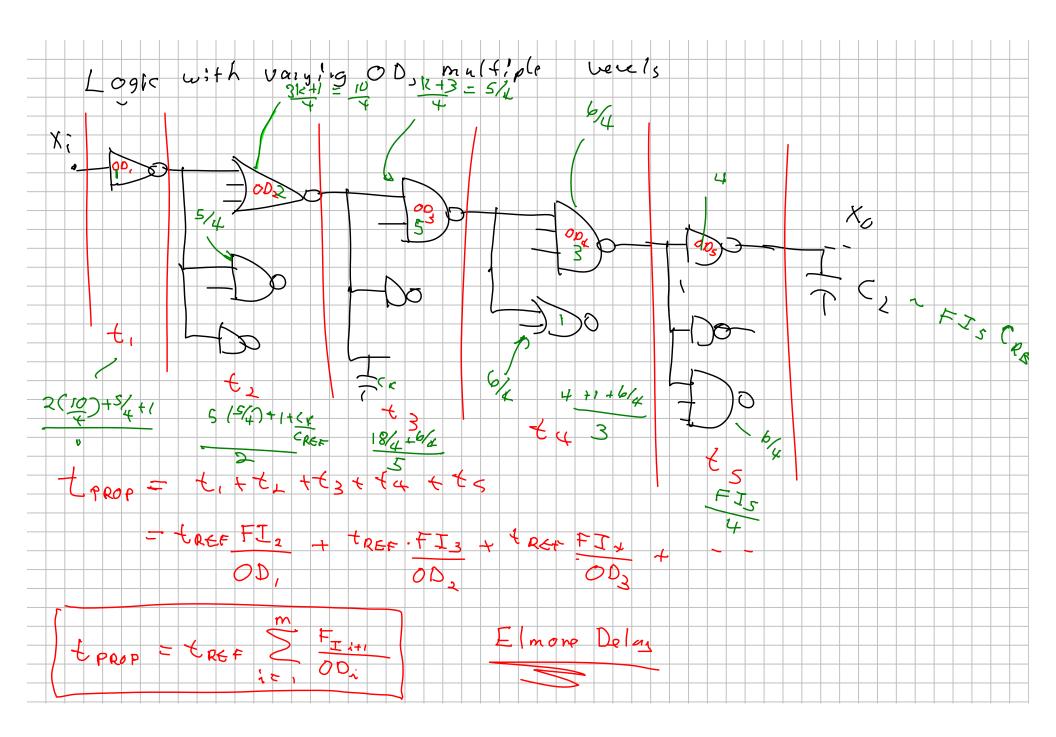

OD sizing for NAND NOR Galos. - For an OD of h on a NAND or NOR Gelp (assuming equal rise (Fail times)