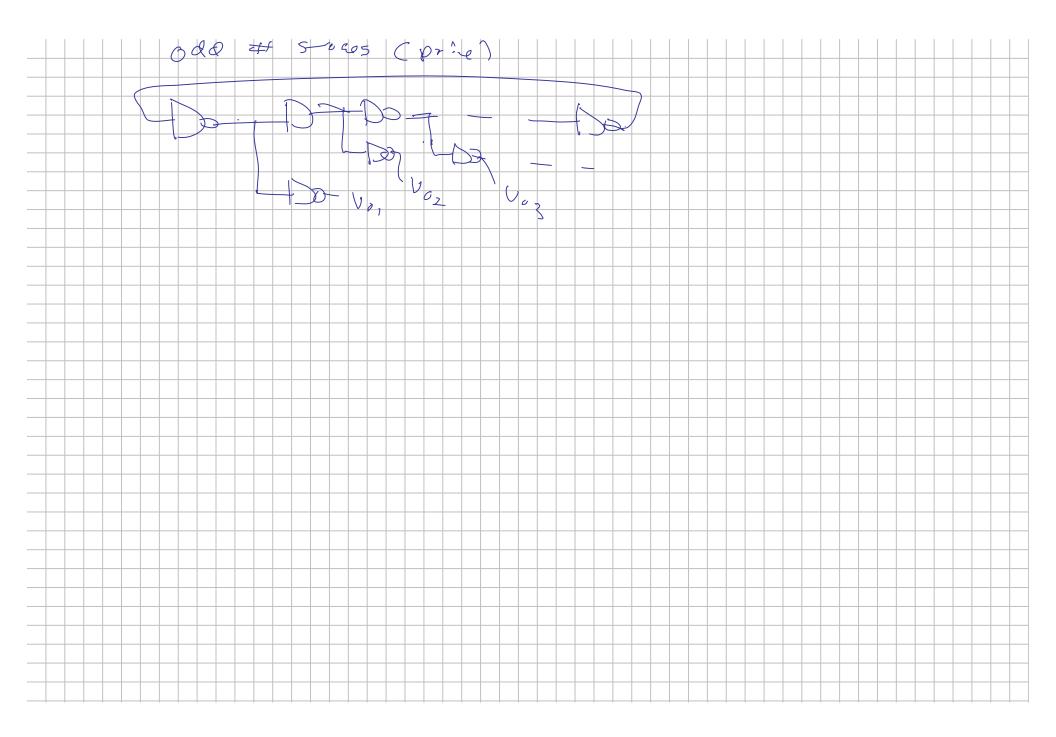

# EE 434 Lecture 38

Propagation Delay in Logic Circuits Power Dissipation Review from last time

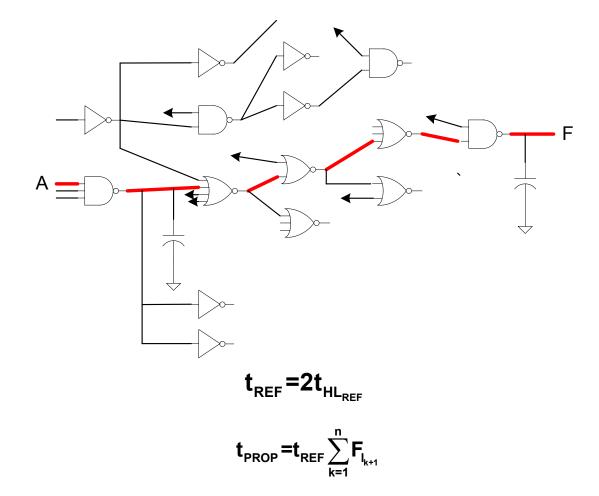

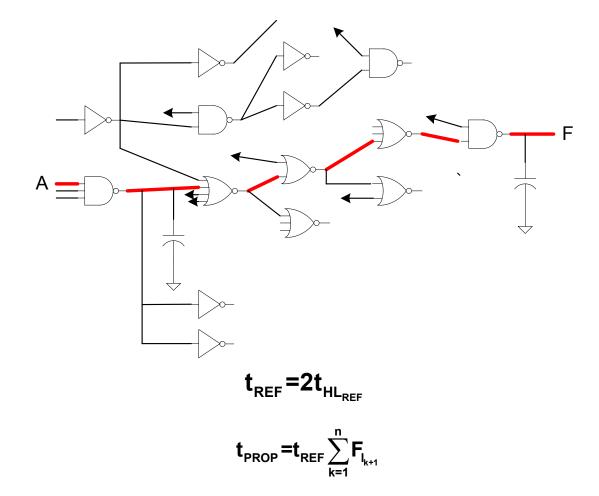

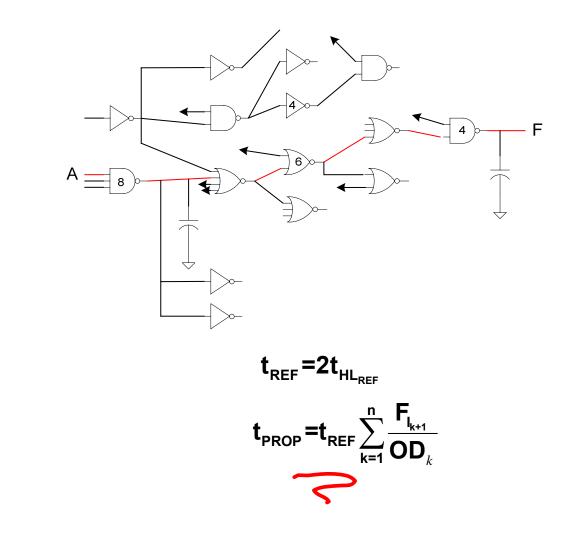

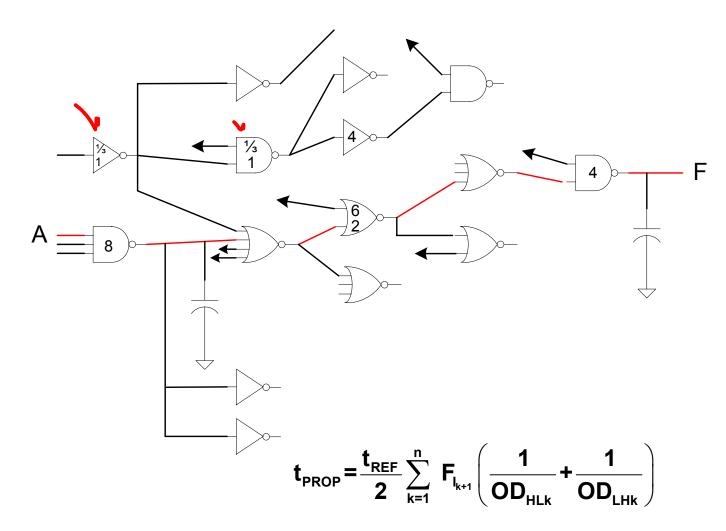

### Propagation Delay in Multiple-Levels of Logic with Stage Loading

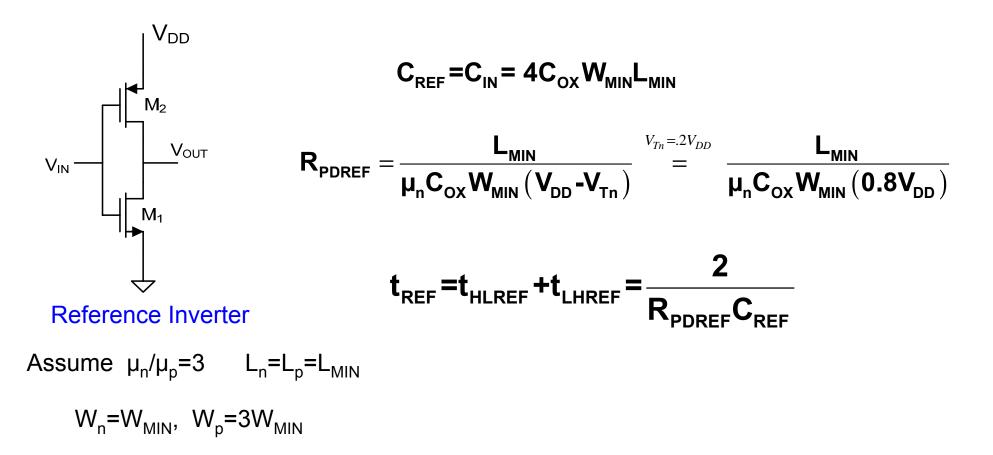

Analysis strategy : Express delays in terms of those of reference inverter

#### Review from last time Propagation Delay in Multiple-Levels of Logic with Stage Loading

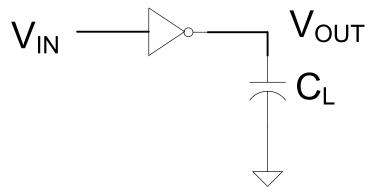

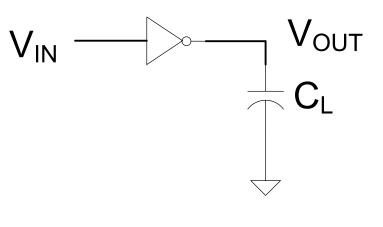

Capacitive Loading

Define the Fan In loading on the stage to be the total capacitive load on the stage normalized to  $\rm C_{REF}$

$$\mathsf{F}_{\mathsf{IL}} = \frac{\mathsf{C}_{\mathsf{L}}}{\mathsf{C}_{\mathsf{REF}}}$$

If inverter sized for equal rise/fall

$$\mathbf{t}_{\mathsf{HL}} = \mathbf{t}_{\mathsf{LH}} = \mathbf{R}_{\mathsf{PD}} \mathbf{C}_{\mathsf{L}} = \mathbf{R}_{\mathsf{PD}} \mathbf{C}_{\mathsf{REF}} \mathbf{F}_{\mathsf{IL}}$$

$$t_{PROP} = t_{LH} + t_{HL} = 2 R_{PD} C_{REF} F_{IL}$$

If inverter is the reference inverter

#### Review from last time Propagation Delay in Multiple-Levels of Logic with Stage Loading

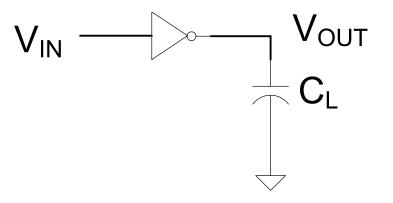

Overdrive

Define the Overdrive Factor of the stage to be the factor by which PU and PD resistors are scaled relative to those of the reference inverter.

$$R_{PDEFF} = \frac{R_{PDREF}}{OD_{HL}} \qquad R_{PUEFF} = \frac{R_{PUREF}}{OD_{LH}}$$

If inverter sized for equal rise/fall,  $OD_{HL} = OD_{LH} = OD$

$$t_{HL} = t_{LH} = \frac{R_{PDREF}}{OD} C_{L} = R_{PDREF} C_{REF} \frac{F_{IL}}{OD}$$

$$t_{PROP} = t_{LH} + t_{HL} = t_{REF} \frac{F_{IL}}{OD}$$

OD may be larger or smaller than 1

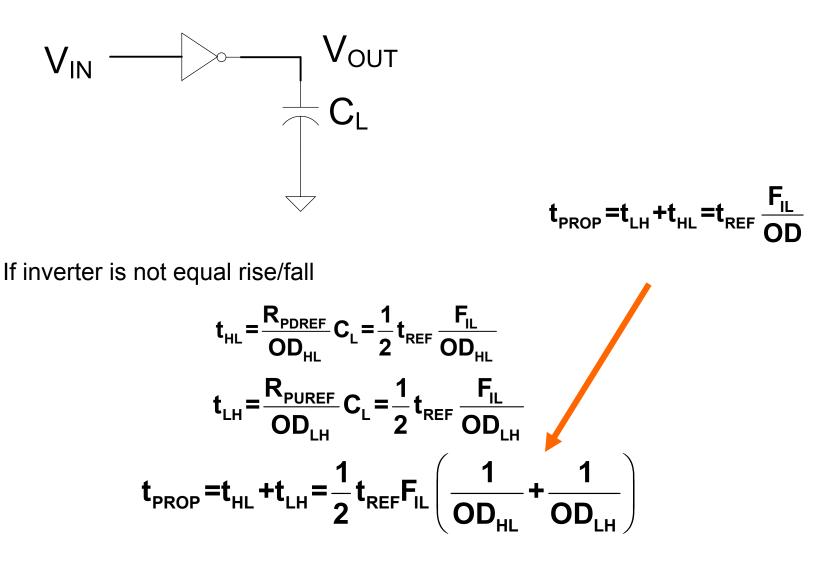

Overdrive

$t_{PROP} = t_{LH} + t_{HL} = t_{REF} \frac{F_{IL}}{OD}$

If inverter is not equal rise/fall

$$t_{HL} = \frac{R_{PDREF}}{OD_{HL}} C_{L} = \frac{1}{2} t_{REF} \frac{F_{IL}}{OD_{HL}}$$

$$t_{LH} = \frac{R_{PUREF}}{OD_{LH}} C_{L} = \frac{1}{2} t_{REF} \frac{F_{IL}}{OD_{LH}}$$

$$t_{PROP} = t_{HL} + t_{LH} = \frac{1}{2} t_{REF} F_{IL} \left(\frac{1}{OD_{HL}} + \frac{1}{OD_{LH}}\right)$$

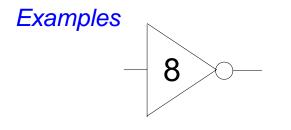

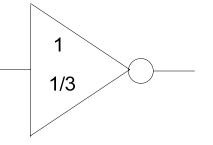

**Overdrive Notation**

- OD O-

Equal Rise/Fall with overdrive OD

Rise/Fall may be different with overdrive  $OD_{HL}$  and  $OD_{LH}$

$OD_{HL}$

ODLH

Equal Rise/Fall with overdrive of 8

If  $W_n$ - $W_{MIN}$ , minimum sized inverter

Example:

Equal rise-fall gates, no overderive

Equal rise-fall gates, no overderive

Equal rise-fall gates, with overderive

Nonequal rise-fall gates, with overderive

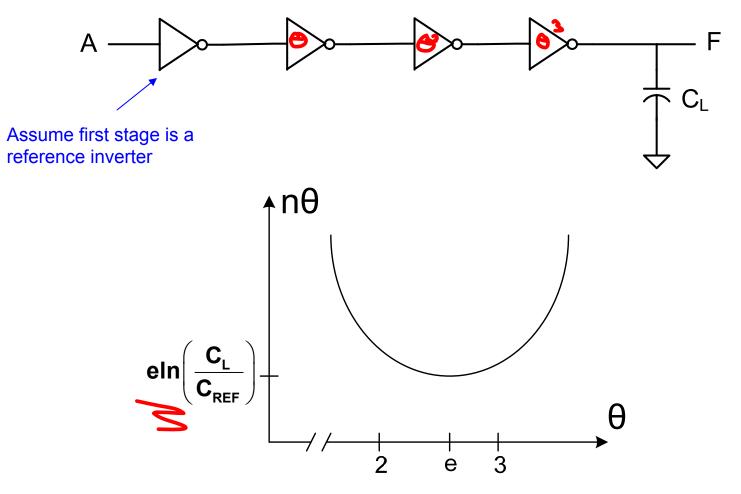

#### **Optimal Driving of Capacitive Loads**

Minimum at  $\theta$ =e but shallow inflection point for 2< $\theta$ <3

#### **Optimal Driving of Capacitive Loads**

Optimal number of stages is  $ln(C_L/C_{REF})$

Practically pick  $\theta$ =2 or 2.5 or 3 to obtain near optimal performance

### **Optimal Driving of Capacitive Loads**

Optimal number of stages is  $ln(C_L/C_{REF})$

Practically pick  $\theta$ =2 or 2.5 or 3 to obtain near optimal performance

t<sub>PROP</sub>≈ nθ

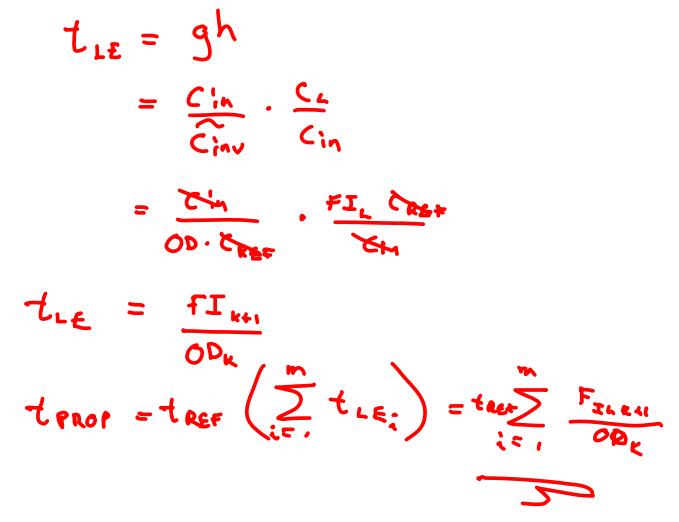

Delay calculations with logical effort approach 9 = ratio or input capacitons of the gate to the input capacitans of an inventer that can deliver the same output current - logic effort  $G = \frac{C_{in}}{\widetilde{C}_{iwv}} = \frac{C_{in}}{C_{REF}OD_{v}}$ h = electrial effort to be natio of doal capacillaco to logit capacitors of a sate  $h = \frac{C_L}{C_R}$

Delay calculations with logical effort approach

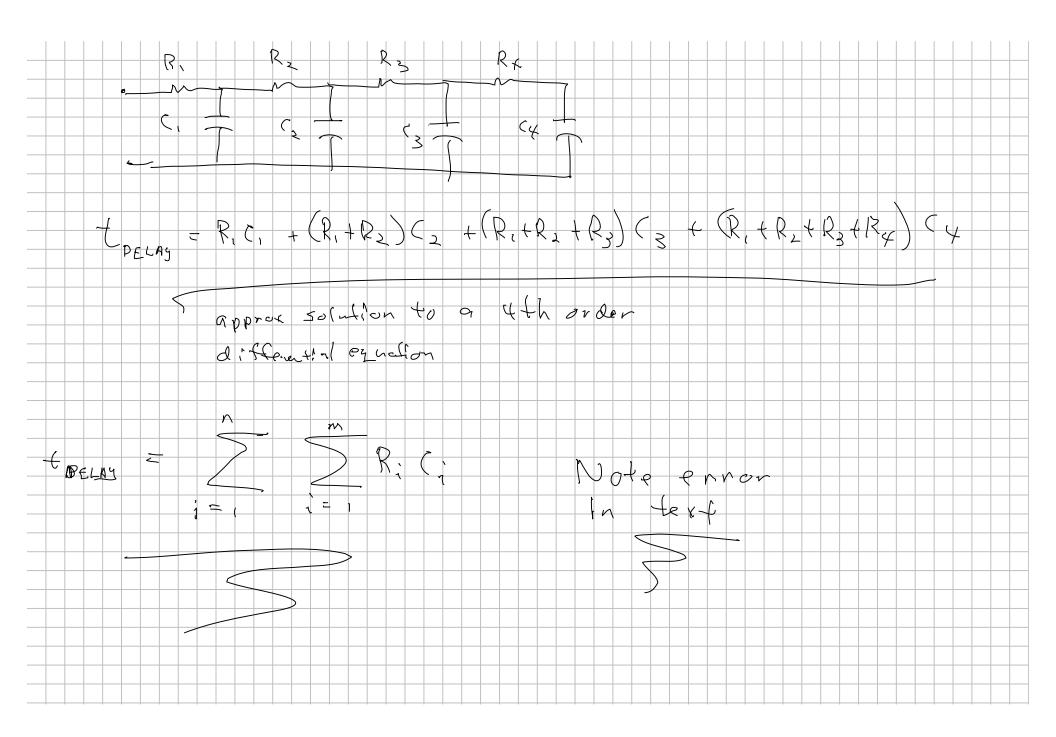

# Propagation Delay in Multiple-Levels of Logic with Stage Loading Elmore Delay Delay calculations with logical effort approach as laddor notway mock ( Is messay if m= j if msz

Is there a problem as socialed with neglecting spage compling in delag calculations for logic circuits we have used? - Golos actually do decompte between stages so existing approximation and 2 1, 10 good