EE 434 Exam 1 Fall 2003 Name \_\_\_\_\_

Instructions. Students may bring two  $8.5 \times 11$  pages of notes to this exam. On the exam, there are a set of short questions and 4 problems. All questions are worth 2 points and each problem is worth 20 points. All work and answers are to appear on this exam sheet. Attach additional sheets only if you run out of room on the examination itself.

If references to a semiconductor processes are needed and are not specified, assume a CMOS process is available with the following key process parameters;  $\mu_n C_{OX}=100\mu A/v^2$ ,  $\mu_p C_{OX}=30\mu A/v^2$ ,  $V_{TNO}=0.5V$ ,  $V_{TPO}=-0.5V$ ,  $C_{OX}=2fF/\mu^2$ ,  $\lambda = 0$ ,  $\gamma = 0$ , Cbdbot =  $0.5fF/\mu^2$ , and Cbdsw =  $2.5fF/\mu$ . and all npn bipolar transistors are characterized by the parameters  $\beta =100$ ,  $V_{AF}=4$ , and  $J_S=3E-19A/\mu^2$ . If more detailed information is needed, consult the process information attached as the last page of this exam. If any other process parameters are needed, specify clearly what process parameter is needed and specify a typical value for that parameter.

## Questions

1. What region of operation in the bipolar transistor is analogous to the saturation region of operation of the MOSFET?

2. What is the major difference between epitaxial silicon and polysolicon?

3. What is the major purpose of the field oxide growth in a CMOS process?

4. In a standard n-well bulk CMOS process the bulk-source voltages of all pchannel transistors can be made 0 to prevent the bulk voltage from modulating the threshold voltage but this can not be done for all n-channel transistors. Why can this not be done for all of the n-channel transistors?

5. What is the gate-source capacitance of an n-channel MOSFET in a 0.5u CMOS process if the channel dimensions are W=5u and L=10u? Selected parameters of a 0.5u CMOS process are attached on the last page of this exam.

6. The parameters NRD and NRS are optional parameters that can be included in the device line for a MOSFET in SPICE. What is the purpose of these two parameters?

7. An interconnect that is 100u long and 0.6u wide is needed on a layout. Compare the resistance of this interconnect if it is made with Metal 3 to what it would be if made with p+ active. Use the process parameters on the last page of this exam to make this comparison.

8. Why is the transconductance gain of a BJT typically much larger than that of a MOSFET?

9 In a state of the art CMOS process, the gate oxide thicknesses are in the  $30\text{\AA}$  range. If SiO<sub>2</sub> is used for the dielectric, about how many molecules are stacked vertically to form this dielectric?

10. The polysilicon processing step that is used to form the gates of MOS transistors is often termed a self-aligned process. Explain what self-aligned means when used in this context.

Problem 1 Determine the approximate cost per good die in a 0.25 $\mu$  process if the die area is 6mm<sup>2</sup> and the defect density is 1.5/cm<sup>2</sup>. Assume the cost of processing an 8 inch wafer is \$1400.

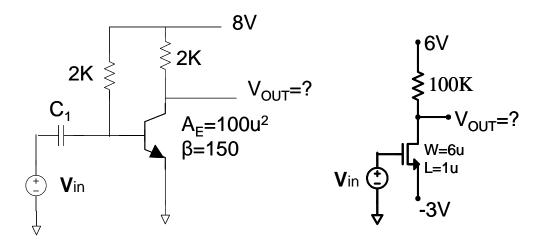

Problem 2 For the following circuits, determine the region of operation and the variable indicated with a ?. The two voltage sources labeled  $\forall$ in are small signal voltage sources.

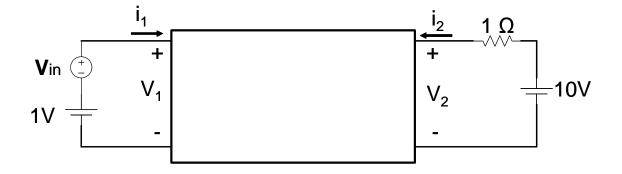

Problem 3 A two-port nonlinear network is shown below. The nonlinear relationship between the port variables is given by the equations

$$I_1 = 0.001V_1 + 0.02V_1V_2^2$$

$$I_2 = 2V_1^3$$

- a) Determine the small signal model and a small-signal equivalent circuit in terms of  $V_{1Q}$  and  $V_{2Q}$

- b) Determine the quiescent operating point for the circuit and numerical values for the parameters in the small signal model obtained in part a)

- c) Determine the small signal voltage gain from the Vin input to the  $V_2$  output.

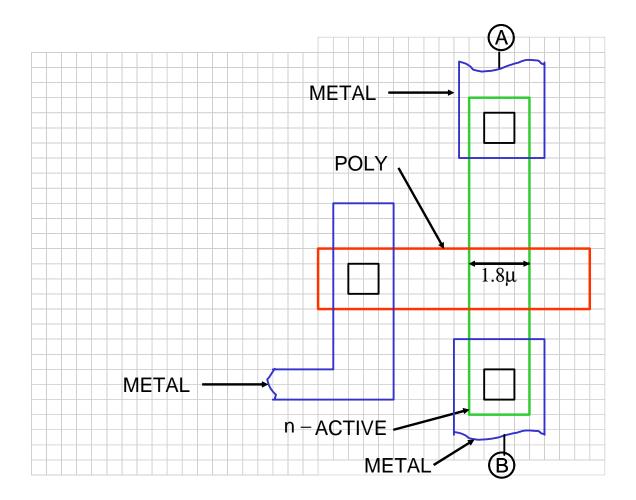

Problem 4 The layout of a transistor is shown. Assume the drain is defined by the top side of the device and the source by the bottom side of the device. Determine the following characteristics of this device:

W/L \_\_\_\_\_

Cdrain/bulk\_\_\_\_\_

Parasitic Gate Resistance

| Resistance from Top Metal (designated as $oxtimes$ ) to Drain _ |

|-----------------------------------------------------------------|

|-----------------------------------------------------------------|

Small signal g<sub>m</sub> if the quiescent gate to source voltage is 3 V \_\_\_\_\_

Use the process parameters listed on the last page of this exam to solve this problem.

| TRANSISTOR PARAMETERS                                                                                 | W/L                      | N-CHANNEL P-CHANNEL UNITS                       |                                 |                          |  |

|-------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------|---------------------------------|--------------------------|--|

| MINIMUM<br>Vth                                                                                        | 3.0/0.6                  | 0.78                                            | -0.93                           | volts                    |  |

| SHORT<br>Idss<br>Vth<br>Vpt                                                                           | 20.0/0.6                 | 439                                             | -238<br>-0.90<br>-10.0          | volts                    |  |

| WIDE<br>Ids0                                                                                          | 20.0/0.6                 | < 2.5                                           | < 2.5                           | pA/um                    |  |

| LARGE<br>Vth<br>Vjbkd<br>Ijlk<br>Gamma<br>K' (Uo*Cox/2)<br>Low-field Mobility<br>COMMENTS: XL_AMI_C5F | 50/50                    | 0.70<br>11.4<br><50.0<br>0.50<br>56.9<br>474.57 | -11.7<br><50.0<br>0.58<br>-18.4 | volts                    |  |

| FOX TRANSISTORS<br>Vth                                                                                | GATE<br>Poly             |                                                 | P+ACTIVE<br><-15.0              |                          |  |

| PROCESS PARAMETERS I<br>Sheet Resistance<br>Contact Resistance<br>Gate Oxide Thickness I              | 82.7 103.2<br>56.2 118.4 |                                                 | _                               | 7 0.09                   |  |

| PROCESS PARAMETERS<br>Sheet Resistance<br>Contact Resistance                                          | MTL3<br>0.05<br>0.78     | 824                                             | N_WELL<br>815                   | UNITS<br>ohms/sq<br>ohms |  |

COMMENTS: N\POLY is N-well under polysilicon.

| CAPACITANCE PARAMETERS<br>Area (substrate)<br>Area (N+active)<br>Area (P+active) | N+ACTV<br>429 | P+ACTV<br>721 | POLY<br>82<br>2401<br>2308 | POLY2 | M1<br>32<br>36 | M2<br>17<br>16 | M3<br>10<br>12 | N_WELL<br>40 | UNITS<br>aF/um^2<br>aF/um^2<br>aF/um^2 |

|----------------------------------------------------------------------------------|---------------|---------------|----------------------------|-------|----------------|----------------|----------------|--------------|----------------------------------------|

| Area (poly)                                                                      |               |               |                            | 864   | 61             | 17             | 9              |              | aF/um^2                                |

| Area (poly2)                                                                     |               |               |                            |       | 53             |                |                |              | aF/um^2                                |

| Area (metall)                                                                    |               |               |                            |       |                | 34             | 13             |              | aF/um^2                                |

| Area (metal2)                                                                    |               |               |                            |       |                |                | 32             |              | aF/um^2                                |

| Fringe (substrate)                                                               | 311           | 256           |                            |       | 74             | 58             | 39             |              | aF/um                                  |

| Fringe (poly)                                                                    |               |               |                            |       | 53             | 40             | 28             |              | aF/um                                  |

| Fringe (metal1)                                                                  |               |               |                            |       |                | 55             | 32             |              | aF/um                                  |

| Fringe (metal2)                                                                  |               |               |                            |       |                |                | 48             |              | aF/um                                  |

| Overlap (N+active)                                                               |               |               | 206                        |       |                |                |                |              | aF/um                                  |

| Overlap (P+active)                                                               |               |               | 278                        |       |                |                |                |              | aF/um                                  |