EE 434 FINAL EXAM Fall 2004 Name\_\_\_\_\_

Instructions. You may bring up to 6 sheets of notes to this exam which is comprised of 8 problems and 10 questions. The weight for each question is 2 points and for each problem is 10 points. Please solve the problems and include your answers directly on the exam sheet.

Unless specified directly in a problem, if references to semiconductor processes are needed, assume a CMOS process is available with the following key process parameters;  $\mu_n C_{OX}=100\mu A/v^2$ ,  $\mu_p C_{OX}=30\mu A/v^2$ ,  $V_{TNO}=0.5V$ ,  $V_{TPO}=-0.5V$ ,  $C_{OX}=2fF/\mu^2$ ,  $\lambda = 0$ ,  $\gamma = 0$ , Cbdbot =  $0.5fF/\mu^2$ , and Cbdsw =  $2.5fF/\mu$ . and all npn bipolar transistors are characterized by the parameters  $\beta = 100$ ,  $V_{AF}=4$ , and  $J_S=3E-19A/\mu^2$ . If more detailed process parameters are needed, refer to the list of parameters on the last page of this exam. If any other process parameters are needed, specify clearly what process parameter is needed and specify a typical value for that parameter.

Q1 What is the major purpose of the field oxide in a CMOS process?

Q2 How does the mobility of a p-channel transistor compare to that of an n-channel transistor?

Q3 What two regions of operation do most transistors operate in when used to build logic circuits?

Q4 In the AMI 0.5u CMOS process discussed in class, what is the difference between transistors used to build logic circuits and transistors used to build linear circuits?

Q5 How does the dynamic power dissipation of logic gates designed using minimum sized transistors in static CMOS implementations compare to that dissipated when the devices are sized for equal worst case rise and fall times?

Q6 If is often stated that the analog designer would prefer the bipolar process over the CMOS process yet many analog designs are done in the CMOS process. What is the major reason the technology of choice of the analog designer is not used to do analog designs?

#### Page 2 of 11

Q7 What is the two major advantages of dynamic logic over static CMOS logic in the applications where it is generally used?

Q8 Dynamic power dissipation was the major source of power dissipation in high speed CMOS circuits with minimum gate lengths at the  $0.35\mu$  range and above. As processes move to minimum gate lengths of  $0.12\mu$  and below, two other sources of power dissipation are becoming dominant. What are they?

Q9 How do the minimum feature sizes that can be patterned in a state of the art bipolar process compare to those that can be patterned in a CMOS process?

Q10 The propagation delay of minimum-sized gates driving comparable devices is in the 10 to 20 ps range which means they can be clocked at 50GHz to 100GHz rates yet the system clock on high-end microcontrollers and mircoprocessors is in the 3GHz range. Why is there such a big discrepancy?

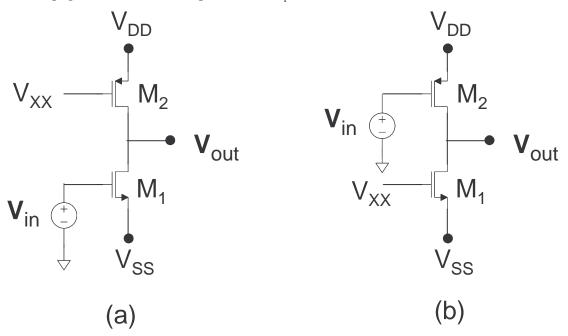

Problem 1 Two amplifier circuits are shown.

a) Determine the voltage gain for each in terms of the small signal parameters

b) Compare the small signal voltage gains of the two circuits if both are biased at the same quiescent current level.

Assume the widths and lengths of all transistors are the same, that all transistors are biased to operate in the saturation region, and that the process is the same as described on the first page of this exam except that  $\lambda_n = \lambda_p = .01 V^{-1}$

Problem 2 Assume the designer has to make a choice about whether to implement a particular function on one die or on two smaller equal-sized die. Assume the area overhead for the I/O on a chip is  $A_1$  and the total active area for implementing the required functionality is A. (Thus, if two chips are used, each will contain an area  $A_1$  for the I/O whereas if a single die is used, the total area for I/O will still be  $A_1$ ). Quantitatively compare the cost of producing a functional single-chip solution with that of the two-chip solution. Assume the defect density is  $1/\text{cm}^2$ , the die come from 8inch wafers that have a fabrication cost of \$1200, the area  $A_1$  is  $0.1\text{cm}^2$  and the area A is .25cm<sup>2</sup>. Neglect packaging and testing costs.

### Page 5 of 11

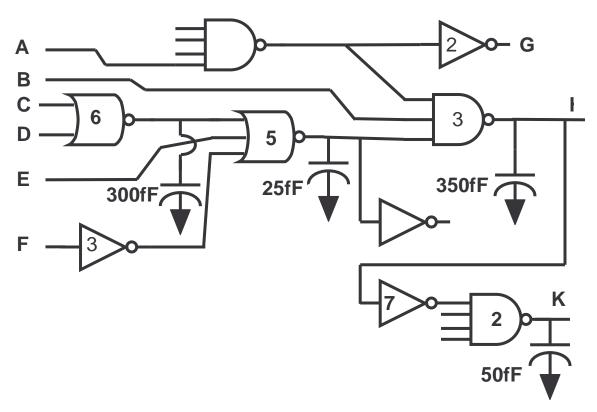

Problem 3 A logic circuit designed in conventional static CMOS is shown. Assume all gates are sized for equal worst-case rise and fall times and that the input capacitance of an equal rise/equal fall reference inverter is 2fF and that it has a propagation delay ( $T_{HL} + T_{LH}$ ) of 20psec. The overdrive factor, if different than 1, is indicated by the number on the gate symbol.

- a) Determine the propagation delay  $(T_{HL} + T_{LH})$  from the E input to the K output

- b) Repeat part a) if all gates use all minimum sized transistors.

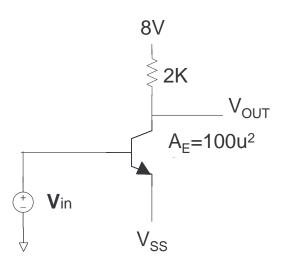

Problem 4 Assume that the voltage  $V_{SS}$  was selected so that the quiescent output voltage of the amplifier shown was measured to be 5V.

- a) Develop a small signal model for the BJT assuming it is operating in the forward active region. Use the forward active region model for the BJT introduced in the class.

- b) Determine the small-signal voltage gain of the circuit from the input to the output.

Problem 5 Design a circuit in the 0.5u AMI CMOS process that implements the following Boolean function  $F = \overline{AB} + A\overline{B}C$  in

a) Static CMOS Logic and

b) Pass Transistor Logic

c) Domino Logic

In your design, size all devices so that there are equal worst case rise and fall time for the static CMOS implementation and use minimum sizing in the PTL and Domino Logic implementations. Assume the input variables present are A,B and C.

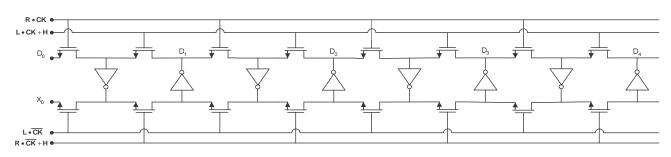

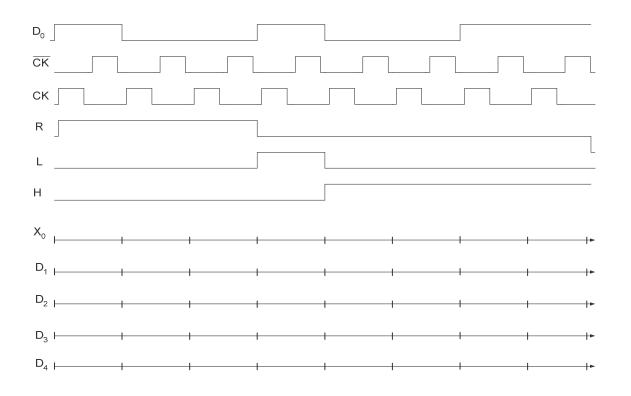

Probhlem 6 A circuit that is fabricated in a bulk CMOS process is shown. If the control signals are as given in the following timing diagram, provide a timing diagram for the signals  $X_0$ ,  $D_1$ ,  $D_2$ ,  $D_3$  and  $D_4$ . Indicate, as appropriate, on the timing diagram where the signals are not defined.

## Page 9 of 11

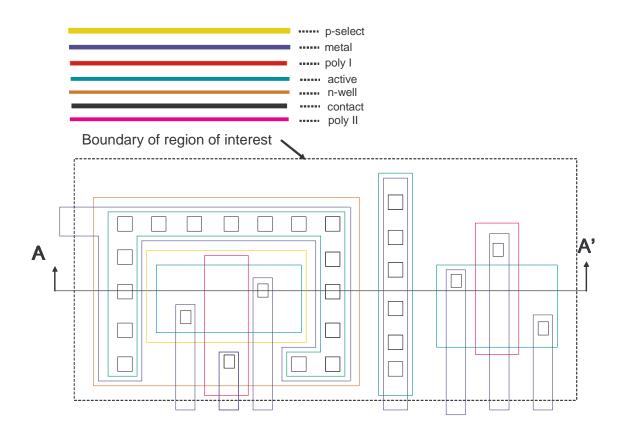

Problem 7 The top view of a section of a layout in a Bulk CMOS process is shown. Sketch a vertical cross-section view of this section along the A-A' section line.

## Page 10 of 11

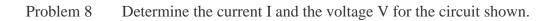

# Page 11 of 11

| TRANSISTOR PARAMETERS                                        | W/L                    | N-CHANNEL               | P-CHANNEL                       | UNITS                    |              |                                   |

|--------------------------------------------------------------|------------------------|-------------------------|---------------------------------|--------------------------|--------------|-----------------------------------|

| MINIMUM<br>Vth                                               | 3.0/0.6                | 0.78                    | -0.93                           | volts                    |              |                                   |

| SHORT<br>Idss<br>Vth<br>Vpt                                  | 20.0/0.6               | 439<br>0.69<br>10.0     | -238<br>-0.90<br>-10.0          | volts                    |              |                                   |

| WIDE<br>Ids0                                                 | 20.0/0.6               |                         | < 2.5                           | pA/um                    |              |                                   |

| LARGE<br>Vth<br>Vjbkd<br>Ijlk<br>Gamma                       | 50/50                  | 11.4<br><50.0           | -0.95<br>-11.7<br><50.0<br>0.58 | volts<br>pA              |              |                                   |

| K' (Uo*Cox/2)<br>Low-field Mobility                          |                        | 56.9<br>474.57          | -18.4<br>153.46                 | uA/V^2<br>cm^2/V*s       |              |                                   |

| COMMENTS: XL_AMI_C5F                                         |                        |                         |                                 |                          |              |                                   |

| FOX TRANSISTORS<br>Vth                                       | GATE<br>Poly           |                         | P+ACTIVE<br><-15.0              |                          |              |                                   |

|                                                              | 2.7 103.2<br>5.2 118.4 | 21.7                    |                                 | 7 0.09                   | 0.09<br>0.78 | UNITS<br>ohms/sq<br>ohms<br>strom |

| PROCESS PARAMETERS<br>Sheet Resistance<br>Contact Resistance | MTL3<br>0.05<br>0.78   | N\PLY N_WELL<br>824 815 |                                 | UNITS<br>ohms/sq<br>ohms |              |                                   |

| COMMENTS: N\POLY is N-wel                                    | ll under p             | olysilicon              |                                 |                          |              |                                   |

| CAPACITANCE PARAMETERS<br>Area (substrate)<br>Area (N+active)<br>Area (P+active)                                      | N+ACTV<br>429 | P+ACTV<br>721 | POLY<br>82<br>2401<br>2308 | POLY2 | M1<br>32<br>36 | M2<br>17<br>16 | M3<br>10<br>12       | N_WELL<br>40 | UNITS<br>aF/um^2<br>aF/um^2<br>aF/um^2                                               |

|-----------------------------------------------------------------------------------------------------------------------|---------------|---------------|----------------------------|-------|----------------|----------------|----------------------|--------------|--------------------------------------------------------------------------------------|

| Area (poly)<br>Area (poly2)<br>Area (metal1)<br>Area (metal2)                                                         |               |               | 2000                       | 864   | 61<br>53       | 17<br>34       | 9<br>13<br>32        |              | aF/um <sup>2</sup><br>aF/um <sup>2</sup><br>aF/um <sup>2</sup><br>aF/um <sup>2</sup> |

| Fringe (substrate)<br>Fringe (poly)<br>Fringe (metal1)<br>Fringe (metal2)<br>Overlap (N+active)<br>Overlap (P+active) | 311           | 256           | 206<br>278                 |       | 74<br>53       | 58<br>40<br>55 | 39<br>28<br>32<br>48 |              | aF/um<br>aF/um<br>aF/um<br>aF/um<br>aF/um<br>aF/um                                   |