# EE 435 Lecture 14

# Two-Stage Op Amp Design

- Architectures

- Compensation

- First-stage compensation

- Load compensated

- Miller Compensation

### Review from Last Time Cascaded Amplifier Summary

$$\mathsf{A} = \frac{\mathsf{A}_{\mathsf{o}} \ \tilde{\mathsf{p}}}{\mathsf{s} + \tilde{\mathsf{p}}} \quad \widetilde{p}_2 = k \widetilde{p}_1$$

$8 > \beta A_0^3$

Single-stage amplifiers

-- widely used in industry, little or no concern about compensation

Two amplifier cascades – for separated poles  $4\beta A_{0TOT} > k > 2\beta A_{0TOT}$

- -- widely used in industry but compensation is essential

- -- spread dependent upon  $\beta$  and most stringent for large  $\beta$

- Three amplifier cascades for ideally identical stages

- -- seldom used in industry !

Three amplifier cascades - for separated poles

$$(1+k_{2}+k_{3})(k_{2}+k_{3}+k_{2}k_{3}) > \beta A_{0TOT}$$

-- seldom used in industry but starting to appear but compensation essential!

Four or more amplifier cascades - problems even larger than for three stages

-- seldom used in industry !

Note: Some amplifiers that are termed single-stage amplifiers in many books and papers are actually two-stage amplifiers and some require modest compensation. Some that are termed two-stage amplifiers are actually three-stage amplifiers. These invariable have a very small gain on the first stage and a very large bandwidth. The nomenclature on this summary refers to the number of stages that have reasonably large gain.

### Review from Last Time Pole approximation methods

- 1. Consider all shunt capacitors

- 2. Decompose these into two sets, those that create low frequency poles and those that create high frequency poles (large capacitors create low frequency poles and small capacitors create high frequency poles)  $\{C_{L1}, \dots C_{Lk}\}$  and  $\{C_{H1}, \dots C_{Hm}\}$

- 3. To find the k low frequency poles, replace all independent voltage sources with ss shorts and all independent current sources with ss opens, all high-frequency capacitors with ss open circuits and, one at a time, select  $C_{Lh}$  and determine the impedance facing it, say  $R_{Lh}$  if all other low-frequency capacitors are replaced with ss short circuits. Then an approximation for the pole corresponding to  $C_{Lh}$  is

$$p_{Lh} = -1/(R_{Lh}C_{Lh})$$

4. To find the m high-frequency poles, replace all independent voltage sources with ss shorts and all independent current sources with ss opens, replace all low-frequency capacitors with ss short circuits and, one at a time, select  $C_{Hh}$  and determine the impedance facing it, say  $R_{Hh}$  if all other high-frequency capacitors are replaced with ss open circuits. Then the approximation for the pole corresponding to  $C_{Hh}$  is

$$p_{Hh} = -1/(R_{Hh}C_{Hh})$$

### **Review from Last Time**

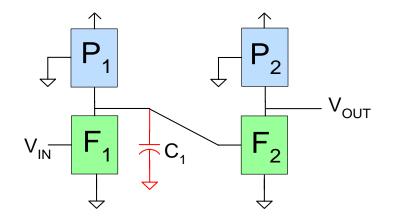

**Compensation of Basic Two-Stage Cascade**

Internally Compensated

**Output Compensated**

- Modest variants of the compensation principle are often used

- Internally compensated creates the dominant pole on the internal node

- Output compensated created the dominant pole on the external node

- Output compensated often termed "self-compensated"

Everything else is just details !!

**Review from Last Time**

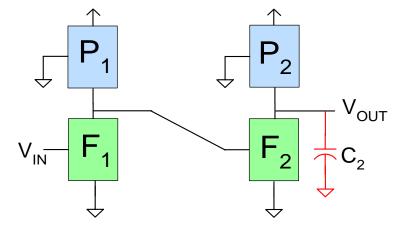

### **Common Compensation Goal**

Typical Target Closed-loop Pole Locations for Feedback Amplifiers

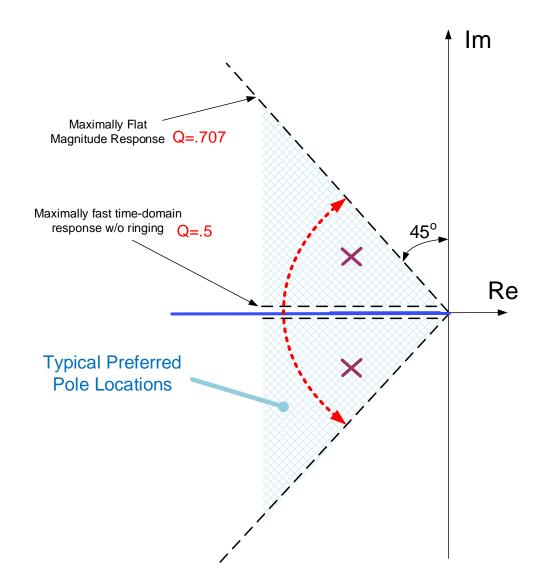

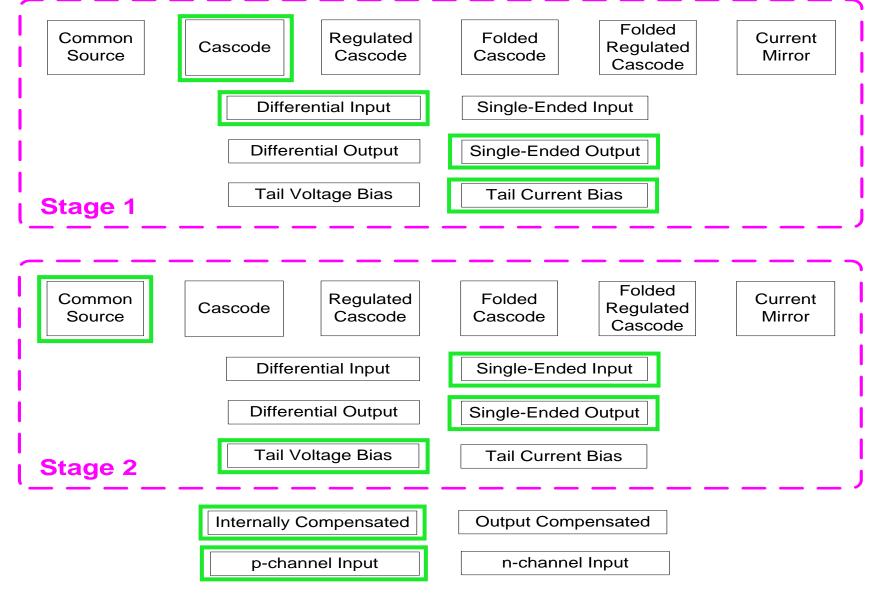

### Review from Last Time Two-stage Architectural Choices

Which of these 2304 choices can be used to build a good op amp?

## All of them !!

### Review from Last Time Two-stage Architectural Choices

**Guidelines for Architectural Choices**

Tail current source usually used in first stage, tail voltage source in second stage

Large gain usually used in first stage, smaller gain in second stage

First and second stage usually use quarter circuits of opposite types (n-p or p-n)

Input common mode input range of concern on first stage but output swing of first stage of reduced concern. Output range on second stage of concern.

CMRR of first stage of concern but not of second stage

Noise on first stage of concern but not of much concern on second stage

Offset voltage usually dominated by that of the first stage

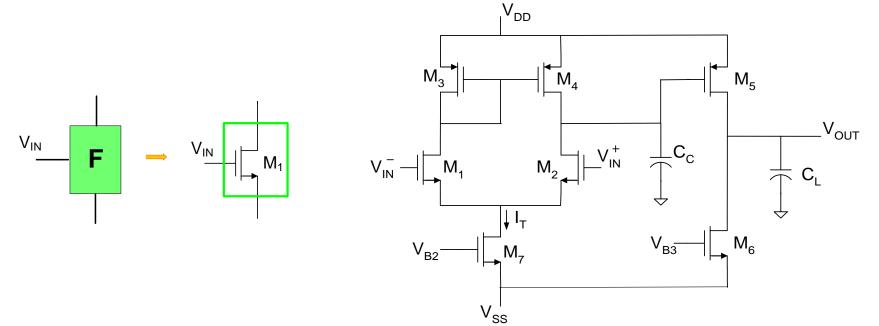

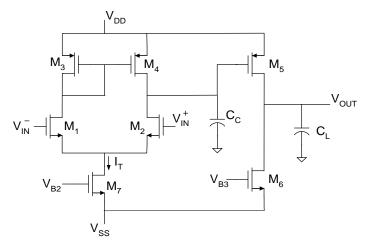

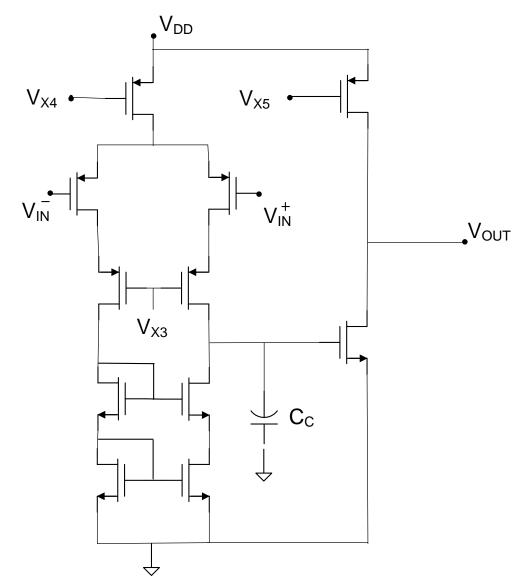

### Review from Last Time Basic Two-Stage Op Amp (compensated on first stage)

o One of the most widely used op amp architectures

- o Essentially just a cascade of two common-source stages

- o Compensation Capacitor C<sub>C</sub> used to get wide pole separation

- o Pole on drain node of M<sub>1</sub> usually of little concern

- o Two poles in differential operation of amplifier usually dominate performance

- o C<sub>C</sub> can be internal (termed internally compensated) or external (termed externally compensated)

- o External compensation works but is usually not practical

- o No universally accepted strategy for designing this seemingly simple amplifier

Pole spread  $k \beta A_{01} A_{02} = 2 < k < 4$  makes  $C_C$  unacceptably large for on-chip solutions

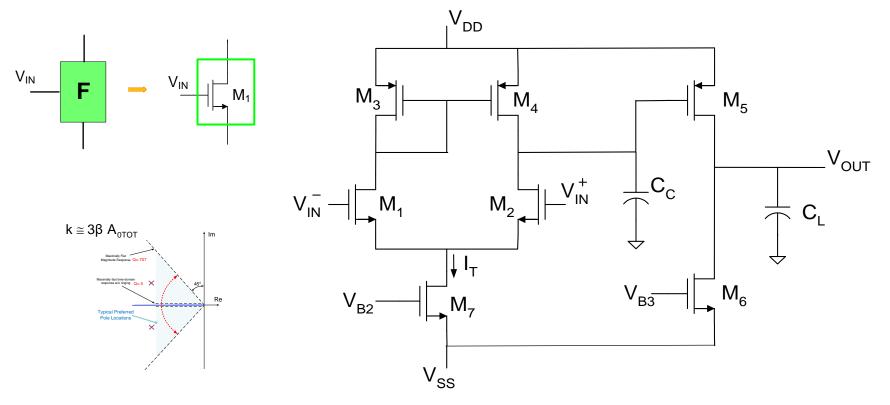

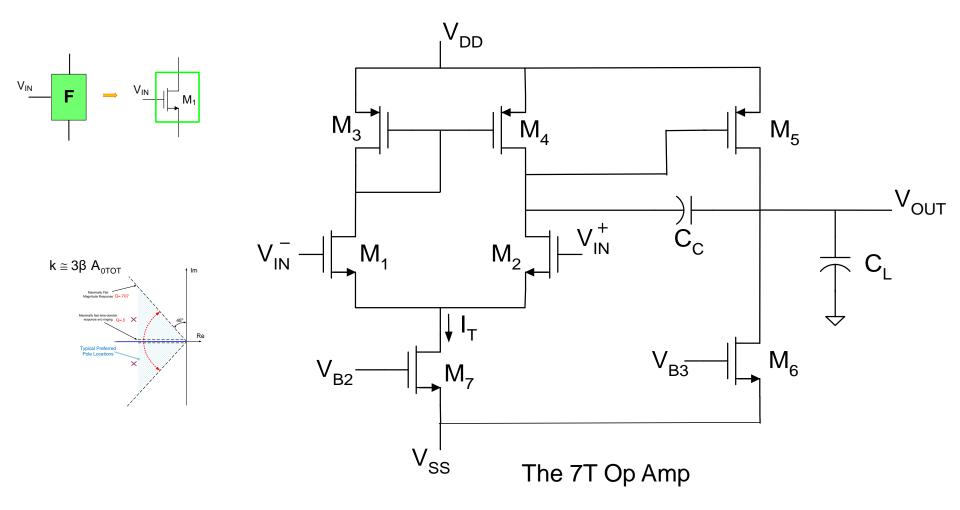

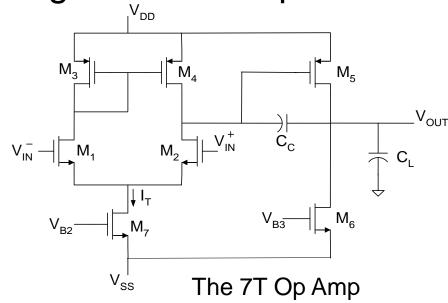

## Basic Two-Stage Op Amp

Will refer to this as the 7T Op Amp

### Pole spread $\propto \beta A_{01}A_{02}$ makes $C_C$ unacceptably large

- Remember, pole spread strongly dependent upon β

- Large  $\beta$  (i.e.  $\beta$ =1) requires large C<sub>C</sub>

- C<sub>C</sub> is usually an additional capacitor that is added

- Concept of Miller compensation will be used to reduce actual size of  $C_{\rm C}$  What about just making  $C_{\rm C}$  larger than what is needed?

### GB will degrade, power and area will increase

What about providing additional compensation by making C<sub>L</sub> larger too?

Poles will move together and degrade performance

What about compensating for worst-case  $\beta=1$  so  $\beta$  dependence can be ignored?

- Good solution for catalog parts so application space large but at a cost !

- Penalty in GB, power, and area sever if compensated for much different β than needed

### Basic Two-Stage Op Amp

Pole spread  $\propto \beta A_{01}A_{02}$  makes  $C_C$  unacceptably large

Important to compensate just for what is needed, even a little more comes at a rather big penalty in performance, power, or area !!

LF147, LF347-N

www.ti.com

SNOSBH1D - MAY 1999 - REVISED MARCH 2013

#### LF147/LF347 Wide Bandwidth Quad JFET Input Operational Amplifiers

Check for Samples: LF147, LF347-N

#### FEATURES

- Internally Trimmed Offset Voltage: 5 mV max

- Low Input Bias Current: 50 pA

- Low Input Noise Current: 0.01 pA/√Hz

- Wide Gain Bandwidth: 4 MHz

- High Slew Rate: 13 V/µs

- Low Supply Current: 7.2 mA

- High Input Impedance: 10<sup>12</sup>Ω

- Low Total Harmonic Distortion: ≤0.02%

- Low 1/f Noise Corner: 50 Hz

- Fast Settling Time to 0.01%: 2 µs

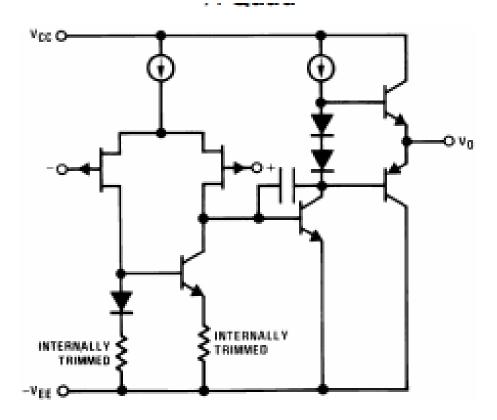

#### Simplified Schematic

#### DESCRIPTION

The LF147 is a low cost, high speed quad JFET input operational amplifier with an internally trimmed input offset voltage (BI-FET II<sup>™</sup> technology). The device requires a low supply current and yet maintains a large gain bandwidth product and a fast slew rate. In addition, well matched high voltage JFET input devices provide very low input bias and offset currents. The LF147 is pin compatible with the standard LM148. This feature allows designers to immediately upgrade the overall performance of existing LF148 and LM124 designs.

The LF147 may be used in applications such as high speed integrators, fast D/A converters, sample-and-hold circuits and many other circuits requiring low input offset voltage, low input bias current, high input impedance, high slew rate and wide bandwidth. The device has low noise and offset voltage drift.

#### **Connection Diagram**

Figure 1. 14-Pin PDIP / CDIP / SOIC

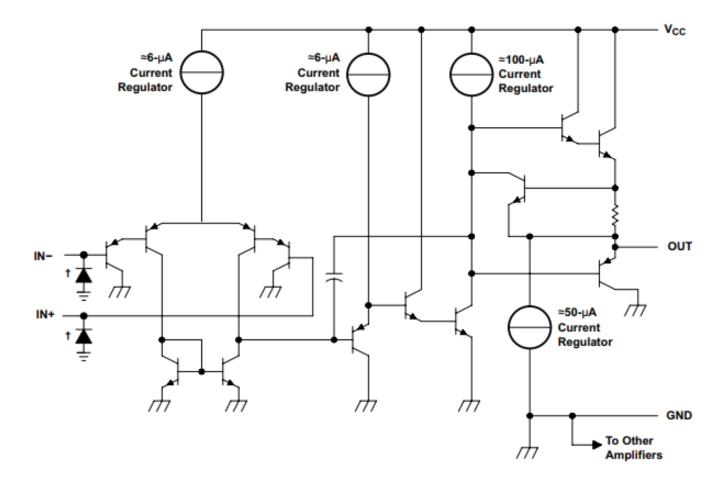

#### LM224K, LM224KA, LM324, LM324A, LM324K, LM324KA, LM2902 LM124, LM124A, LM224, LM224A, LM2902V, LM2902K, LM2902KV, LM2902KAV

SLOS066W-SEPTEMBER 1975-REVISED MARCH 2015

LMx24, LMx24x, LMx24xx, LM2902, LM2902x, LM2902xx, LM2902xxx Quadruple Operational Amplifiers

#### 1 Features

- 2-kV ESD Protection for:

- LM224K, LM224KA

- LM324K, LM324KA

- LM2902K, LM2902KV, LM2902KAV

- Wide Supply Ranges

- Single Supply: 3 V to 32 V (26 V for LM2902)

- Dual Supplies: ±1.5 V to ±16 V (±13 V for LM2902)

- Low Supply-Current Drain Independent of Supply Voltage: 0.8 mA Typical

- Common-Mode Input Voltage Range Includes Ground, Allowing Direct Sensing Near Ground

- Low Input Bias and Offset Parameters

- Input Offset Voltage: 3 mV Typical

#### 2 Applications

- Blu-ray Players and Home Theaters

- Chemical and Gas Sensors

- DVD Recorders and Players

- Digital Multimeter: Bench and Systems

- · Digital Multimeter: Handhelds

- Field Transmitter: Temperature Sensors

- Motor Control: AC Induction, Brushed DC, Brushless DC, High-Voltage, Low-Voltage, Permanent Magnet, and Stepper Motor

- Oscilloscopes

- TV: LCD and Digital

- Temperature Sensors or Controllers Using Modbus

- Weigh Scales

#### 8.2 Functional Block Diagram

### MT-033 TUTORIAL

#### Voltage Feedback Op Amp Gain and Bandwidth

#### **INTRODUCTION**

This tutorial examines the common ways to specify op amp gain and bandwidth. It should be noted that this discussion applies to voltage feedback (VFB) op amps—current feedback (CFB) op amps are discussed in a later tutorial (MT-034).

#### **OPEN-LOOP GAIN**

Unlike the ideal op amp, a practical op amp has a finite gain. The open-loop dc gain (usually referred to as  $A_{VOL}$ ) is the gain of the amplifier without the feedback loop being closed, hence the name "open-loop." For a precision op amp this gain can be vary high, on the order of 160 dB (100 million) or more. This gain is flat from dc to what is referred to as the *dominant pole corner frequency*. From there the gain falls off at 6 dB/octave (20 dB/decade). An octave is a doubling in frequency and a decade is ×10 in frequency). If the op amp has a single pole, the open-loop gain will continue to fall at this rate as shown in Figure 1A. A practical op amp will have more than one pole as shown in Figure 1B. The second pole will double the rate at which the open-loop gain falls to 12 dB/octave (40 dB/decade). If the open-loop gain has dropped below 0 dB (unity gain) before it reaches the frequency of the second pole, the op amp will be unconditionally stable at any gain. This will be typically referred to as *unity gain stable* on the data sheet. If the second pole is reached while the closed-loop gain is greater than 1 (0 db), then the amplifier may not be stable. Some op amps are designed to be stable only at higher closed-loop gains, and these are referred to as *decompensated* op amps.

**Decompensated Op Amp**

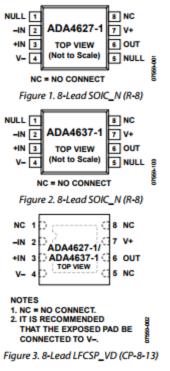

### 30 V, High Speed, Low Noise, Low Bias Current, JFET Operational Amplifier

### Data Sheet

### ADA4627-1/ADA4637-1

#### FEATURES

Low offset voltage: 200 µV maximum Offset drift: 1 µV/°C typical Very low input bias current: 5 pA maximum Extended temperature range: -40°C to +125°C ±5 V to ±15 V dual supply ADA4627-1 GBW: 19 MHz ADA4637-1 GBW: 79 MHz Voltage noise: 6.1 nV/√Hz at 1 kHz ADA4627-1 slew rate: 82 V/µs ADA4637-1 slew rate: 170 V/µs High gain: 120 dB typical High CMRR: 116 dB typical High PSRR: 112 dB typical

#### APPLICATIONS

High impedance sensors Photodiode amplifier Precision instrumentation Phase-locked loop filters High end, professional audio DAC output amplifier ATE Medical

#### **PIN CONFIGURATIONS**

### ADA4627-1/ADA4637-1

#### **Data Sheet**

| Parameter                            | Symbol  | Test Conditions/Comments                                                                   | B Grade |          |     | A Grade |          |     |        |

|--------------------------------------|---------|--------------------------------------------------------------------------------------------|---------|----------|-----|---------|----------|-----|--------|

|                                      |         |                                                                                            | Min     | Тур      | Max | Min     | Тур      | Max | Unit   |

| Settling Time to 0.01%               | ts      |                                                                                            |         |          |     |         |          |     |        |

| ADA4627-1                            |         | $V_{IN} = 10 \text{ V step}, C_L = 35 \text{ pF},$<br>$R_L = +1  k\Omega, A_V = -1$        |         | 550      |     |         | 550      |     | ns     |

| ADA4637-1                            |         | $V_{IN} = 10 \text{ V step}, C_L = 35 \text{ pF},$<br>$R_L = +1 \text{ k}\Omega, A_V = -4$ |         | 300      |     |         | 300      |     | ns     |

| Settling Time to 0.1%                | ts      |                                                                                            |         |          |     |         |          |     |        |

| ADA4627-1                            |         | $V_{IN} = 10 \text{ V step}, C_L = 35 \text{ pF},$<br>$R_L = +1  k\Omega, A_V = -1$        |         | 450      |     |         | 450      |     | ns     |

| ADA4637-1                            |         | $V_{OUT} = 10 \text{ V step}, C_L = 35 \text{ pF},$<br>$R_L = +1  k\Omega, A_V = -4$       |         | 200      |     |         | 200      |     | ns     |

| Gain Bandwidth Product               | GBP     |                                                                                            |         |          |     |         |          |     |        |

| ADA4627-1                            |         | $R_L = 1 \ k\Omega, C_L = 20 \ pF, A_V = 1$                                                | 164     | 19       |     | 164     | 19       |     | MHz    |

| ADA4637-1                            |         | $A_{v} = 10$                                                                               |         | 79.9     |     |         | 79.9     |     |        |

| Phase Margin                         | Фм      |                                                                                            |         |          |     |         |          |     |        |

| ADA4627-1                            |         | $R_L = 1 \ k\Omega, C_L = 20 \ pF, A_V = 1$                                                |         | 72       |     |         | 72       |     | Degree |

| ADA4637-1                            |         | Av = 10                                                                                    |         | 85       |     |         | 85       |     |        |

| Total Harmonic<br>Distortion + Noise | THD + N | V <sub>IN</sub> = 6 V rms, f = 1 kHz, A <sub>V</sub> = 1,<br>ADA4627-1                     |         | 0.000045 |     |         | 0.000045 |     | %      |

# Example:

Sketch the circuit of a two-stage internally compensated op amp with a telescopic cascode first stage, single-ended output, tail current bias first stage, tail voltage bias second stage, p-channel inputs and n-channel inputs on the second stage.

### **Two-stage Architectural Choices**

### Cascode-Cascade Two-Stage Op Amp

### **Example Solution**

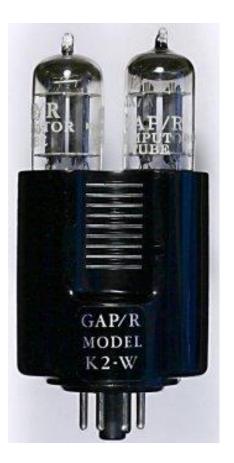

First Commercial Operational Amplifier

K2-W Op Amp by Philbrickk, 1952-1971

### Inventor of the Two-Stage Op Amp

### **Robert Widlar**

Many say he started the field of analog IC design, considered a brilliant engineer

"Widlar began his career at Fairchild semiconductor, where he designed a couple of pioneering op amps. By 1966, the commercial success of his designs became apparent, and Widlar asked for a raise. He was turned down, and jumped ship to the fledgling National Semiconductor. At National he continued to turn out amazing designs, and was able to retire just before his 30th birthday in 1970." (from posted www site)

### Inventor of the internally-compensated Op Amp Dave Fullagar

(from posted www site)

- Designed the first internally-compensate op amp, the 741

- Fullagar was 26 years old when this was designed (introduced?)

- Introduced in 1968

- Largest selling integrated circuit ever

- Still in high-volume production even though over 50 years old

- Fullagar later started the linear design activities at Intersil

- Cofounder (catalyst) of Maxim

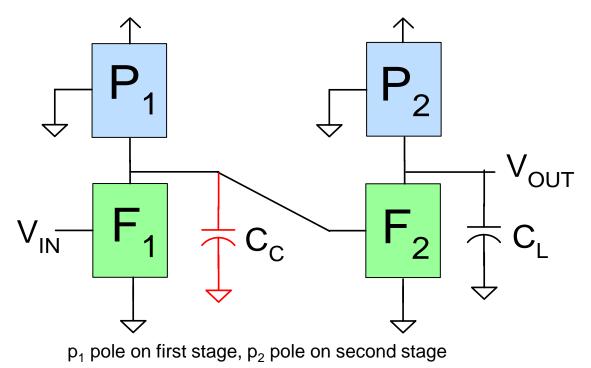

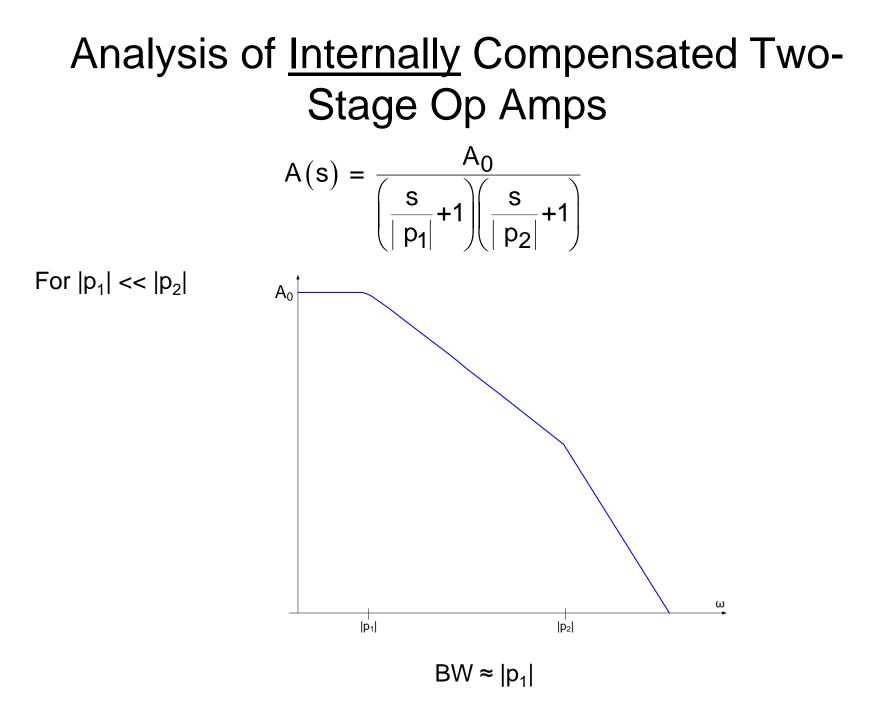

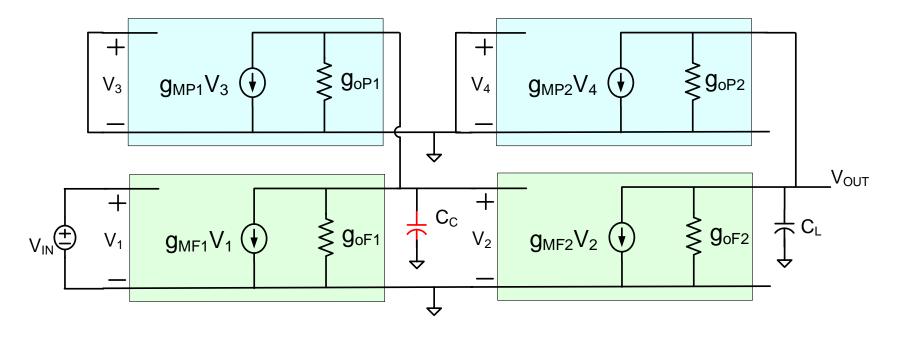

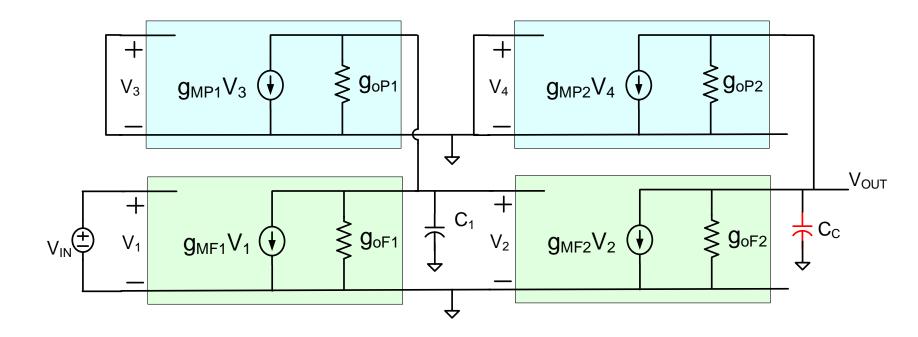

## Analysis of <u>Internally</u> Compensated Two-Stage Op Amps

Consider single-ended input-output (differential analysis only slightly different) Can't get everything but can get most of the small-signal results Since internally compensated, must have  $p_1 << p_2$

## Analysis of Internally Compensated Two-Stage Op Amps

### Analysis of Internally Compensated Two-Stage Op Amps

$$\begin{split} &V_{2}\left(sC_{C}+g_{_{0}\text{F1}}+g_{_{0}\text{P1}}\right)+g_{_{m}\text{F1}}V_{_{IN}}=0 \\ &V_{_{OUT}}\left(sC_{_{L}}+g_{_{0}\text{P2}}+g_{_{0}\text{F2}}\right)+g_{_{m}\text{F2}}V_{_{2}}=0 \end{split}$$

$$A_{V}(s) = \frac{-g_{mF1}}{sC_{C} + g_{oF1} + g_{oP1}} \bullet \frac{-g_{mF2}}{sC_{L} + g_{oP2} + g_{oF2}}$$

## Analysis of Internally Compensated Two-Stage Op Amps

$\boldsymbol{GB} = \frac{\boldsymbol{g}_{\text{mF1}}\boldsymbol{g}_{\text{mF2}}}{\left(\boldsymbol{g}_{\text{oF2}} + \boldsymbol{g}_{\text{oP2}}\right)\!\boldsymbol{C}_{\text{C}}}$

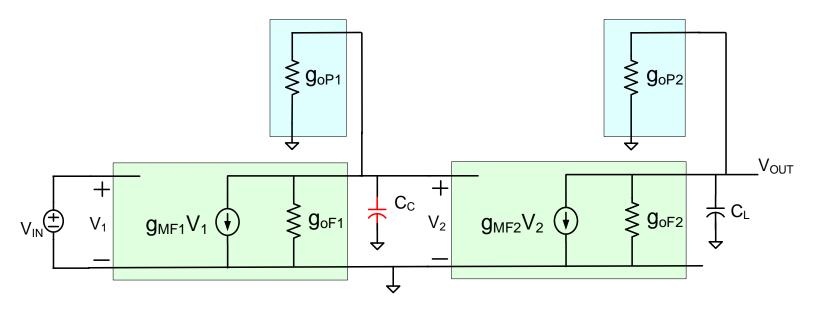

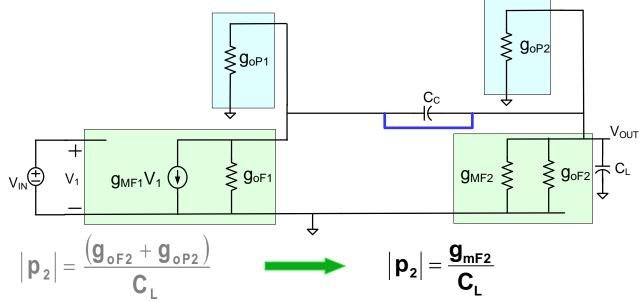

## Analysis of Load Compensated Two-Stage Op Amps

Can't get everything but can get most of the small-signal results

## Analysis of Load Compensated Two-Stage Op Amps

## Analysis of Externally Compensated Two-Stage Op Amps

Consider Again the Internally Compensated Two-Stage Op Amp

Recall approximate compensation requirements:  $4\beta A_{oTOT} > k > 2\beta A_{oTOT}$ where  $|\mathbf{p}_2| = \mathbf{k}|\mathbf{p}_1|$ Thus, approximately,  $3\beta A_{oTOT} = \frac{|\mathbf{p}_2|}{|\mathbf{p}_1|}$   $k \cong 3\beta A_{oTOT}$   $3\beta \left(\frac{g_{mF1}}{g_{oF1} + g_{oP1}}\right) \left(\frac{g_{mF2}}{g_{oF2} + g_{oP2}}\right) \approx \left(\frac{g_{oF2} + g_{oP2}}{C_L}\right) \left(\frac{C_C}{g_{oF1} + g_{oP1}}\right)$  $C_C \approx \left(3\beta \frac{g_{mF1}g_{mF2}}{(g_{oF2} + g_{oP2})^2}\right) C_L$

Since the pole ratio needs to be very large, C<sub>c</sub> gets very large !

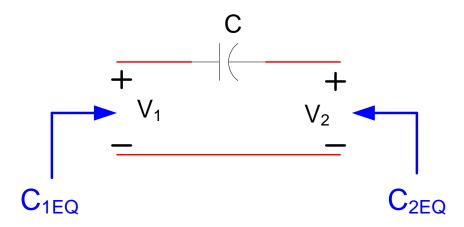

If

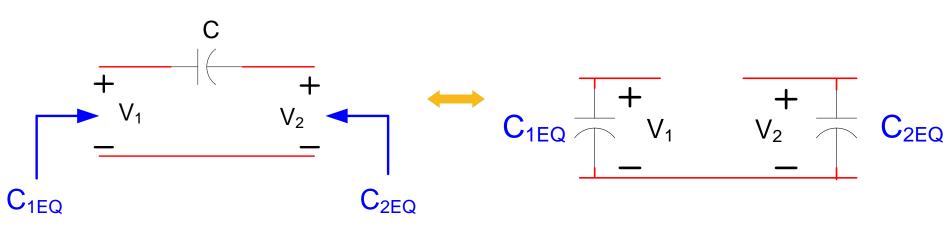

$$V_2 = -AV_1$$

then for A large

$C_{1EQ} = C(1 + A) \approx CA$

$C_{2EQ} = C(1 + \frac{1}{A}) \approx C$

Thus, a large effective capacitance can be created with a much smaller capacitor if a capacitor bridges two nodes with a large inverting gain !!

Note: The symbol "A" used in the Miller Capacitance should not be confused with the gain of the op amp

If

$$V_2 = -AV_1$$

then for A large

$C_{1EQ} = C(1 + A) \approx CA$

$C_{2EQ} = C(1 + \frac{1}{A}) \approx C$

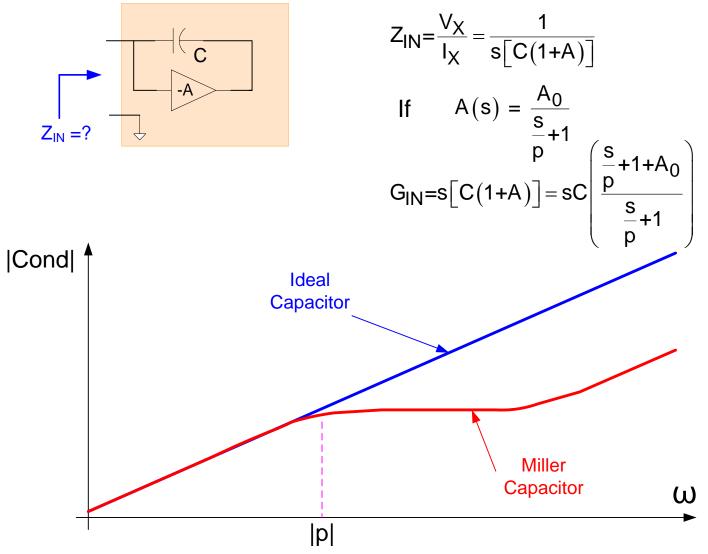

- If A changes with frequency, C<sub>1EQ</sub> and C<sub>2EQ</sub> are no longer pure capacitors

- More useful for giving a concept than for accurate actual analysis because of frequency dependence of A

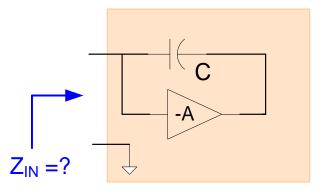

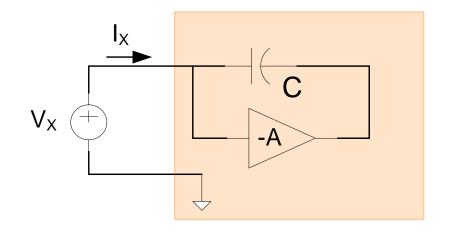

The Basic Concept – from capacitance multiplication

$$V_{X} = [V_{X} - (-AV_{X})]sC = V_{X}s[C(1+A)]$$

thus

$$Z_{IN} = \frac{V_X}{I_X} = \frac{1}{s[C(1+A)]}$$

So, if A is constant, input looks like a capacitor of value  $C_{EQ}=C(1+A)$

Does not behave as a capacitor for  $\omega > p$

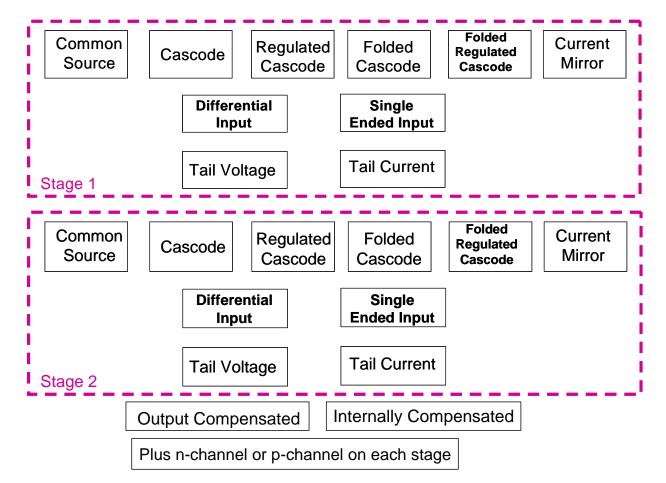

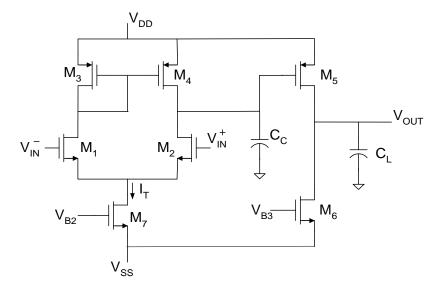

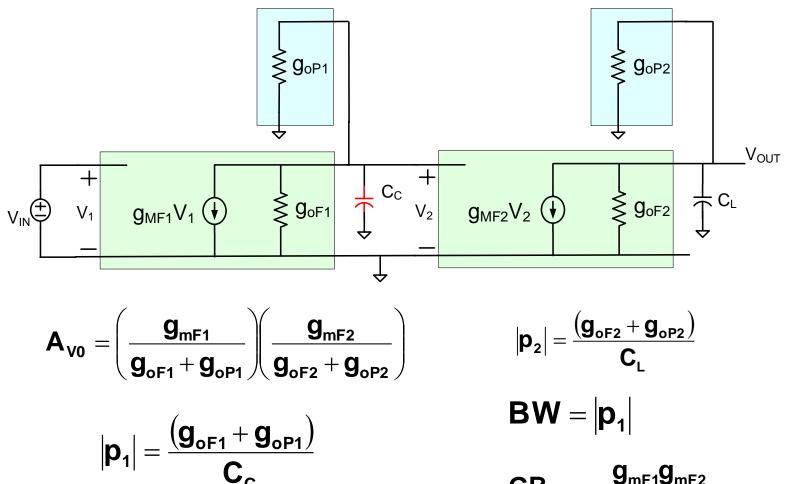

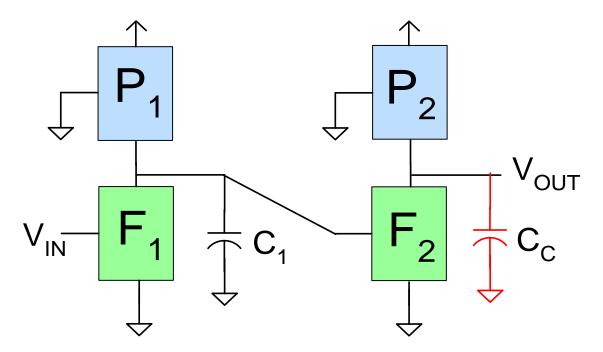

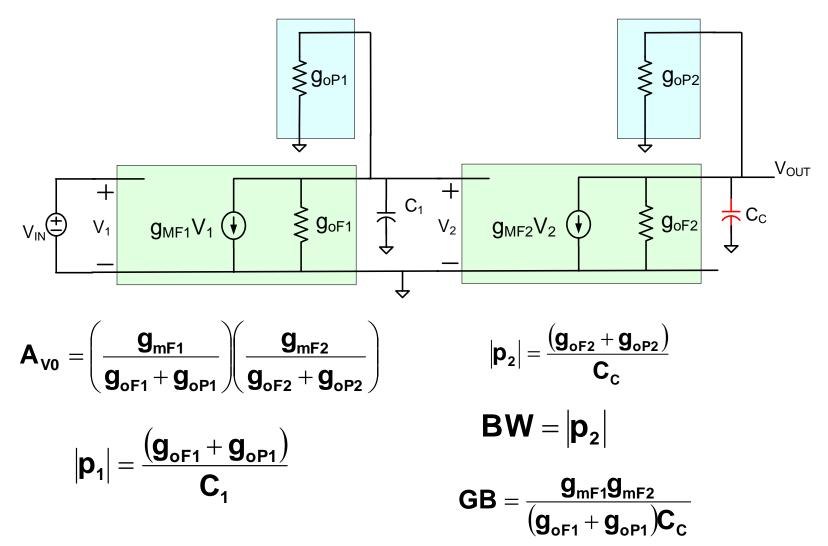

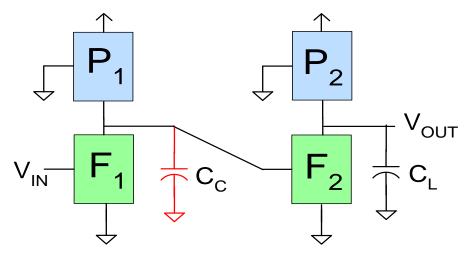

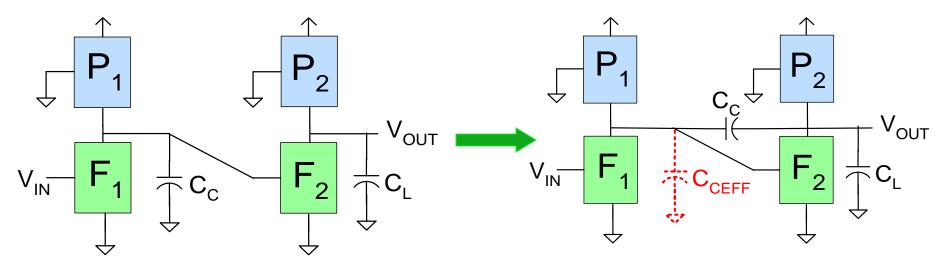

### Internal Miller-Compensated Two-Stage Op Amp

Standard Compensation

Miller Compensation

The second stage amplifier can be used to create a Miller capacitance at its input with no circuit overhead!

Compensation capacitance reduced by approximately the gain of the second stage! (the value of the two C<sub>c</sub>'s are not the same)

Since the gain of the second stage is not constant, however, a new analysis is needed

Note the F2 block is now "diode connected" at high frequencies

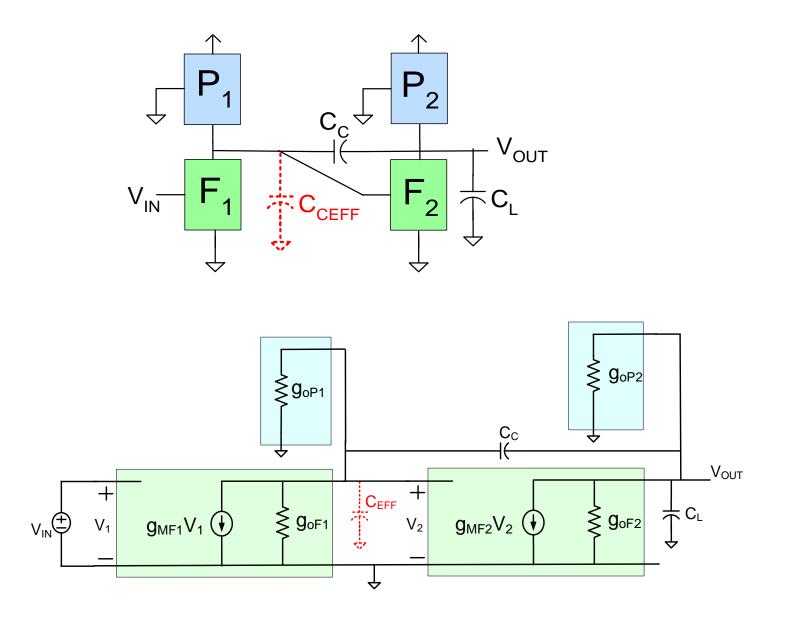

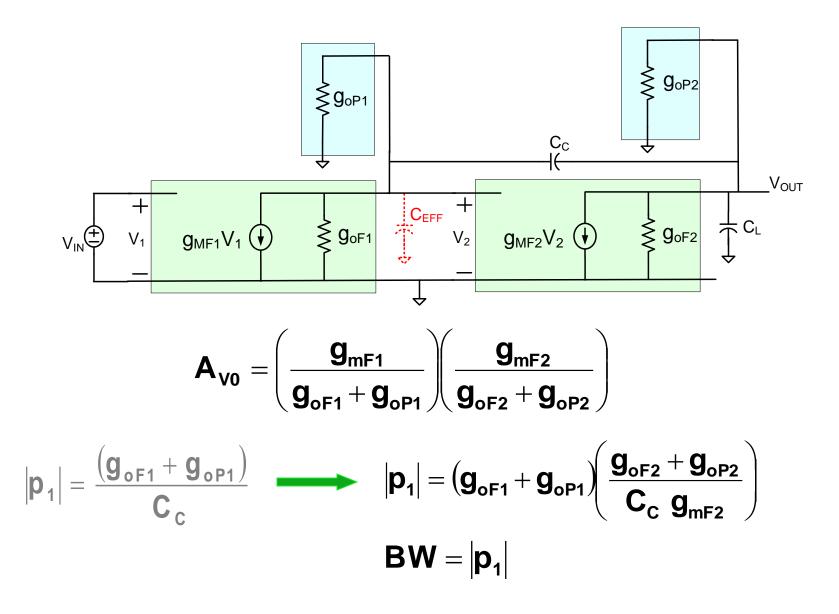

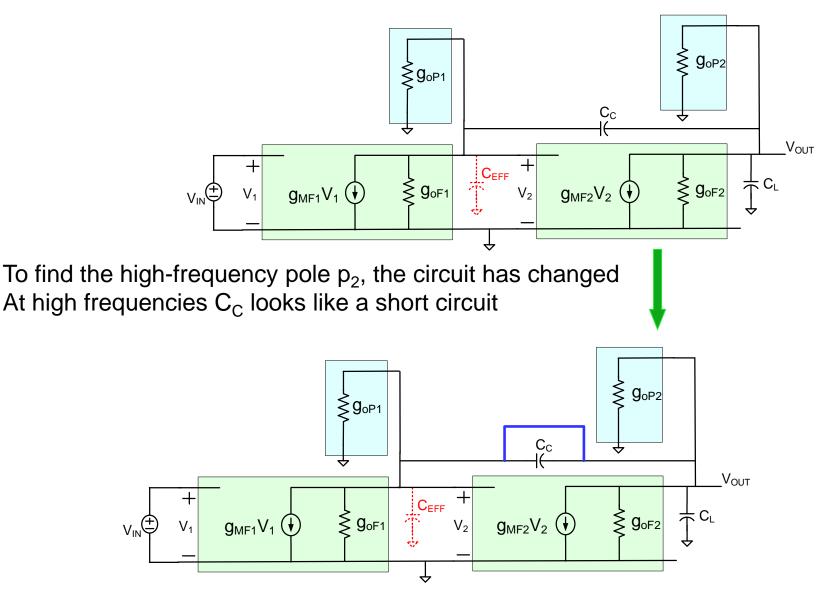

Pole Analysis of Internally Miller-Compensated Two-Stage Op Amps

Will be shown later that C<sub>C</sub> introduces a zero in the gain function

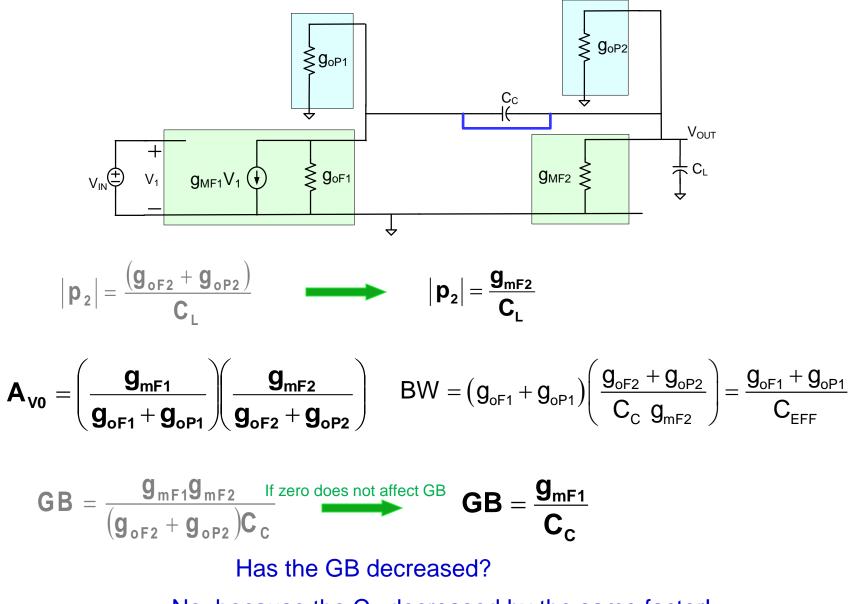

$$\mathbf{A}_{V0} = \left(\frac{\mathbf{g}_{mF1}}{\mathbf{g}_{oF1} + \mathbf{g}_{oP1}}\right) \left(\frac{\mathbf{g}_{mF2}}{\mathbf{g}_{oF2} + \mathbf{g}_{oP2}}\right) \qquad \mathsf{BW} = \left(g_{oF1} + g_{oP1}\right) \left(\frac{g_{oF2} + g_{oP2}}{C_C \ g_{mF2}}\right) = \frac{g_{oF1} + g_{oP1}}{C_{EFF}}$$

$$\mathbf{GB} = \frac{g_{mF1}g_{mF2}}{\left(g_{oF2} + g_{oP2}\right)C_C} \qquad \text{If zero does not affect GB} \qquad \mathbf{GB} = \frac{g_{mF1}}{C_C}$$

$$\mathbf{GB} = \frac{g_{mF1}g_{mF2}}{C_C} \qquad \mathbf{GB} = \frac{g_{mF1}g_{mF2}}{C_C}$$

No, because the C<sub>C</sub> decreased by the same factor!

## Basic Two-Stage Op Amp

- o Essentially just a cascade of two common-source stages

- o Same gain and pole expressions as developed for the cascade

- o Compensation Capacitor C<sub>C</sub> used to get wide pole separation

- o Two poles in amplifier

- o No universally accepted strategy for designing this seemingly simple amplifier

Pole spread  $\cong 3 \beta A_{01} A_{02}$  makes  $C_C$  unacceptably large

### Basic Two-Stage Op Amp (with Miller Compensation)

o Reduces C<sub>C</sub> by approximately A<sub>02</sub>

o Pole spread  $\simeq 3 \beta A_{01}A_{02}$  makes size of C<sub>C</sub> manageable

o One of the most widely used op amp architectures

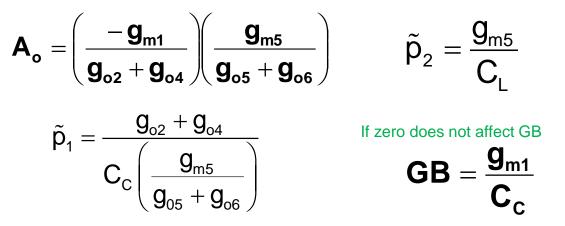

### Basic Two-Stage Miller Compensated Op Amp

**By inspection** (Notation:  $p_1 = -\tilde{p}_1$   $p_2 = -\tilde{p}_2$ )

Will also get these results from a more complete (and time consuming) analysis This analysis was based only upon finding the poles and will miss zeros if they exist

# Stay Safe and Stay Healthy !

# End of Lecture 14