# CHAPTER 10

DESIGN AUTOMATION AND VERIFICATION

# 10.0 INTRODUCTION

Design automation and design verification are the keys to effective use of large-scale integrated circuit technology today. When circuits consisted of only a few transistors or gates, layout and checking of circuits by hand were reasonable. As circuit complexity increased to thousands and tens of thousands of transistors, manual tools were no longer sufficient for design, causing computer-based design aids to become prominent. With present integrated circuits containing hundreds of thousands of transistors, heavy dependence on design automation and design verification is necessary to design these circuits.

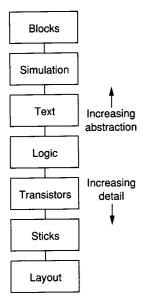

This chapter describes the nature and use of basic design automation and design verification tools as applied to the design of integrated circuits. *Design automation tools* are defined here as those computer-based tools that assist through automation of procedures that would otherwise be performed manually, if at all. Simulation of proposed design functionality and synthesis of integrated circuit logic and layout are just two examples. *Design verification tools*, on the other hand, are those computer-based tools used to verify that circuit design or layout meets certain prescribed objectives. A geometrical design rule checker for examining layout characteristics is an example, and a logic simulator with a specific set of input vectors and corresponding desired output vectors is another. Note that simulation can be classified in either category according to its purpose. Both design automation tools and design verification tools are included in the more general class known as CAD (computer-aided design) tools.

Both design automation and design verification tools require computerreadable descriptions of the underlying circuit function and structure to operate. These computer-based descriptions vary from simple geometrical specification languages such as CIF1 (Caltech Intermediate Form) to high-level functional description languages such as VHDL<sup>2</sup> (a hardware design language). Initially the focus of this chapter is on a description of design tools related to or based on geometrical layout. A simplified geometrical specification language will be examined. Required functionality provided by tools that input and display integrated circuit layout will also be described. Then, tools that check layout geometries and extract circuit net list information will be detailed.

Design tools for higher-level design description and verification are described next. Circuit, switch, and logic simulation for digital circuits are introduced and compared. Timing analysis is examined as a way to verify the temporal operation of digital circuits. Hardware design languages such as VHDL and EDIF<sup>3</sup> (Electronic Design Interchange Format) are introduced with simple examples provided to clarify important concepts.

The descriptions of design verification and design automation tools provided here use MOS examples primarily. The concepts are directly applicable to bipolar designs, although some changes in specific tool capability may be required by different technologies. The chapter concludes with an introduction to automated methods of generating layout from high-level descriptions of digital circuits via silicon compilers.

#### INTEGRATED CIRCUIT LAYOUT 10.1

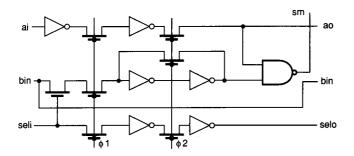

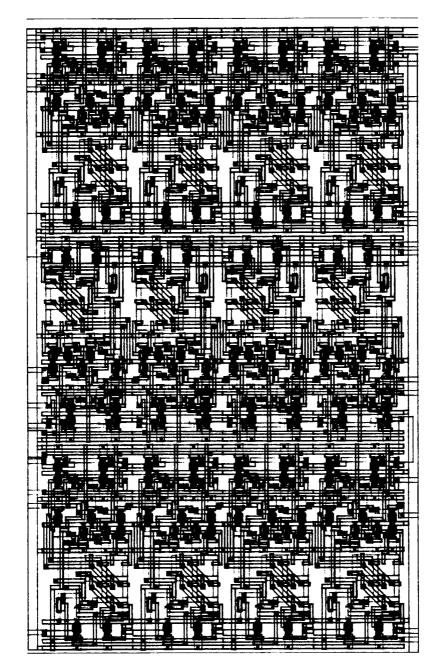

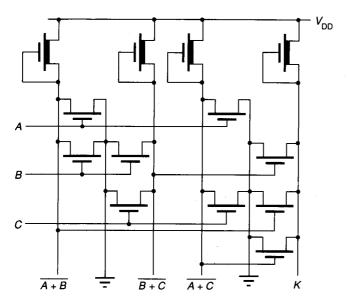

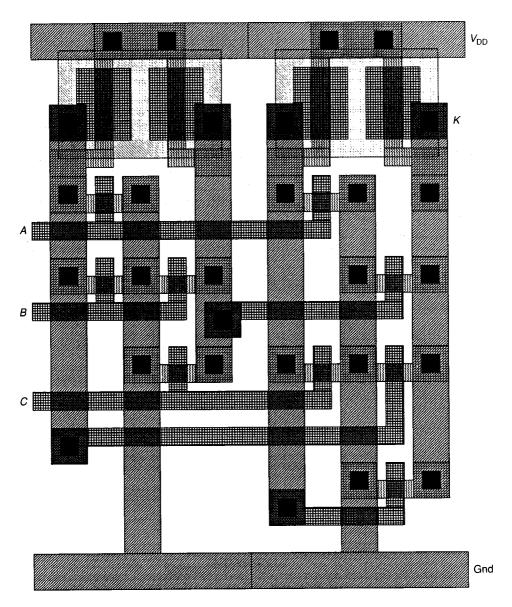

Historically, integrated circuit design and integrated circuit layout functions were performed by separate groups. The circuit design task resulted in mixed logic and transistor-level circuit diagrams describing the intended circuits. A circuit description like that of Fig. 10.1-1 was given to layout artists, who were experts at converting circuit diagrams to geometrical layouts such as the one shown in Fig. 10.1-2. For early commercial products, the layout drawings were transferred to rubylith masks by hand. Later, layouts were drawn on vellum—a tough, semitransparent drafting material—to withstand the many design modifications

**FIGURE 10.1-1** Partial circuit diagram for bit-serial multiplier of Fig. 10.1-2.

**FIGURE 10.1-2** Layout for bit-serial multiplier based on circuit of Fig. 10.1-1.

that are inherent in the normal design process. The layouts from the large vellum plots were digitized to computer-readable form to allow automated checks and to provide input to the mask-making process. Although this method worked for many years, including the early days of microprocessors, the large number of devices required in modern integrated circuits causes fully manual layout to be too time-consuming and prone to error. However, even today, critical sections of the newest microprocessors are still handcrafted to pack the circuit into the smallest possible area.

Many modern methods of integrated circuit layout include both synthesis of control logic and handcrafting of critical building blocks that will be repeated. These layout pieces are entered into a computer at an early stage to allow mechanized help with replicating, checking, and plotting the complete integrated circuit layout. Design layouts may be entered via tools that help convert graphic layout information to computer-readable form. An early tool, shown in Fig. 10.1-3, is called a *digitizer* and was used to enter layout coordinates directly into a computer from a layout plot. Sometimes layout is converted directly to text input in the form of a geometrical specification language. Most often, geometrical layout information is entered through a color graphics workstation to specify the desired integrated circuit layout.

## 10.1.1 Geometrical Specification Languages

Geometrical specification languages for integrated circuits allow computerreadable definition of the geometries for the mask layers required to fabricate an integrated circuit. These specification languages contain primitive structures such as wires and boxes to specify geometrical shapes and layout levels. Organizational constructs are also provided to allow placement and repetition of the geometrical structures. A geometrical specification language is much like a computer programming language, with the geometrical shape primitives corresponding to instructions and the organizational constructs corresponding to procedures with parameter values.

FIGURE 10.1-3 Digitizer board.

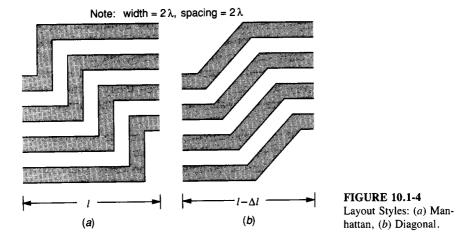

A simplified geometrical specification language for Manhattan style designs for a general MOS process is used here to illustrate relevant concepts. A Manhattan design style is one that supports only horizontal and vertical geometries. The name arises because Manhattan style layouts resemble an aerial view of the street layout of New York's Manhattan borough. This style precludes diagonal structures, such as interconnection jogs, that are sometimes used within circuit layouts to minimize area. Figure 10.1-4 shows layout styles with and without diagonal structures. The potential area savings with diagonal structures must be weighed against the increased complexity of programs used to verify the final design. Many commercial integrated circuit manufacturers allow diagonal layout structures but limit these to 45° angles from horizontal and vertical structures.

The simplified geometrical specification language defined here provides only two primitive statements. The two primitives are boxes and levels, while the organizational constructs include macros and calls. A macro is like a highlevel language (HLL) procedure, and a call is like an HLL procedure call. Table 10.1-1 provides the syntax for these primitives and organizational constructs.

All parameter values are integers. Lengths are in terms of  $\lambda$ , a measure related to the characteristic resolution of the process and the layout design rule set. Macro numbers, layout levels, and orientations are limited to positive integers. A minimum set of layers for a typical NMOS n-well CMOS process is defined in Table 10.1-2. Appendices 2A and 2B define corresponding layers for a double polysilicon NMOS and a p-well CMOS process, respectively.

**TABLE 10.1-1** Simplified geometrical specification language

| $\mathbf{B} x y dx dy$ | Box structure with length $dx$ , width $dy$ , and lower left-hand corner placed |

|------------------------|---------------------------------------------------------------------------------|

|                        | at $x$ , $y$                                                                    |

| L n                    | Layout level for the box definitions that follow                                |

| M n                    | Start of macro number n                                                         |

| Е                      | End of a macro                                                                  |

| C n x y m              | Call for macro number $n$ with translation $x, y$ and orientation $m$           |

| Q                      | End of layout file                                                              |

| -                      |                                                                                 |

| <b>TABLE</b> | E 10.1-2 | 2           |

|--------------|----------|-------------|

| MOS          | layer    | definitions |

| Layer | CMOS        | NMOS        |

|-------|-------------|-------------|

| 1     | n-diffusion | n-diffusion |

| 2     | p-diffusion | Ion implant |

| 3     | Polysilicon | Polysilicon |

| 4     | Metal       | Metal       |

| 5     | Contact     | Contact     |

| 8     | n-well      | _           |

| 9     | Overglass   | Overglass   |

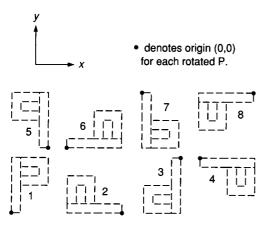

The orientation represents possible rotations of the geometrical figure after translation. The relative order of translation and rotation is important (see Prob. 10.3). Here, rotation is performed first with translation following. The possible orientations are defined in Table 10.1-3 and demonstrated with the block letter P in Fig. 10.1-5.

This simple geometrical specification language will suffice to specify any MOS Manhattan integrated circuit layout if the necessary layout levels are defined. The description is based on alphanumeric characters and is easily displayed, edited, or transferred between computer systems.

TABLE 10.1-3 Rotations of geometries

| Orientation | Description                             |

|-------------|-----------------------------------------|

| 1           | No rotation                             |

| 2           | Rotate 90° CCW                          |

| 3           | Rotate 180° CCW                         |

| 4           | Rotate 270° CCW                         |

| 5           | Mirror about y-axis                     |

| 6           | Rotate 90° CCW and mirror about y-axis  |

| 7           | Rotate 180° CCW and mirror about y-axis |

| 8           | Rotate 270° CCW and mirror about y-axis |

FIGURE 10.1-5

Cell orientations.

FIGURE 10.1-6

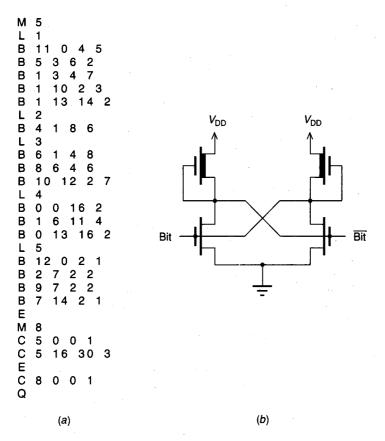

Static memory cell definition: (a) Geometrical specification file, (b) Circuit diagram.

An example of the geometrical specification file for a static memory cell composed of two inverters tied back to back is shown in Fig. 10.1-6 along with the corresponding circuit diagram. A single inverter consisting of an enhancement pulldown transistor and a depletion pullup transistor is defined by macro 5. This inverter is placed twice, once in a rotated and translated position, to create the static memory cell defined as macro 8. Macro 8 is placed once to create the layout plot shown in Fig. 10.1-7.

# 10.1.2 Layout Styles

In spite of high labor costs, handcrafted layout is still used within the semiconductor industry because of the necessity to minimize the area required by high-volume integrated circuits. Even automated layout methods such as silicon compilation and standard cell synthesis use handcrafted layout to optimize the primitive cells that are combined through automated techniques. Frequently the basic form for the integrated circuit is sketched and optimized on paper prior to entry into

FIGURE 10.1-7 Static memory cell layout.

a computer. The resulting geometrical layouts are digitized, sometimes through use of a symbolic layout language but primarily with the help of an interactive CRT graphics editor.

Handcrafted layouts can be entered directly into a computer in geometrical form through use of an interactive CRT graphics editor. A mouse or joystick is used in conjunction with a cursor to size and position geometrical objects such as boxes on a high-resolution CRT display. A corresponding data file is kept in computer memory to describe the displayed geometries. With an operator's command, this data file may be converted to a geometrical specification language description or can be saved for further use. Several advantages of this graphical editor accrue from bypassing the need to input numerical data to a computer with a text editor or digitizer and from the ease with which geometries can be changed or duplicated.

The graphics editor called Magic,<sup>4</sup> currently popular with universities, uses the painting idiom to create geometrical objects on a color CRT display. The user chooses a color (layout level) from a palette on the screen and paints areas on the screen by specifying two opposite corners of a rectangular field.

The chosen color fills the area. The final result is the same as for other layout methods: a geometrical specification file is created in computer memory, saved, and ultimately transferred to the mask shop.

Graphical editors in both industrial and university environments typically maintain their own unique memory and disk representations of layout geometries. For reasons of efficiency (fast editing response and minimum memory requirements), these representations are often highly optimized binary data structures. In the university environment, the geometrical specification language CIF was defined as a common interchange format among universities and between universities and the MOSIS fabrication service. In industry, EDIF was defined as the interchange format. Most industrial CAD tools provide conversions between their internal format and EDIF. In addition, most industrial CAD tools convert their internal format to a special binary format for submittal to the mask shop. The Berkeley Oct tool set<sup>5</sup> provides conversion from its internal format (Oct) to and from both CIF and EDIF.

In summary, both specification of layout geometries and designer entry of layout geometries are described in this section. Many different geometrical specification languages have been defined and used. A very simple one was defined here for demonstration purposes only. In the university environment, CIF is the predominant interchange format, and EDIF is the interchange standard in industry.

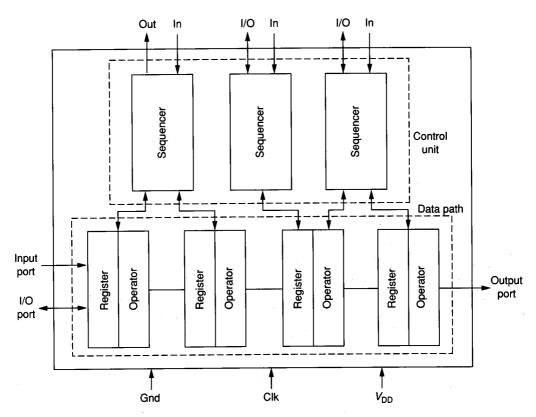

## 10.2 SYMBOLIC CIRCUIT REPRESENTATION

Descriptions of integrated circuit layouts can take many forms. The geometrical specification language of the previous section provides a primitive textual description of a circuit. Other, more symbolic, forms of representation are often used by designers to specify layouts. A hierarchy of these, including a parameterized layout representation, parameterized module generation, a graphical symbolic representation, and logic equations, is described here.

# 10.2.1 Parameterized Layout Representation

A symbolic layout language<sup>1</sup> (SLL) allows a textual description of circuit layout in a form that is more easily generated and understood by humans than the geometrical specification language of the previous section. In the past, an SLL was used to represent design layouts that were drawn by hand on graph paper and then digitized. Two main characteristics differentiate an SLL from the geometrical specification language described previously. First, the SLL uses descriptive identifiers for the parameters necessary to specify a geometrical layout. Examples are BOX, POLY, and DX for the geometrical shape, the layer, and the width in the x direction, respectively. This provides a readable description of geometries that specify a layout. Thus, the SLL description is easily entered into a computer using the designer's favorite text editor. Second, symbolic entries are allowed in addition to the numerical data of the geometrical specification language. For example, the x and y position of a geometry might be specified by the variables XPOINT and YPOINT. This allows the final placement of the geometry to depend on the

placement of other cells. At some point in the design process, the SLL must be converted to a geometrical specification language for use by other CAD tools and for transmittal to the mask shop. XPOINT and YPOINT must be assigned numerical values to specify the location of the geometry before this conversion takes place.

In addition to the use of symbolic parameters in an SLL, programming constructs such as loops and conditionals can provide additional capability in the specification of a cell's layout. The use of an SLL to describe layout is much like the use of assembly language to describe the machine language (binary) program for a computer. An assembly language program uses mnemonics for the instructions and symbols for variables to simplify and expedite the process of programming a digital computer. Both forms describe the same end object; the binary representation provides the most concise description, while the assembly language is a preferable working medium for programmers.

An SLL description for the layout of the CMOS inverter of Fig. 7.5-5 is given in Fig. 10.2-1. Note the verbose nature of this description compared to the geometrical specification file of Fig. 10.1-6. The description of Fig. 10.2-2 demonstrates the use of variables to allow the inverter cell of Fig. 7.5-5 to be stretched in either the VERT (vertical) or HORZ (horizontal) directions. Also, a REPEAT statement is included to allow the cell to be repeated NR times. RX and RY are the repeat distances along the x and y axes, respectively. If the variables VERT and HORZ are each set to a value of 0 and NR is set to 4, the inverter cascade of Fig. 10.2-3 is produced. The two variables VERT and HORZ can be used to stretch the inverter cell to match the pitch of adjacent cells by

```

CELLNAME CMOSINV;

BOX NDIF X=3 Y=0 DX=4 DY=4;

BOX NDIF X=3 Y=4 DX=2 DY=4

BOX NDIF X=3 Y=8 DX=4 DY=4:

BOX PDIF X=3 Y=20 DX=4 DY=4;

BOX PDIF X=3 Y=24 DX=5 DY=4;

BOX PDIF X=3 Y=28 DX=4 DY=4;

BOX POLY X=0 Y=5 DX=7 DY=2:

BOX POLY X=0 Y=7 DX=2 DY=18

BOX POLY X=0 Y=25 DX=10 DY=2;

BOX POLY X=4 Y=14 DX=8 DY=4:

BOX MET1 X=0 Y=0 DX=12 DY=4:

BOX MET1 X=0 Y=28 DX=12 DY=4:

BOX MET1 X=3 Y=8 DX=4 DY=16;

BOX MET1 X=7 Y=14 DX=1 DY=4;

BOX CONT X=4 Y=1 DX=2 DY=2;

BOX CONT X=4 Y=9 DX=2 DY=2;

BOX CONT X=5 Y=15 DX=2 DY=2;

BOX CONT X=4 Y=29 DX=2 DY=2:

BOX CONT X=4 Y=21 DX=2 DY=2:

BOX NWEL X=0 Y=18 DX=12 DY=16;

END CMOSINV:

```

Figure 10.2-1 Symbolic layout language description of CMOS inverter of Fig. 7.5-5

```

CELLNAME CMOSINV;

BOX NDIF X=3 Y=0 DX=4 DY=4;

BOX NDIF X=3 Y=4 DX=2 DY=4;

BOX NDIF X=3 Y=8 DX=4 DY=4;

BOX PDIF X=3 Y=20 DX=4 DY=4;

BOX PDIF X=3 Y=24 DX=5 DY=4;

BOX PDIF X=3 Y=28 DX=4 DY=4+VERT;

BOX POLY X=0 Y=5 DX=7 DY=2;

BOX POLY X=0 Y=7 DX=2 DY=18;

BOX POLY X=0 Y=25 DX=10 DY=2;

BOX POLY X=4 Y=14 DX=8+HORZ DY=4;

BOX MET1 X=0 Y=0 DX=12+HORZ DY=4;

BOX MET1 X=0 Y=28+VERT DX=12+HORZ DY=4;

BOX MET1 X=3 Y=8 DX=4 DY=16;

BOX MET1 X=7 Y=14 DX=1 DY=4;

BOX CONT X=4 Y=1 DX=2 DY=2;

BOX CONT X=4 Y=9 DX=2 DY=2;

BOX CONT X=5 Y=15 DX=2 DY=2;

BOX CONT X=4 Y=29+VERT DX=2 DY=2;

BOX CONT X=4 Y=21 DX=2 DY=2;

BOX NWEL X=0 Y=18 DX=12 DY=16+VERT;

END CMOSINV;

CELLNAME FOURINV;

REPEAT CMOSINV NR=4 RX=12+HORZ RY=0;

END FOURINV;

```

#### **FIGURE 10.2-2**

Parameterized symbolic layout language description for inverter cascade of Fig. 10.2-3

# **FIGURE 10.2-3**

Inverter cascade created from parameterized symbolic layout language description.

specifying positive values for one or both of VERT and HORZ. The use of a programmatic description of layout greatly expands the capabilities of a layout designer in specifying the geometrical structure of a circuit.

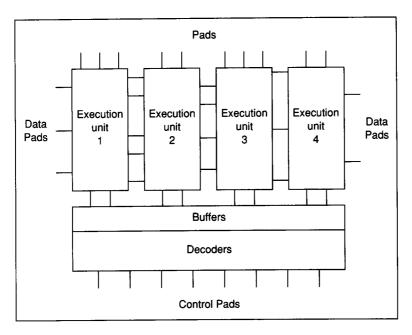

## 10.2.2 Parameterized Module Generation

A recent advance in the area of symbolic layout descriptions is the use of parameterized module generators. A parameterized module generator is a software procedure that can generate many different cell layouts depending on values that are specified when the generator program is executed. Parameterized module generators have been written for RAMs, ROMs, PLAs, multipliers, adders, and data paths, for example. Many of these generators use input parameters to specify the width or number of bits in the generated layout.

As an example, three separate designs might require an 8-bit adder for the first design, a 16-bit adder for the second design, and a 32-bit adder for the third design. Typical design style would use an interactive graphics editor to create each of these adders separately. If a parameterized generator for the adder module could be defined, however, a single module generator could be used to produce an N-bit adder where N is a parameter that can be set to 8, 16, 32, or some other integer value. Then each of the three adders could be created from the same parameterized description. A parameterized module generator is particularly well suited to modern integrated circuit design styles, which commonly utilize regular structures such as rows of cells and arrays of cells.

Parameterized module generators use many of the powerful constructs of high-level programming languages to describe layout structure, position subcells, and fit the overall layout of a larger cell together. Parameterized variables are used with their values bound to a specific value when a module is generated. Conditional statements allow creation of specialized edge cells and programming of memory and PLA contents. For example, a parameterized module generator for an array of cells might include conditional statements such that if both the x and y indices were equal to 0, then an upper-left corner cell would be generated. If the x and y indices were each between the smallest and largest values, a center cell would be generated, and so forth.

The use of high-level programming language techniques also provides a disadvantage for many parameterized module generators. That is, the layout cannot be visualized until the generation program has been compiled and linked to instantiate the layout for a module. These potentially time-consuming steps may hinder the use of interactive layout in designing a module generator for a new cell. To circumvent this problem, there is ongoing research on ways to provide interactive graphical feedback as the geometrical structure of a cell is defined.<sup>6</sup>

With such a tool, a silicon layout specialist can create the parameterized modules that are required in a design. Then a circuit or logic designer can use these blocks by specifying parameters appropriate to the design task. Recently, parameterized module generators were used to specify the layout of a commercial RISC processor (see Sec. 10.11). An interesting, but unsolved problem, is to prove that the output of a parameterized module generator is correct over the valid range of parameters for the module generator.

## 10.2.3 Graphical Symbolic Layout

The parameterized layout representation described previously provides little insight into the geometrical relationships between circuit elements. This important insight can be provided by another symbolic form for integrated circuit description, called graphical symbolic layout. An early form of graphical symbolic layout is called Sticks. Sticks and related symbolic methods provide an abbreviated, graphical description that combines circuit connectivity with layout topology information. In the Sticks symbology, circuit connections are shown with colored (or weighted) lines representing layout levels, while transistors are formed by the intersection of the lines representing polysilicon and diffusion. The entire layout diagram is composed of simple line symbols that show both connectivity and topology but not actual or relative size for geometrical constructions.

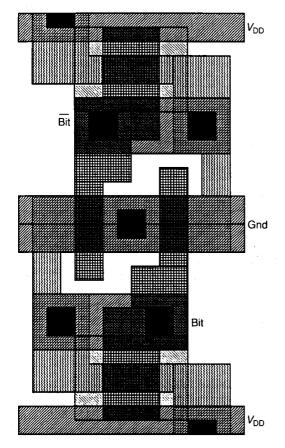

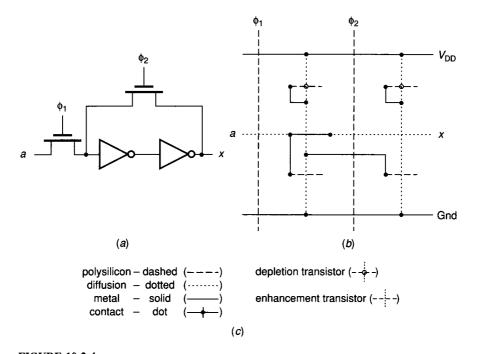

The combination of connectivity and topological information is important in the generation of integrated circuit layouts, as is shown with the aid of the circuit diagram for the quasi-static memory cell of Fig. 10.2-4a. This circuit diagram shows a forward path from the first inverter to the second inverter and a clocked feedback path from the second inverter to the input of the first inverter. The circuit diagram does not indicate topological requirements to realize this path.

The geometrical layout of the memory cell of Fig. 10.2-4a requires decisions on changes of layout levels to prevent unwanted transistors and connections. The Sticks diagram of Fig. 10.2-4b retains all the circuit connectivity information

**FIGURE 10.2-4**

Quasi-static memory cell: (a) Logic diagram, (b) Symbolic diagram for NMOS layout, (c) Layer legend.

for the memory cell and also symbolically specifies the topology of the final integrated circuit layout. In particular, it shows that the feedforward path must be changed from the diffusion layer to the metal layer to cross the polysilicon  $\phi_2$ clock line without creating an unwanted transistor. Also, the Sticks diagram shows that the feedback transistor is conveniently formed by allowing the polysilicon  $\phi_2$  line to cross the diffusion feedback path. The diagram shows that power and ground are provided in metal and that the input and output signals are both in the diffusion level. The utility of Sticks and other graphical symbolic layout methods is derived from the simple abstracted notation for layout topology and circuit description.

Once a graphical symbolic layout for a circuit is generated, it is often simple for a designer to convert to a full layout form. The layout task has been simplified to the process of fattening connection lines and compacting the layout, especially if required transistor length-to-width ratios have been noted on the graphical symbolic layout. In fact, this process is simple enough to be automated. 8 If the graphical symbolic layout description has been entered into a computer, perhaps through an interactive graphics terminal, a symbolic compiler program can convert the symbolic layout to a full layout by expanding the line symbols according to a technology specification and then compacting the resulting layout.

As with most automated layout aids, a symbolic compiler usually trades reduced designer efforts for increased silicon area. An increase in the area for a layout generated with a program is not uncommon when compared to a handcrafted layout. As a result, high-volume integrated circuits such as microprocessors and memory continue to utilize handcrafted layout of replicated cells as a major design component. This does not, however, minimize the value of the symbolic representation to the designer. Capturing layout topology in symbolic form early in the layout design prevents later problems such as isolation of a circuit from direct metal connection to power buses.

# 10.2.4 Logic Equation Symbology

If the function of a digital integrated circuit can be captured by a set of Boolean logic equations, these equations suffice to generate an integrated circuit layout. Thus, logic equations represent a fourth symbolic means to describe a combinational logic circuit. One frequently used means to convert logic equations into layout topology is with a PLA generator, as described in Chapter 9. Two other methods for generating geometrical layouts from logic equations are discussed next: the Weinberger array<sup>9</sup> and SLAP<sup>10</sup> (a methodology for silicon layout).

A Weinberger array uses a regular structure of NOR gates to implement combinational logic in an integrated circuit form. This array structure was introduced in Chapter 9. Figure 10.2-5 shows a Weinberger array used to implement the full adder carry function described by

$$K = AB + AC + BC \tag{10.2-1}$$

Since the final structure is regular, it is not difficult to construct a computer program to generate the array layout using logic equations as program input. By

FIGURE 10.2-5 Weinberger array for full-adder carry.

use of DeMorgan's theorem, any combinational logic function can be realized using only NOR gates. In fact, the Weinberger array requires at most a series path of three NOR gates between an input and an output to realize a combinational logic function. Remember that a single-input NOR gate is an inverter. Thus, a first NOR gate may be required to provide the complement of an input while the final two levels use the NOR-NOR logic form to realize the logic function in product-of-sums form.

The use of NOR gates for a Weinberger array allows a constant size for the pullup devices even though the number of inputs and their corresponding pulldown devices may differ for each gate. Careful design allows adjacent gates to share a single ground path, as shown in the layout of Fig. 10.2-6. This array structure can be easily expanded by adding input variables at the bottom and NOR gates to the right without changing the existing structure.

A comparison of the Weinberger array with the PLA yields an interesting result. Even though the logic of a PLA is realized entirely with NOR gates, the AND-OR logic form corresponding to a sum-of-products description is normally used. The AND-OR logic form can be realized with NOR gates only by inverting both the inputs and outputs. This requires a series string of four or five NOR gates between the PLA inputs and outputs, thus causing more delay for a PLA implementation of logic than for a Weinberger array implementation which requires only three levels of logic.

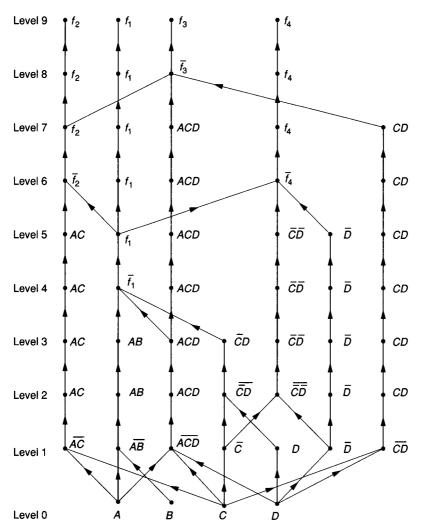

In contrast to the PLA and the Weinberger array, both with predefined array structures, a third method called SLAP has been proposed to compile logic equations into layout form. SLAP first converts logic equations into a directed graph with a graph level for each level of the logic equations. If double-rail inputs

FIGURE 10.2-6 Layout for Weinberger array.

are available, at least two levels of gates are required to implement a general logic function. The SLAP methodology, however, allows realization of intermediate outputs that may then be used as inputs for other logic functions. A graph with an arbitrary number of levels may be required, depending on the particular representation for the logic. Figure 10.2-7 shows the directed graph for the logic functions of the following equations.

FIGURE 10.2-7 Directed graph for Eqs. 10.2-2 through 10.2-5.

$$f_1 = AB + \overline{C}D + ACD \tag{10.2-2}$$

$$f_2 = AC + f1 (10.2-3)$$

$$f_3 = ACD + CD + f_2 \tag{10.2-4}$$

$$f_4 = \overline{C}\,\overline{D} + \overline{D} + f_1 \tag{10.2-5}$$

This directed graph is formed by placing logic gates with external inputs at the first level, secondary logic gates at the next level, and so on. Heuristics are then used to improve the organization by reducing the number of required levels, if possible, and to reduce the resulting layout area required. The layout density achieved with this method is about the same as that accomplished with gate array

structures. An important characteristic of the SLAP methodology is that general logic structures can be compiled directly into a geometrical layout, whereas the PLA format forces a two-level logic realization.

In this section, four methods of generating layout from symbolic representations were introduced. Of the first two, parameterized layout representation and parameterized module generation, the second is growing in popularity for layout of today's designs. Graphical symbolic layout also enjoys success as a technique for layout of random logic. Synthesis of layout directly from the fourth symbolic form, logic equations, is fast becoming a widely used technique for generating integrated circuit layout.

## 10.3 COMPUTER CHECK PLOTS

Generation of a layout plot from a geometrical specification file for an integrated circuit is often desirable. In the past, large-scale plots, some almost big enough to cover one end of a basketball court, were generated so that visual checking of circuit layout could be performed. Most of these visual checks can now be performed directly from a computer-based geometrical specification file without manual intervention. A computer program can verify fixed rules for the millions of geometrical figures used to describe VLSI circuits without tiring and without error — a task that is essentially impossible for humans. However, human capability to critique overall structure or to detect inconsistencies in an otherwise regular design is difficult to duplicate with computer-based checks. As a result, hardcopy plots of integrated circuit designs are still used for finding errors, for promotional literature, and for many other purposes. Such plots are called computer check plots.

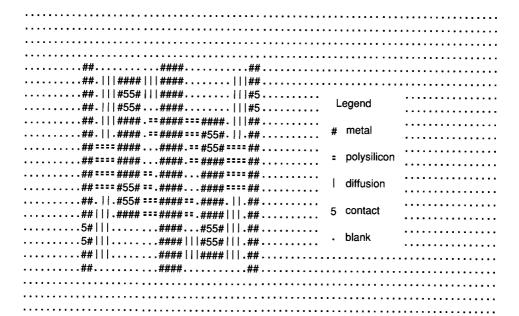

Computer check plots for integrated circuit designs are created in both soft- and hardcopy form on CRTs, printers, and plotters using color or black on white representations for the layout artifacts. Check plot devices range from monochrome CRTs, with only 24 × 80 character resolution for the entire display, to laser printers with 300 dots per inch or higher resolution. To compare the maximum usable display capability over this range of resolution, an example using a static memory cell is examined next.

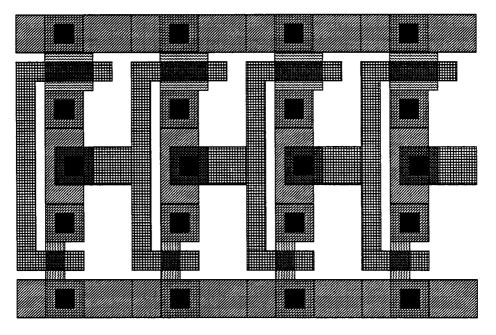

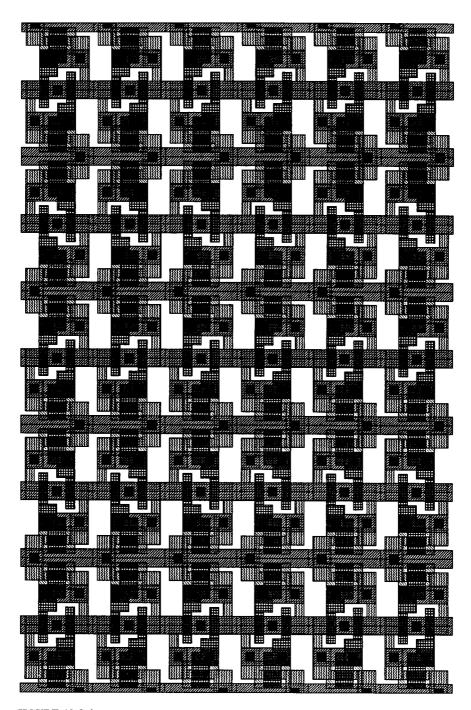

The static memory cell of Fig. 10.1-7 has dimensions of 16  $\lambda \times 30 \lambda$  for an area of 480  $\lambda^2$ . A monochrome alphanumeric CRT using character graphics with 24 lines by 80 columns can display an area of 1920  $\lambda^2$ , although the effective area is somewhat less because of the 1:3 aspect ratio of the CRT display resolution. All details of the static memory cell are visible in the CRT display, as shown in the hardcopy plot of Fig. 10.3-1, but the cell's relation to other cells is lost. As a second example, a dot matrix drawing normally requires a resolution of at least 5 dots per  $\lambda$  to define the smallest details of a circuit. For a printer with a resolution of 100 dots per inch, the static memory cell requires a plot that is about  $0.8 \times 1.5$  in. to show the details of the circuit. Figure 10.3-2 provides a plot of this size for the memory cell of Fig. 10.1-7. If the memory cell were part of a 1K-bit memory (32 cells × 32 cells), a high-resolution plot of the entire memory array would require 25.6 × 48 in. Of course, the general form of the memory area could be discerned with a much smaller plot. Figure 10.3-3 shows a plot at one-tenth this scale  $(2.56 \times 4.8 \text{ in.})$  for the 32-by-32 cell array.

#### **FIGURE 10.3-1**

Hardcopy plot of SRAM cell as displayed on 24 line by 80 character CRT ( $\lambda$  = one character width).

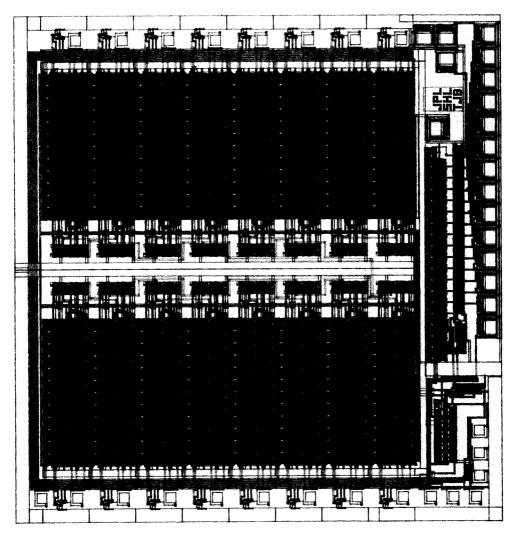

A typical graphics CRT display with a 19 in. diagonal screen (15 in. horizontal  $\times$  11 in. vertical) might have a resolution of 760 by 480 dots. This is roughly 50 dots per display inch. Based on the analysis above, the details of a 152  $\lambda$  by 96  $\lambda$  circuit could be displayed in its entirety on the screen. This would correspond to about a five-by-six array of the memory cells described above. Figure 10.3-4 shows a hardcopy plot of the memory cells that could be seen on the CRT display. Of course, an entire chip can be displayed if the layout is scaled so that the finer details of the chip are lost. Figure 10.3-5 shows the entire layout for a 220  $\times$  230 mil image-processing chip composed of sixteen, 12-bit serial multipliers with associated circuitry and input/output pads.

Color displays and plots are always a higher-cost feature than black and white; where color is available, each integrated circuit layer is represented using

FIGURE 10.3-2 Minimum size plot for Fig. 10.1-7 with 100 dots/inch resolution.

FIGURE 10.3-3 Plot of  $32 \times 32$  memory cell array.

a different color. Aside from their aesthetic appeal, color renditions of circuits show higher information content per unit area, allowing display of larger circuits in a given area. For a color display, only 2 to 3 dots per  $\lambda$  of resolution are necessary to delineate circuit details. Additionally, individual color levels can be used to show labels, flag geometrical design rule violations, or highlight specific features of a circuit. Most modern graphics workstations provide color displays.

When black on white plots are generated, two primary methods are used to distinguish individual layers. Line drawings, with each layer represented by a different style of line (solid, dotted, dashed, dot-dash, etc.) are producible on almost any printer with dot graphics capability (see Fig. 10.3-6). Filled drawings with different layers shown by characteristic area fill pattern (fine dots, heavy dots, diagonal lines, vertical lines, etc.) are popular, even at the expense of increased computer time to generate the plots, greater wear on the printer mechanism, and longer time to print the plots. Laser printers provide good resolution

FIGURE 10.3-4

Hardcopy plot of memory cells visible on typical graphics CRT display.

**FIGURE 10.3-5** Image-processing chip (220 mil × 230 mil).

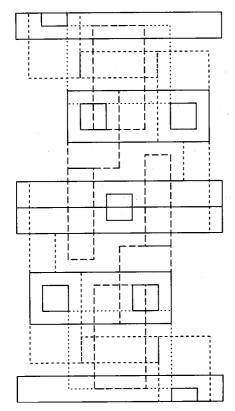

(300 dots per inch) and are frequently used for area fill check plots. A primary advantage of the filled drawing of Fig. 10.1-7, compared with the line drawing of Fig. 10.3-6, is that the concept of area for integrated circuit layers is quickly conveyed to the viewer by the filled drawing. This concept is important to the designer since the fabrication process operates on contiguous areas rather than the individual boxes used to describe them.

In this section, a short summary of integrated circuit display media and their corresponding resolution requirements was presented. It is important to have highresolution display and hardcopy capability for integrated circuit layout design.

FIGURE 10.3-6 Line check plot of layout of Fig. 10.1-7.

## 10.4 DESIGN RULE CHECKS

Integrated circuits are created from several layers whose geometrical structures are defined by photolithographic masks. At any given time, a minimum resolution exists for the structures that can be fabricated on silicon because of lithographic and processing constraints. Any attempt to define structures that require higher resolution or accidental specification of a higher resolution through carelessness may lead to nonfunctional circuits. Also, violation of certain geometrical relationships among layers may cause failures because of processing constraints. For each process, a set of guidelines called *design rules* is specified to encapsulate geometrical fabrication constraints. The design rules for the CMOS process described in Table 2B of Appendix 2 are used as the basis for the following discussion. However, most of the rules are determined by general lithographic and processing constraints so that similar rules apply to other processes as well.

# 10.4.1 Geometrical Design Rules

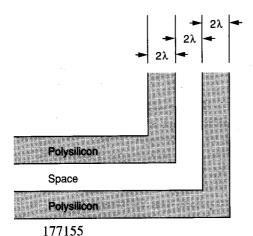

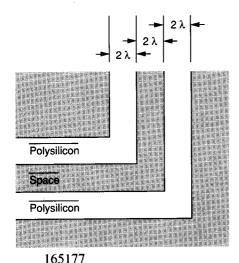

A conceptual explanation of geometrical design rules is provided in this section. Design rules were introduced in Sec. 2.3 of this text. Geometrical design rules for a single integrated circuit layer are simple; they involve only spacings and widths. Figure 10.4-1 demonstrates a 2  $\lambda$  spacing between polysilicon conductors

FIGURE 10.4-1 Minimum width polysilicon conductors.

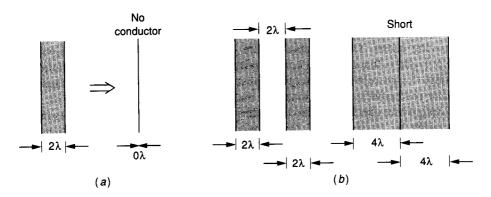

that are each  $2\lambda$  wide. It is worth noting that if a mask layer is complemented, all widths become spacings. This is shown in Fig. 10.4-2, where the complemented polysilicon conductor widths from Fig. 10.4-1 appear as spacings. Therefore, if width is considered in terms of the complement of the layer definition, all single-layer rules can be treated as simple spacing rules. This means that the same computer algorithm can be used to check for both width and spacing errors.

An interesting conceptual understanding of design rules was provided by Lyon. It is explanation is based on the scalable parameter  $\lambda$ , which is said to describe the minimum resolution of the fabrication process. In practice, fabrication processes are usually characterized by their minimum transistor length. The parameter  $\lambda$  is normally specified as half the minimum transistor length. Thus, a 2  $\mu$  process has a minimum gate length (and width) of 2  $\mu$ , and  $\lambda$  would be set to 1  $\mu$ . Thus,  $\lambda$  is not directly a measure of process resolution, but rather is proportional to the minimum device length. With this in mind, the following two meta rules (a meta rule is a rule about rules) were proposed by Lyon to generalize geometrical design rules in terms of  $\lambda$ .

FIGURE 10.4-2 Complemented layout, where spacings become widths.

- 1. A 1  $\lambda$  error should not be fatal, although the intended performance of the integrated circuit may be degraded.

- 2. A 2  $\lambda$  error may be fatal and almost certainly will degrade the performance of the integrated circuit.

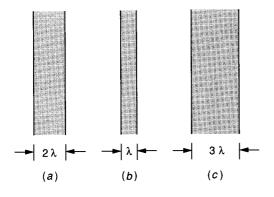

Consider the minimum width of 2  $\lambda$  for the polysilicon conductor shown in Fig. 10.4-3a. If the width of the actual polysilicon that is fabricated on the chip is 1  $\lambda$  less than this minimum, as in Fig. 10.4-3b, the polysilicon will still conduct, although its resistance will double. If the fabricated polysilicon conductor is 1  $\lambda$ wider than the minimum, as in Fig. 10.4-3c, the resistance is lowered, but the polysilicon still functions as a conductor. Thus, a change in width of 1  $\lambda$  does not cause an obviously fatal problem for the polysilicon interconnection.

Now consider a 2  $\lambda$  deviation from the design width of 2  $\lambda$ . If a minimum width polysilicon conductor is narrowed by  $2\lambda$ , as in Fig. 10.4-4a, there is no conductor left-certainly a fatal error unless the connection was redundant. If the width is increased by 2  $\lambda$  as in Fig. 10.4-4b and the minimum polysilicon spacing is  $2\lambda$ , there is a chance that the polysilicon conductor will contact an adjacent polysilicon conductor, causing a short circuit—also a fatal error.

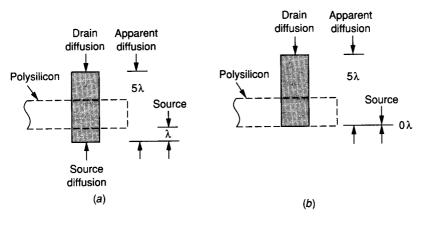

Other design rules involve more than one level and are harder to remember and to verify. As an example of a two-level rule, consider that a transistor is created by the area common to polysilicon and diffusion. This transistor area must satisfy the 2  $\lambda$  minimum length rule, so the smallest transistor size is 2  $\lambda$  by 2  $\lambda$ . The diffusion areas for the source and drain of a transistor also must satisfy a 2  $\lambda$  minimum length. This rule is sometimes confusing from a layout viewpoint since the source, the drain, and the transistor gate area appear as one contiguous diffusion area. Thus, a source area 1  $\lambda$  long combined with a transistor area 2  $\lambda$ long and a drain area 2  $\lambda$  long, shown in Fig. 10.4-5a, appears as a diffusion area 5  $\lambda$  long and does not seem to violate the 2  $\lambda$  diffusion length rule. However, Fig. 10.4-5b shows that a source only 1  $\lambda$  long could disappear as a result of a 1  $\lambda$  alignment error between polysilicon and diffusion—thus a 2  $\lambda$  rule must be specified for the transistor source/diffusion dimensions. Typical design rule sets for several processes, including NMOS and CMOS, are provided in Appendix 2.

**FIGURE 10.4-3** DRC degradation meta rule.

FIGURE 10.4-4 DRC fatality meta rule.

# 10.4.2 Computer Design Rule Checks

If a designer creates or changes a geometrical specification file manually, a design rule check (DRC) is required. Because of the large number of geometries and the wide variation in number and style of geometrical design rules in today's circuits, computer-based DRCs are necessary. Two different styles of DRC programs are in wide use. These can be categorized as polygonal checks and raster scan checks. Both styles will be described briefly.

Polygonal design rule checks are widely used within the semiconductor industry. The geometrical specification file is expanded to produce polygons defining all connected areas for the layer(s) of interest. Note that the layer of interest may be a composite area such as active transistor area or perhaps depletion transistor area. Or it may be a difference area such as the ion implantation overhang created by subtracting the depletion transistor area from the ion implan-

FIGURE 10.4-5 Transistor source width.

tation area. These special areas can be defined by logical operations on primitive layers. Once the polygonal definitions are formed, they can be analyzed for width and spacing errors. One valuable feature of encircling a connected area with a single polygon is that electrical connectivity information is immediately available. Polygonal design rule checks require substantial computing resources because of the many mathematical operations that must be performed during the check.

Design rule checks can also be performed in a relatively simple way as raster scan checks by passing small filters over a rasterized image of the integrated circuit. To allow this, an entire geometrical specification file is instantiated (expanded into the geometries and layers that represent the layout) within a twodimensional array where the dimensions represent the x and y coordinates of a point and the contents are binary variables to indicate the presence or absence of each layout level. The resolution of the x and y coordinates limits the precision of the design rule checks. Filters such as a 4 × 4 array, <sup>12</sup> a "plus" symbol, or a circled "plus" symbol<sup>13</sup> have been used to scan the instantiated layout to check for design rule violations. These methods are conceptually simple and computationally clean, but lack the accuracy and connectivity information of the polygonal methods.

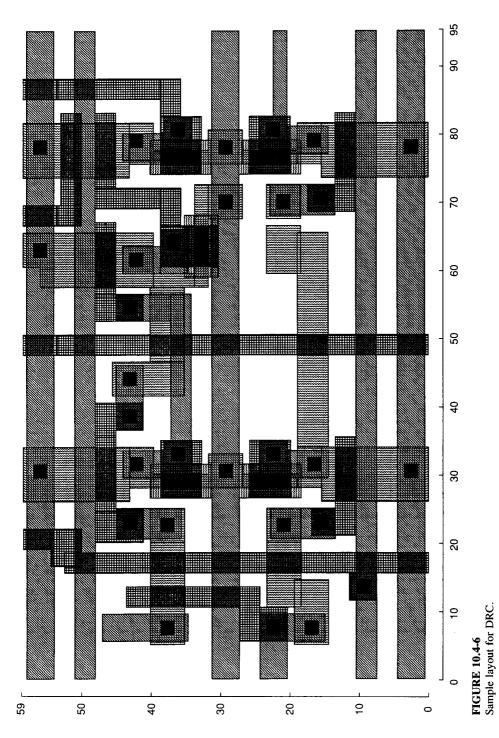

# 10.4.3 Design Rule Checker Output

To demonstrate the results from a raster scan DRC program, several errors were placed in a geometrical specification file. The layout for this file is shown in Fig. 10.4-6. The resulting output from the DRC program is shown in Fig. 10.4-7. The DRC program outputs a heading that gives the name of the file, the date and time, the bounding box coordinates for the checked area, and the macro number. Below the heading, a list of all vertical and horizontal errors is provided. This particular sample contains three vertical and four horizontal errors. Each violation is shown by a one-line entry containing the identification of the violated rule, the x and y coordinates of the violation, the violation or error distance, and the length over which the violation occurred. The resolution of the layout of Fig. 10.4-6 and the DRC results of Fig. 10.4-7 is 0.5  $\lambda$ .

Definitions of the seven rule violations from Fig. 10.4-7 are given in Table 10.4-1. In each case these errors involve a spacing violation. For example, Rule 6.2 is a metal spacing error. A glance at the upper left corner of Fig. 10.4-6 shows a T formed by a long horizontal metal section and a short vertical metal section separated from the horizontal metal (top of the T) by about 1  $\lambda$ . From Rule 6.2, the spacing must be at least 3  $\lambda$  unless the two metal sections should be joined, in which case the spacing would be zero. As an exercise, the reader should find the location of each of the errors listed in Fig. 10.4-7.

Once the cause of an error is determined, corrective action must be initiated. Since the DRC output gives the exact x and y coordinates of the violation, it is usually relatively simple to use an interactive graphics CRT to display the error. Actually correcting the error may not be so simple. If the layout is loosely packed, correction in place by adjusting a single geometrical figure can possibly be done. For some layouts, however, an error will occur in a space-critical area,

#### LDRC version 3.115

Design rule check of file: BGA.TAM Date 9-MAR-89 Time 21:08:05 X min = 0.0 X max = 95.0Y min = 0.0 Y max =59.0

Macro name is BGMLT Macro number is 99

#### Vertical errors

| Rule | X loc | Y loc | Error | X len |

|------|-------|-------|-------|-------|

| 6.2  | 5.5   | 47.5  | 1.0   | 4.0   |

| 5.3  | 22.0  | 17.0  | 0.5   | 2.0   |

| 6.1  | 82.5  | 20.5  | 1.0   | 12.5  |

Vertical error count: 3

#### Horizontal errors

| Rule | X loc | Y loc | Error | X len |

|------|-------|-------|-------|-------|

| 4.3  | 10.5  | 20.5  | 0.0   | 3.0   |

| 4.2  | 18.5  | 41.5  | 0.5   | 7.0   |

| 1.2  | 66.5  | 18.5  | 1.0   | 5.0   |

| 5.6  | 80.0  | 41.5  | 1.0   | 2.0   |

Horizontal error count:

Total number of Design rule violations:

Design-Rule Checker Execution:

CPU Time 0: 0:26.06 Page Faults 354

**FIGURE 10.4-7**

DRC output for Fig. 10.4-6.

requiring changes of a large number of geometries. For this reason, it is crucial to generate a correct layout through automatic means or, in the case of a handcrafted design, to check the layout frequently for geometrical design-rule errors as it is generated. With care, errors are caught early before correction causes difficult problems.

**TABLE 10.4-1** Design rule error definitions

| Rule | Length | Definition                       |

|------|--------|----------------------------------|

| 1.2  | 3 λ    | Diffusion spacing                |

| 4.2  | 2 λ    | Polysilicon spacing              |

| 4.3  | λ      | Polysilicon-to-diffusion spacing |

| 5.3  | λ      | Polysilicon larger than contact  |

| 5.6  | λ      | Metal larger than contact        |

| 6.1  | 3 λ    | Metal width                      |

| 6.2  | 3 λ    | Metal spacing                    |

The DRC program used here was run in the batch mode on a computer after the layout was complete. Many CAD systems allow DRCs as geometries are entered through an interactive graphics CRT using an incremental DRC program. Either the designer is prevented from placing geometries that would violate design rules, or a pending violation is flagged immediately by an error message. This minimizes the need for major changes after the layout is almost complete.

DRCs are one of the more time-consuming, yet important, design verification steps. Both polygonal and raster scan DRCs are possible. A good DRC program provides output that accurately identifies the type and location of each error. A good interface between the DRC program and an interactive graphics editor is important for displaying and correcting DRC errors.

## 10.5 CIRCUIT EXTRACTION

After the design and layout process is complete, MOS circuits are characterized by a machine-readable specification prior to the mask-making step. This specification is usually a geometrical specification file as described earlier. This file contains all the information about the geometries, levels, and placements for the circuit to be fabricated. Because geometrical specification files contain large quantities of detailed information about the integrated circuit, it is difficult for a designer to determine whether this information accurately describes the circuit that was intended. Fortunately, computerized methods exist to extract the circuit information from the geometrical specification file. The process of extracting the circuit information from the geometrical description is called *circuit extraction*.

A circuit extraction program expands the geometrical specification file of the integrated circuit into a layer-by-layer description of the geometries and their placements. This description is then scanned to locate all transistors and interconnections for the circuit. A result of the circuit extraction program is a net list. A *net list* is a set of statements that specifies the elements of a circuit (for example, transistors or gates) and their interconnection. Individual transistors are described along with the nodes to which they connect. This information allows creation of a circuit diagram based on the actual geometrical specification file. Most importantly, the extracted circuit can be compared with the original circuit specified by the designer so that differences are annotated. A difference usually indicates an error that must be corrected. This comparison is called an LVS (layout versus schematic) design verification step.

In addition to providing the details of circuit interconnections, circuit extraction is useful for calculating layout areas and perimeters for each integrated circuit layer at each node of the circuit. These layout areas and perimeters can be used to accurately calculate the parasitic capacitances and resistances that load the active devices. Prior to the layout and extraction step, most circuit parasitics can only be estimated by the designer. With accurate capacitance and resistance values from circuit extraction, a design can be accurately simulated to ensure correct operation. Thus, circuit extraction is an essential design verification tool for accurate characterization of modern integrated circuits.

## 10.5.1 A Simple Circuit Extraction Algorithm

One simple method of circuit extraction consists of two main steps. First, the geometrical specification file is instantiated as a set of coordinates and levels within a computer memory. This is essentially the same operation that was required for the raster scan DRC described in the previous section. This method requires a large computer memory to store the integrated circuit levels at a resolution matching the smallest features of the integrated circuit. For example, a 5 mm by 5 mm die using a process with a  $\lambda$  of 1  $\mu$  could require over 25 million individual memory locations to store the instantiated layout, where each memory location corresponds to a 1  $\lambda$  by 1  $\lambda$  cell of layout. For a CMOS process, roughly 14 possible layout levels must be remembered for each location. This results in a storage requirement of more than 350 megabits. One useful approach to minimize the memory requirements is to instantiate the design file in overlapping strips. All required circuit information is extracted from each strip before the next strip is instantiated.

The second main step in circuit extraction is the extraction of transistor and connectivity information from the instantiated layout. This is a straightforward, but time-consuming task. The instantiated layout is scanned using a format typical of that used to display television images. The scanning order described here is leftto-right and top-to-bottom, with all integrated circuit levels scanned in parallel. Information on the extent of each level is obtained, and relations between levels that form transistors and contact cuts are derived.

A simple algorithm to determine connectivity at each level can be described as follows. This algorithm requires the program to look at the current cell, the cell to the left, and the cell above. Figure 10.5-1 shows conditions of interest where a "-" indicates no level present and an "m" indicates the presence of a level (e.g., metal). If the current cell does not contain a level, action is not required. This condition is shown in Fig. 10.5-1a by a template (upper part) and a 5  $\lambda$  by 5  $\lambda$  layout sample (lower part). If the current cell contains a level, four possible cases are of interest; these are shown in Figs. 10.5-1b through 10.5-1e.

## Cell templates for each possible condition

|                         | (a) Blank | (b) Upper left 1<br>corner | (c) Top edge      | (d) Left edge | (e) Inside<br>corner |

|-------------------------|-----------|----------------------------|-------------------|---------------|----------------------|

| ,                       | -         | - !                        | -                 | m ¦           | m                    |

|                         |           | - m                        | m m               | - m           | m m                  |

|                         |           | i                          |                   | m m m         | m m m                |

|                         |           |                            |                   | m m m !       | m m m                |

| scan line $\rightarrow$ |           | mmm                        | mmmmmm            | mmm           | mmmmmm               |

|                         |           | mmm;                       | mmmmmm            | ; mmm ;       | mmmmmm               |

|                         |           | m m m ı                    | m $m$ $m$ $m$ $m$ | mmm +         | mmmmmm               |

Layout samples to demonstrate each template

**FIGURE 10.5-1** Connectivity extraction. If the current cell contains a level, say metal, then four cases must be examined. First, if neither the cell to the left nor the cell above contains metal, then an *upper left corner* has been encountered as in Fig. 10.5-1b, and a new node number must be assigned to this location. As a second case, if the cell to the left contains metal but the cell above does not, as in Fig. 10.5-1c, then the extractor is moving along a *top edge*, and the current node is assigned the same node number as the cell to the left. As a third case, if the cell above contains metal but the cell to the left does not, as is shown in Fig. 10.5-1d, a *left edge* has been found, and this node is assigned the same node number as the cell above. As a final case, if both the cell above and the cell to the left contain metal, either an *internal point* or an *inside corner* has been found. If the node numbers for these cells are different, they should be merged. The inside corner template and sample layout section are shown in Fig. 10.5-1e.

The procedure just described produces a list of nodes for each level and a list of nodes that should be merged. Other information is also kept: for example, a count of the number of times each node is encountered (the area), a count of the number of nodes along an edge (the perimeter), and the location of the first occurrence of each node. In addition, relationships between levels such as contact cuts result in a second node merge list. This node merge list must be kept separate from the homogeneous node merge list since the contact cuts represent nodes of different materials that are connected. Electrically they represent the same circuit node, but for capacitance and resistance calculations their individual identity, area, and perimeter must be maintained.

Other interactions between levels must also be considered. Wherever polysilicon and diffusion are coincident, an additional level (transistor) must be created. This artificial level is processed in a manner similar to the other levels to generate individual transistors and maintain their areas for capacitance and drive strength calculations.

# 10.5.2 Circuit Extractor Output

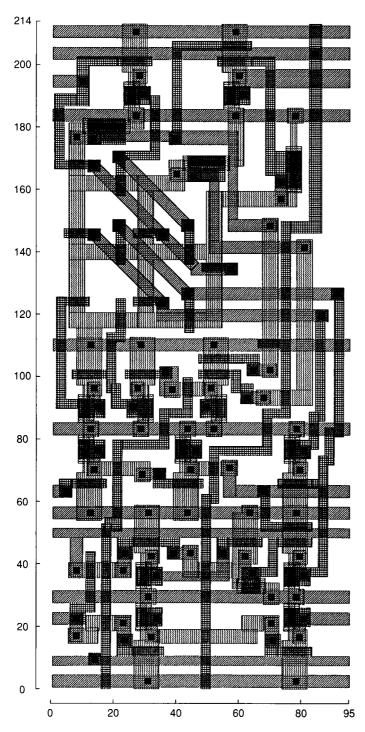

As a minimum, the output from a circuit extraction program should contain a complete list of transistors showing the type of transistor (p-channel, n-channel, depletion, etc.) and the nodes to which the transistor is connected. The circuit of Fig. 10.5-2 was extracted to show typical output. A sample of such output, called a net list, is shown in Fig. 10.5-3.

The extracted output of Fig. 10.5-3 lists an arbitrary transistor number; the drain (DS1), source (DS2), and gate (G) connections; the type of transistor (enhancement or depletion); the shape (ok means rectangular); the length and width of the transistor; and the x and y coordinates of the upper left corner of the transistor. All dimensions are based on the parameter  $\lambda$ . The resolution of Fig. 10.5-2 and its extracted output listings is 0.5  $\lambda$ . With this information, transistor size can be verified, individual transistors can be located, and the  $V_{\rm DD}$  connection for the depletion transistors (the normal case) can be verified. The net list provides sufficient information to allow reconstruction of a transistor-level circuit diagram

FIGURE 10.5-2 Sample layout for circuit extraction.

#### LEXTRACT version 3.337

Date 4-MAR-89 Time 19:54:46

X min = 0.0 X max =95.0  $Y min = 0.0 \ Y max = 214.0$

Macro name is BGMLT Macro number is 99

Final merge node list

| Num | DS1 | DS2 | G  | Type | Shape | Length | Width | X-loc | Y-loc |

|-----|-----|-----|----|------|-------|--------|-------|-------|-------|

| 1   | GND | 42  | 3  | enhN | ok    | 3.0    | 8.0   | 54.0  | 208.5 |

| 2   | GND | 6   | 4  | enhN | ok    | 3.0    | 8.0   | 22.0  | 203.5 |

| 3   | 42  | 7   | 5  | enhN | ok    | 3.0    | 8.0   | 54.0  | 203.5 |

| 4   | 6   | VDD | 6  | depN | ok    | 6.0    | 2.0   | 24.0  | 194.0 |

| 5   | 7   | VDD | 7  | depN | ok    | 6.0    | 2.0   | 56.0  | 194.0 |

| 6   | 3   | VDD | 3  | depN | ok    | 12.0   | 2.0   | 11.0  | 182.0 |

| 7   | VDD | 5   | 5  | depN | ok    | 12.0   | 2.0   | 76.0  | 173.0 |

| 8   | 3   | 51  | 4  | enhN | ok    | 3.0    | 5.0   | 5.0   | 170.0 |

| 9   | 9   | VDD | 9  | depN | ok    | 12.0   | 2.0   | 43.0  | 170.0 |

| 10  | 51  | 9   | 6  | enhN | ok    | 3.0    | 5.0   | 20.0  | 165.0 |

| 11  | 51  | 55  | 11 | enhN | ok    | 3.0    | 5.0   | 5.0   | 148.0 |

| 12  | 9   | 12  | 4  | enhN | ok    | 3.0    | 5.0   | 27.0  | 148.0 |

| 13  | 55  | 12  | 10 | enhN | ok    | 3.0    | 5.0   | 20.0  | 143.0 |

| 14  | 12  | 5   | 6  | enhN | ok    | 3.0    | 5.0   | 42.0  | 143.0 |

| 15  | 5   | 13  | 4  | enhN | ok    | 3.0    | 5.0   | 49.0  | 137.0 |

| 16  | 55  | GND | 14 | enhN | ok    | 3.0    | 5.0   | 5.0   | 126.0 |

| 17  | 12  | 17  | 11 | enhN | ok    | 3.0    | 5.0   | 27.0  | 126.0 |

| 18  | GND | 17  | 15 | enhN | ok    | 3.0    | 5.0   | 20.0  | 121.0 |

| 19  | 17  | 13  | 10 | enhN | ok    | 3.0    | 5.0   | 42.0  | 121.0 |

| 20  | 3   | 18  | 2  | enhN | ok    | 3.0    | 5.0   | 67.0  | 112.5 |

**FIGURE 10.5-3**

Partial net list generated from Fig. 10.5-2 by circuit extractor (VDD and GND labels entered by user).

(not shown) for the integrated circuit. The extracted circuit diagram can be compared with the intended circuit diagram for omissions or errors.

Additional information based on the circuit extraction should be provided. For example, for each integrated circuit layout level, a complete list of nodes with their corresponding areas and perimeters can be provided. If the capacitance per unit area is known for each level, the circuit extraction program can provide an accurate estimate of the capacitance at each node. Figure 10.5-4 provides a partial circuit extractor output for the layout of Fig. 10.5-2 showing the details of the integrated circuit layers that form the nodes of a circuit. For each extracted geometry, this output lists the area, top edge length, left edge length, x and y coordinates of the upper left corner of the geometry, the new merged node number, the old node number assigned to the geometry during extraction, the layout level, and the node name (if any).

The output of Fig. 10.5-4 shows that node 1\* is composed of a diffusion geometry (level 1) with area of 84 square units and perimeter of 37 units, a metal

## LEXTRACT version 3.337

Date 4-MAR-89 Time 19:54:46

X min = 0.0 X max =95.0  $Y min = 0.0 \ Y max = 214.0$

Macro name is BGMLT Macro number is 99

Final merge node list

| Area  | Тор  | Left | X-loc | Y-loc | New | Old | Lev | Name  |

|-------|------|------|-------|-------|-----|-----|-----|-------|

| 84.0  | 8.0  | 10.5 | 22.0  | 214.0 | 1*  | 1   | 1   |       |

| 4.0   | 2.0  | 2.0  | 25.5  | 212.5 |     | 5   | 5   | GND   |

| 380.0 | 95.0 | 4.0  | 0.0   | 213.5 |     | 4   | 4   |       |

| 4.0   | 2.0  | 2.0  | 57.5  | 212.5 |     | 6   | 5   | GND   |

| 44.0  | 8.0  | 5.5  | 54.0  | 214.0 |     | 2   | 1   |       |

| 254.0 | 4.0  | 63.5 | 82.0  | 214.0 | 2*  | 3   | 3   | Phi-2 |

| 4.0   | 2.0  | 2.0  | 83.0  | 205.5 |     | 11  | 5   |       |

| 154.0 | 13.0 | 38.0 | 73.0  | 150.5 |     | 87  | 3   |       |

| 380.0 | 95.0 | 4.0  | 0.0   | 206.5 |     | 9   | 4   |       |

| 90.0  | 10.5 | 22.5 | 65.5  | 112.5 |     | 135 | 3   |       |

| 54.0  | 9.0  | 12.0 | 67.0  | 90.0  |     | 193 | 3   |       |

| 97.5  | 20.0 | 15.5 | 50.0  | 78.0  |     | 222 | 3   |       |

| 195.0 | 5.5  | 62.5 | 47.5  | 62.5  |     | 260 | 3   |       |

| 27.0  | 5.0  | 6.0  | 24.0  | 188.0 | 8*  | 33  | 1   |       |

| 4.0   | 2.0  | 2.0  | 25.5  | 185.5 |     | 38  | 5   | VDD   |

| 12.0  | 6.0  | 2.0  | 23.0  | 182.0 |     | 46  | 1   |       |

| 380.0 | 95.0 | 4.0  | 0.0   | 186.5 |     | 37  | 4   |       |

| 4.0   | 2.0  | 2.0  | 57.5  | 185.5 |     | 39  | 5   | VDD   |

| 87.0  | 5.0  | 18.0 | 56.0  | 188.0 |     | 34  | 1   |       |

| 12.0  | 6.0  | 2.0  | 55.0  | 170.0 |     | 68  | 1   |       |

| 4.0   | 2.0  | 2.0  | 76.5  | 185.5 |     | 40  | 5   |       |

| 43.0  | 5.0  | 14.0 | 75.0  | 187.0 |     | 36  | 1   |       |

| 193.0 | 15.0 | 20.5 | 5.0   | 123.0 | 16* | 122 | 1   |       |

| 4.0   | 2.0  | 2.0  | 11.0  | 111.5 |     | 137 | 5   | GND   |

| 380.0 | 95.0 | 4.0  | 0.0   | 112.5 |     | 134 | 4   |       |

| 4.0   | 2.0  | 2.0  | 27.0  | 111.5 |     | 139 | 5   | GND   |

| 84.0  | 8.0  | 10.5 | 24.5  | 113.0 |     | 132 | 1   |       |

| 335.0 | 95.0 | 15.5 | 0.0   | 51.5  | 30* | 273 | 4   |       |

| 4.0   | 2.0  | 2.0  | 6.5   | 39.0  |     | 308 | 5   | B-in  |

| 27.5  | 5.5  | 5.0  | 5.0   | 40.5  |     | 299 | 1   |       |

## **FIGURE 10.5-4**

Partial layer detail generated by circuit extractor for Fig. 10.5-2.

geometry (level 4) with area of 380 square units, another diffusion geometry (level 1) of 44 square units area and 27 units perimeter, and two contacts (level 5) with area 4 square units each. The x and y coordinates of the upper left corner of each geometry are given, allowing location of the geometry on a display or plot. With the area and perimeter sizes determined, calculation of interconnection capacitances is relatively easy using the values from Table 10.5-1. Example 10.5-1 demonstrates this calculation.

| TABLE 1        | 0.5-1       |        |       |       |     |

|----------------|-------------|--------|-------|-------|-----|

| <b>Typical</b> | capacitance | values | (from | Table | 2B) |

| Layer                | Capacitance              |

|----------------------|--------------------------|

| Metal                | $0.025 \text{ fF/}\mu^2$ |

| Polysilicon          | $0.045 \text{ fF/}\mu^2$ |

| Gate                 | $0.7 \text{ fF/}\mu^2$   |

| Diffusion (bottom)   | $0.33 \text{ fF}/\mu^2$  |

| Diffusion (sidewall) | $0.9 \text{ fF/}\mu$     |

Example 10.5-1 Calculation of nodal interconnect capacitance. For a typical MOS process, parasitic capacitance values to ground are given in Table 10.5-1. Determine the total capacitance for node  $1^*$  of the circuit extraction output given in Fig. 10.5-4. The units of extracted dimensions are  $\mu$ .

**Solution:** The total capacitance to ground at node 1\* is the sum of the capacitance of the layers that compose the node (the contact capacitances are neglected). The capacitance can be calculated as follows.

$$C_{\text{total}} = C_{\text{diff}} + C_{\text{sidewall}} + C_{\text{poly}} + C_{\text{metal}}$$

$$C = (84 + 44)0.33 + (37 + 27)0.9 + (0)0.045 + (380)0.025 \text{ fF}$$

$$C = 42.24 + 57.6 + 9.5 \text{ fF}$$

$$C = 109.34 \text{ fF}$$

If the geometrical specification language allows names to be assigned to nodes, the names can be associated with their respective nodes by the circuit extraction program. The ability to name nodes adds to the complexity of the circuit extraction program since the name information must be kept after the geometric layout is instantiated. This adds substantially to the active computer memory required during a circuit extraction.

A node list with associated names is particularly valuable when checking for open circuits and short circuits. For example, if all power and ground nodes are named ( $V_{\rm DD}$  or GND) and an individual node is associated with both the names  $V_{\rm DD}$  and GND, a short circuit between power and ground is indicated. This is *not* desirable! Conversely, if the name GND is associated with two disjoint nodes, an open circuit may be indicated for the GND node. Of course, these same name tests can be applied to signal nodes and names, and this can be automated to report potential problems. Figure 10.5-4 shows circuit extractor output for a circuit with named nodes.

The nodes of Fig. 10.5-4 are named GND, Phi-2, VDD, and B-in. The fact that two separate nodes (1\* and 16\*) are named GND is cause for suspicion. This may indicate a discontinuity in the ground connection or, as in this case, it may be the result of extracting a partial layout. It is very important to provide node names early in a design and carry these names through the layout and simulation steps.

## 10.5.3 Interface to Other Programs

The output from a circuit extraction program can provide valuable input to circuit and logic simulation programs. Without circuit extraction results, circuit and logic simulations are based on manual input of the intended circuit connections and estimated circuit parameters. If certain process characteristics such as layer capacitance and transistor conductance are provided, a computer program can combine the circuit extraction output with process characteristics to create an input file for circuit simulation and logic simulation. Automatic generation of the input files eliminates human error in providing these data and allows accurate specification of capacitance values and transistor sizes.

Many modern integrated circuits are designed with a high-level circuit description provided in the form of a hardware design language (HDL). If this high-level description allows specification of circuit connections, a particularly important check on circuit integrity can be performed as a result of circuit extraction. The top-down circuit description from the HDL can be compared directly with the bottom-up circuit description from the extracted circuit. This check is valuable because it allows comparison between the designer's intent and the actual computer specification used to generate the fabrication masks.

Circuit extraction is a valuable design verification tool. With the aid of an LVS program, the extracted circuit can be compared to the intended circuit. Circuit extractor derived capacitances and resistances are extremely valuable for accurate circuit simulation. The use of named nodes in the geometrical specification file and subsequent extraction of these nodes allows open, short, and circuit continuity tests.

# 10.6 DIGITAL CIRCUIT SIMULATION

Accurate circuit simulation is essential for the design of analog circuits such as filters, comparators, and operational amplifiers. The need for circuit simulation extends to the design of semiconductor memory chips even though their data are stored in binary or digital form. For example, extremely sensitive sense amplifiers are required within DRAM circuits to respond to the small change in voltage caused by selecting a storage cell. SRAM circuits often use differential sensing circuits to increase the speed of the data access operation. Both of these memory types require accurate circuit simulation for proper design. Circuits whose external operation is totally digital may require accurate circuit simulation to model critical signal-delay paths. Circuit simulations of high accuracy are almost universally performed with a version of the SPICE circuit simulator described in Chapter 4.

Because of the large number of transistors in digital circuits such as microprocessors, peripheral controllers, and digital signal processors, it is not computationally feasible to perform a circuit simulation for the entire circuit. Since the execution time of circuit simulation programs increases at a rate that is only slightly less than the square of the number of nodes under consideration, verification of the operation of large circuits must be accomplished by other means. Many times a simulation at the logic or switch level (described in the next section) can

provide sufficient verification of a digital circuit's functionality. Sometimes even logic simulation programs are too slow to model an entire processor's behavior. Special-purpose hardware simulators are required in these cases. <sup>14</sup>

An intermediate class of circuit simulators is being investigated to provide accurate circuit simulation without the computational penalty of a full circuit simulator. <sup>15,16</sup> These new simulators usually depend on one of two characteristic features of digital circuits. First, most digital circuits are loosely coupled. This means that disjoint parts of the circuit may be relatively independent of one another. There are methods that take advantage of this structure by partitioning the network to simplify the equations that must be solved during a simulation. Second, only a small part, perhaps 25%, of a digital circuit is active during each clock cycle. If a circuit simulator can take advantage of those quiescent portions of the circuit, then only a small part of the circuit will result in simulation calculations at any given time. In either of these two cases, accurate digital circuit simulation can proceed at a relatively rapid rate compared to standard circuit simulation. Nonetheless, digital circuits of any size are rarely simulated in their entirety with circuit-level simulators. Rather, switch-level or logic-level simulators are preferred. Such simulators are described in the next section.

## 10.7 LOGIC AND SWITCH SIMULATION

Digital integrated circuits are designed to operate with binary representations for data. The basic presumption is that only two logic states are important for each signal line. Thus, knowledge of a precise voltage versus time characteristic for each node in the circuit is not necessary to design or analyze digital circuits. For many purposes, this simplifies both the circuits and their analysis compared to analog circuits. Nevertheless, computer simulation and verification of a circuit's functionality are necessary. Even though a digital circuit is designed based on logic gates, the logic gates are fabricated from the basic transistors and conductors allowed by the integrated circuit process. Therefore, it is often the case that the electrical operation of a simple logic circuit must be characterized by using a circuit simulator such as SPICE.

Though circuit simulation of digital circuits is frequently used, such circuit simulation has several drawbacks. As described in the previous section, the large number of logic gates in most digital integrated circuits precludes circuit simulation of the entire system because of the extended computer time required. Also, standard circuit simulators provide more detail about circuit voltages than is required to analyze a logic circuit. In an effort to reduce computer simulation time and to provide appropriate data to characterize the operation of digital circuits, logic simulators were developed.

# 10.7.1 Logic-level Simulation

Logic simulators allow specification of the operation of a circuit block in terms of its behavior. For example, a simple logic gate is described by its behavior, such as AND, OR, or NOT. More complex digital blocks such as full adders

and multiplexers are each described by their corresponding behavior rather than their circuit structure. The circuit inputs are specified as binary values that change at discrete time intervals. Logic simulator outputs are provided as binary values as well. Pure logic simulation does not model time delays through logic blocks. Only the logical behavior of the simulated system is considered, although the concept of sequence wherein one action precedes another is important. Timed logic simulation considers the delays of logic gates and blocks in determining when outputs will change. Because a logic simulator models the circuit in terms of an abstracted (less detailed) representation, larger circuits can be simulated in a much shorter length of time than with circuit simulation. Consider the following example.

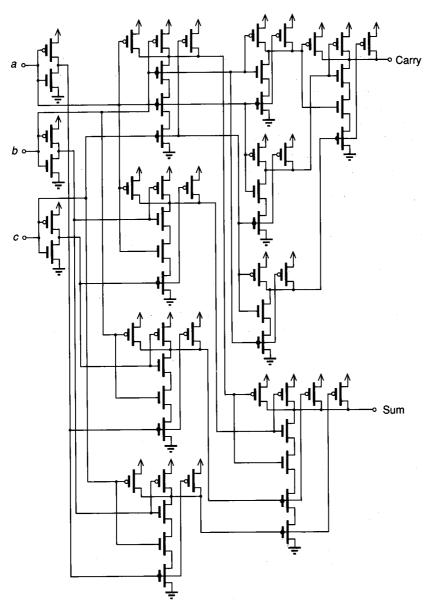

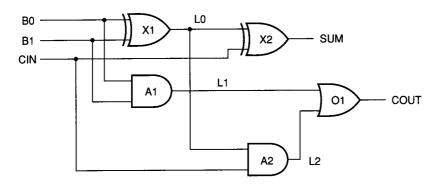

Example 10.7-1 Comparison of circuit and logic simulation. In terms of the number of circuit elements, nodes, and calculations, compare circuit simulation and logic simulation requirements for a full adder built from a classical CMOS circuit and from CMOS gates.

#### Solution

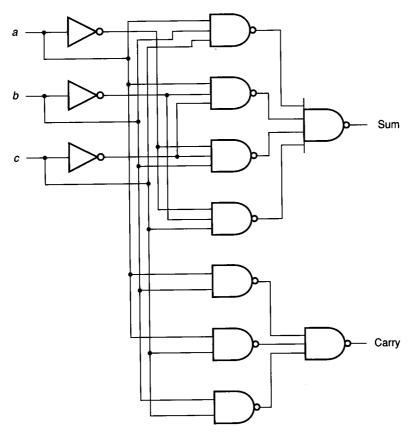

Circuit simulation. The two-level logic circuit for a classical CMOS full adder requires 56 transistors and 33 nodes. This circuit is shown in Fig. 10.7-1. In addition, continuous input waveforms that generate the eight possible logic input conditions of three inputs must be provided. Each of these conditions must be stable for a length of time sufficient to allow the sum and carry outputs to stabilize. This requires about 100 to 200 time steps for each input condition. As a rough estimate, a minimum of 800 to 1600 time-step calculations would be required to characterize the full-adder operation.

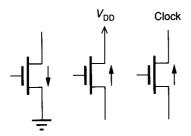

Logic simulation. A classical two-level logic circuit for a full adder requires three inverters, three 2-input NAND gates, five 3-input NAND gates, and a 4input NAND gate, for a total of 12 logic gates and 15 nodes. The logic gate implementation is given in Fig. 10.7-2. Eight possible input combinations exist for the full adder. Each of these combinations generates a digital value for the sum and carry outputs. Correctness of the sum and carry outputs is easily verified by these eight calculations.