# CHAPTER

4

# CIRCUIT SIMULATION

#### 4.0 INTRODUCTION

Computer simulation of a circuit entails using a computer to predict, or simulate, the performance of a circuit or system. The circuit which is simulated may include anywhere from a few components to several hundred thousand. Many different types of computer programs are used for simulations of integrated circuits, depending on the type of analysis required and the size of circuit involved.

The major emphasis in this chapter is on the use of the SPICE simulation program for circuit simulation, and, in particular, on a discussion of the active device models used in SPICE and the interrelationship between these models and the device models discussed in Chapter 3. The simulation program SPICE was selected because of its long-term acceptance and use, as well as its widespread availability to both industrial and academic groups. The reader should have access to and be familiar with the SPICE User's Guide<sup>1</sup> and the basic use of SPICE.

In the design of state-of-the-art integrated circuits; circuit simulations comprise only a small portion of the overall use of the computer. The discussion of a circuit simulation program is included in this chapter because of the challenging nature of circuit simulation. Many students and even practicing engineers experience more problems with circuit simulation than with most of the other sophisticated CAD tools used for VLSI design. These problems largely result from unfamiliarity with the capabilities, limitations, and uses of the simulators.

### 4.1 CIRCUIT SIMULATION USING SPICE

The circuit simulation program called SPICE is the result of a continuing effort, which has spanned nearly 20 years, by a large group of individuals at the University of California at Berkeley. It was initially written in FORTRAN; later

versions in that language are nearly 18,000 lines long. A C-Language version of SPICE was practically introduced in 1987, and now both the FORTRAN and C versions are widely used. SPICE has been adapted to a large number of different hardware configurations and is used in both industry and academia. Although there are several competing programs, some of which may offer advantages in some respects, none are as universally accepted as SPICE.

SPICE utilizes a modified nodal analysis approach. It can be used for nonlinear-dc, nonlinear-transient, and linear-ac analysis problems. It also includes modules for more specialized analysis such as noise analysis, temperature analysis, etc. The inputs can be constant or time varying. For the nonlinear-dc and nonlinear-transient analyses, the program includes the nonlinear effects of all devices specified by the user. For the ac analysis, the dc operating point is internally determined. From the dc operating point, the small signal equivalent circuit of each device is obtained. The resulting linear network is analyzed using the appropriate matrix manipulations. The small signal analysis includes no nonlinear effects of the devices.

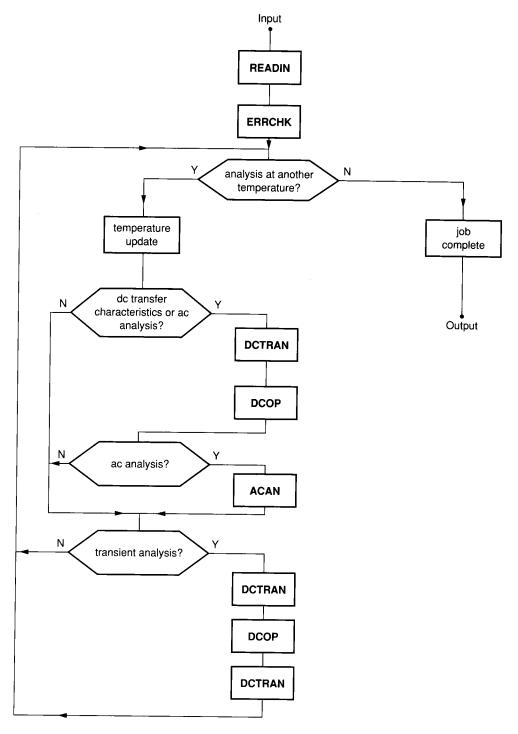

A block diagram showing the fundamental operation of SPICE appears in Fig. 4.1-1. The subroutine READIN reads the SPICE input file. ERRCHK verifies that the input syntax is correct. Temperature effects are handled in SPICE by repeating the entire analysis for each temperature. The subroutines DCTRAN, DCOP and ACAN perform the bulk of the manipulations. DCTRAN and DCOP are used for dc transfer characteristics, dc operating point calculations, and transient analysis. ACAN performs the small signal ac analysis.

Documentation about the program SPICE is required for utilizing the program. At a minimum, the IC designer needs the following two documents available from Berkeley to effectively use SPICE for MOS IC design.

- 1. "SPICE User's Guide"1

- 2. "The Simulation of MOS Integrated Circuits Using SPICE"2

These publications, along with other relevant documentation<sup>3-12,22,23</sup> are listed in the references. The SPICE source code6 contains good comments and serves as the ultimate reference document on the program.

One of the strong points of SPICE is its inclusion of respectable models for the basic active devices, specifically, the diode, BJT, JFET, and MOSFET. The user can create generic models for the active devices that correspond to, and are consistent with, the process parameters and design rules of the process used for a specific design. This model library may actually contain numerous generic device models for a given process, each of which contains as little or as much information as needed for the desired emphasis in the simulation. The designer can then use geometric parameters and specific model name references to specify the complete model for each active device in the circuit being analyzed.

To run SPICE1, the user must first create a file, sometimes referred to as a SPICE deck, which contains a complete description of the circuit (including device models) along with a description of the excitation and the type of analysis desired. This file is accessed when the SPICE program runs.

FIGURE 4.1-1 Simplified SPICE functional flowchart (boldface mnemonics indicate names of major subroutines).

The designer must be familiar with the device models used in any computer simulation. In the following sections the device models of the active devices used in SPICE are discussed. These models are related to those used for hand calculations that were introduced in Chapter 3. Each section is self-contained.

#### 4.2 MOSFET MODEL

SPICE Version 2G has three different MOSFET models, designated as Level 1, Level 2, and Level 3. Version 3 of SPICE also contains a fourth MOSFET model, the BSIM model<sup>7-12</sup>. The BSIM model is a process-oriented model which places a major emphasis on short channel devices. The discussion here will be restricted to the Level 1, Level 2, and Level 3 models. The Level 1 model is basically the same as introduced in Chapter 3 and is termed the Shichman–Hodges model; it closely follows the work of Sah<sup>13</sup>. The Level 1 model is the simplest model and is useful for verifying that no errors occurred in the hand calculations. In some applications the Level 1 model may be adequate for computer simulations.

The Level 2 model differs from the Level 1 model both in its method of calculating the effective channel length ( $\lambda$  effects) and the transition between the saturation and ohmic regions. A time-consuming polynomial rooting routine is required for the Level 2 model to determine the transition point between the linear and saturation regions. The Level 2 model offers improvements in performance which are particularly significant for short channel devices.

The Level 3 model is termed a semi-empirical model. Several empirical parameters (parameters not obviously related to or motivated by the device physics of the MOSFET) are introduced in the Level 3 model. These parameters may offer improvements in fit of the model. The Level 3 model also offers a reduction in time required to calculate the transition point between the linear and saturation regions of operation.

The Level 1, Level 2, and Level 3 device models can be found respectively in subroutines MOSEQ1, MOSEQ2, and MOSEQ3 of the SPICE source code. Subroutine MODCHK is used for some of the hierarchical parameter definitions. The terminal voltages of the MOSFET are passed to these subroutines, and the nodal currents are returned along with the small signal model parameters at the operating point. In each interval of time in a transient analysis, nodal currents are comprised of two parts. The first is the dc current obtainable from the large signal device model. The second is the charge current associated with the parasitic capacitances in the devices. This latter current plays a major role in high-frequency transient analyses.

Temperature effects can also be modeled in SPICE. The functional form of the temperature-dependent device parameters will be discussed later.

Individual MOSFETS are modeled by a two-step process in SPICE. The device element line (card) in the SPICE deck contains information about the nodal location of the device in the circuit as well as geometrical information about the device and optional initial condition variables. In the device element line, reference is made to a specific device *model*. The .MODEL line (card) in the SPICE deck contains generic information about the electrical characteristics

of devices formed in a process based upon the characterizing process parameters. Each device has a separate device element line. Typically, many devices will reference a single .MODEL line.

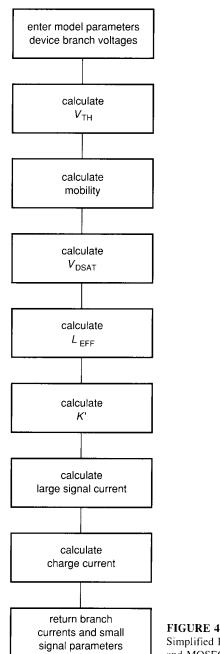

A simplified flowchart of MOSEQ1, MOSEQ2 and MOSEQ3 is shown in Figure 4.2-1. The large signal currents in Quadrant 1 of the  $I_{\rm D}-V_{\rm DS}$  plane are calculated from the expression:

$$I_{\rm G} = I_{\rm B} = 0 \tag{4.2-1}$$

$$I_{\rm D} = \begin{cases} I_{\rm CUTOFF} & V_{\rm GS} < V_{\rm TH} \\ I_{\rm OHMIC} & V_{\rm GS} > V_{\rm TH} \\ I_{\rm SAT} & V_{\rm GS} > V_{\rm TH} \\ V_{\rm DS} > V_{\rm DSAT} \end{cases} \tag{4.2-2}$$

where it is assumed that the drain and source are designated so that  $V_{\rm DS} \geq 0$ . The parameter  $V_{\rm TH}$  denotes the threshold voltage which was denoted by  $V_{\rm T}$  in Chapter 3.  $V_{\rm DSAT}$  is a parameter that characterizes the transition between the ohmic and saturation regions. Operation in Quadrant 3 of the  $I_{\rm D}-V_{\rm DS}$  plane is characterized by the same equations, where the drain and source designations are internally made so that  $V_{\rm DS} \geq 0$ .

The small signal parameters are calculated from the derivatives of  $I_{\rm D}$  with respect to  $V_{\rm GS}$ ,  $V_{\rm DS}$ , and  $V_{\rm BS}$  as explained in Sec. 3.1. In what follows, the expressions used for  $I_{\rm D}$  for the Level 1 and Level 2 models are given along with a description of each of the parameters that appear in the model; the default values used in SPICE are given if the parameter is not specified. The parameters are summarized in Appendix 4A.

Some parameters in the model may be specified in more than one way. For example, the transconductance parameter K', introduced in Sec. 3.1, may be entered directly or calculated from the expression  $K' = \mu_0 C_{\rm ox}$ . A hierarchical convention has been adopted in SPICE to avoid ambiguity. If a parameter is specified, that value will be used. If a parameter is not specified but can be calculated from other parameters that are specified (or have a nonzero default value), the calculated value will be used. If a parameter is not specified and at least one of the other parameters which can be used to calculate it is not specified and defaults to zero, the default value of the original parameter is adopted. A summary of the Level 1 and Level 2 large signal models follows. The parameters used in these models are defined in the Appendices of this chapter.

#### 4.2.1 Level 1 Large Signal Model

$$I_{\text{CUTOFF}} = 0 \tag{4.2-5}$$

$$I_{\text{OHMIC}} = K' \frac{W}{L_{\text{eff}}} ([V_{\text{GS}} - V_{\text{TH}}] - \frac{V_{\text{DS}}}{2}) V_{\text{DS}}$$

(4.2-6)

$$I_{\text{SAT}} = \frac{K'}{2} \frac{W}{L_{\text{eff}}} (V_{\text{GS}} - V_{\text{TH}})^2$$

(4.2-7)

**FIGURE 4.2-1** Simplified Flowchart of SPICE Subroutines MOSEQ1, MOSEQ2, and MOSEQ3.

where  $V_{DSAT}$  is given by

$$V_{\rm DSAT} = V_{\rm GS} - V_{\rm TH} \tag{4.2-8}$$

and the regions of operation are as defined in Eqs. 4.2-1 - 4.2-4.

The parameters  $V_{\rm TH}$  and  $L_{\rm eff}$  represent the threshold voltage and effective length of the device, respectively, and are given by

$$V_{\rm TH} = V_{\rm T0} + \gamma \left[ \sqrt{\phi - V_{\rm BS}} - \sqrt{\phi} \right]$$

(4.2-9)

and

$$L_{\rm eff} = \frac{L_{\rm adj}}{1 + \lambda V_{\rm DS}} \tag{4.2-10}$$

where  $V_{T0}$  is the zero bias threshold voltage,  $\gamma$  is the bulk threshold parameter,  $\phi$  is the surface potential, and  $\lambda$  is the channel length modulation parameter.  $\lambda$  is a SPICE input parameter.  $V_{T0}$ ,  $\gamma$ , and  $\phi$  can either be entered directly or be internally calculated, as discussed later. The parameter K', if not entered, can be calculated from the expression

$$K' = \mu_0 C_{\text{ox}} {4.2-11}$$

where  $\mu_0$  is the nominal channel mobility (if  $\mu_0$  is not entered, the default value will be used) and  $C_{ox}$  is the gate oxide capacitance density which can be calculated from the gate oxide thickness,  $T_{ox}$ , by the expression

$$C_{\rm ox} = \epsilon_{\rm ox}/T_{\rm ox} \tag{4.2-12}$$

where  $\epsilon_{\rm ox}$  is the dielectric constant of  ${\rm SiO}_2$ . The parameter  $L_{\rm adj}$  represents the adjusted length which is the drawn length reduced by the lateral diffusion on the drain and source, LD.

$$L_{\text{adj}} = L - 2 \times \text{LD} \tag{4.2-13}$$

The parameters in  $V_{\rm TH}$ , if not input, are calculated from

$$\gamma = \frac{\sqrt{2q\,\epsilon_{\rm si}N_{\rm SUB}}}{C_{\rm ox}}\tag{4.2-14}$$

$$\phi = \frac{2kT}{q} \ln \left( \frac{N_{\text{SUB}}}{n_{\text{i}}} \right) \tag{4.2-15}$$

and

$$V_{\rm T0} = V_{\rm FB} + \gamma \sqrt{\phi} + \phi \tag{4.2-16}$$

where  $\epsilon_{\rm si}$  is the dielectric constant of silicon,  $N_{\rm SUB}$  is the substrate doping, q is the charge of an electron, and  $n_{\rm i}$  is the intrinsic carrier concentration of silicon.  $N_{\rm SUB}$  is a SPICE input parameter and  $n_{\rm i}$  and  $\epsilon_{\rm si}$  are physical constants defined in Appendix 4A. The flatband voltage,  $V_{\rm FB}$ , is given by

$$V_{\rm FB} = \phi_{\rm ms} - \frac{qN_{\rm ss}}{C_{\rm ox}} \tag{4.2-17}$$

where the input parameter,  $N_{\rm ss}$ , is the effective surface state density and  $\phi_{\rm ms}$  is the semiconductor work function difference.  $\phi_{\rm ms}$  is calculated internally from

$$\phi_{\rm ms} = W_{\rm FN} - \frac{\phi}{2} \tag{4.2-18}$$

where the parameter  $W_{\rm FN}$  is an internal function of physical constants characteristic of the materials involved, TPG (which specifies the types of materials used to construct the device), and temperature.

#### 4.2.2 Level 2 Large Signal Model†

$$I_{\text{CUTOFF}} = \begin{cases} 0 & \text{NFS} = 0\\ I_{\text{weak inversion}} & \text{NFS} \neq 0 \end{cases}$$

(4.2-19)

$$I_{\text{OHMIC}} = \frac{K_2'W}{L_{\text{eff}}} \left[ \left( V_{\text{GS}} - V_{\text{TH}}^{\circ} - \eta \frac{V_{\text{DS}}}{2} \right) V_{\text{DS}} \right] + I_{\text{BSO}}$$

(4.2-20)

$$I_{\text{SAT}} = \frac{K_2'W}{2L_{\text{eff}}} \left[ (V_{\text{GS}} - V_{\text{TH}}^*)^2 (2 - \eta) \right] + I_{\text{BSS}}$$

(4.2-21)

where the cutoff transition region is determined by

$$V_{\text{TH}} = V_{\text{T0}} + \gamma \left[ \sqrt{\phi - V_{\text{BS}}} - \sqrt{\phi} \right] - \gamma \alpha \sqrt{\phi - V_{\text{BS}}} + (\phi - V_{\text{BS}}) \frac{\pi}{4} \frac{\epsilon_{\text{Si}}}{C_{\text{Ox}} \hat{L}_{\text{adj}}} \text{(DELTA)}$$

(4.2-22)

The parameter  $L_{\rm adj}$  is defined by (4.2-13). The parameters DELTA and  $\alpha$  will be discussed later.

The parameter  $V_{\rm MAX}$  is used to characterize the saturation/ohmic transition region as specified in (4.2-3) and (4.2-4); it denotes the maximum drift velocity of carriers in the channel. If the parameter  $V_{\rm MAX}$  is not input, the saturation/ohmic transition region is determined by

$$V_{\text{DSAT}} = \frac{(V_{\text{GS}} - V_{\text{TH}}^*)}{\eta} + \frac{1}{2} \left[ \frac{\gamma_s}{\eta} \right]^2 \cdot \left[ 1 - \left[ 1 + 4 \left( \frac{\gamma}{\eta} (1 - \alpha) \right)^{-2} \left( \frac{V_{\text{GS}} - V_{\text{TH}}^*}{\eta} + \phi - V_{\text{BS}} \right) \right]^{\frac{1}{2}} \right]$$

(4.2-23)

If  $V_{\rm MAX}$  is input,  $V_{\rm DSAT}$  is obtained from solution of a complicated fourth-order polynomial.  $V_{\rm MAX}$  essentially reduces the value of  $V_{\rm DSAT}$  and hence the saturation current in a manner more consistent with experimental measurements. If

$<sup>\</sup>dot{\tau}$ See SPICE source code for the SPICE Model of the MOSFET in weak inversion. The accuracy of the weak inversion MOSFET Models has been questioned by some individuals. 14-15

$V_{\rm MAX}$  is input, computational time for calculating  $V_{\rm DSAT}$  does increase. Additional details about  $V_{\rm MAX}$  can be found in the paper by Vladimerescu and Liu.<sup>2</sup>

The parameters  $\eta$ ,  $V_{\text{TH}}^*$ ,  $I_{\text{BSO}}$  and  $I_{\text{BSS}}$  are given by the following equations:

$$\eta = 1 + \frac{\pi}{4} \frac{\epsilon_{\text{si}}}{C_{\text{ox}} L_{\text{adi}}} (\text{DELTA})$$

(4.2-24)

$$V_{\text{TH}}^* = V_{\text{T0}} - \gamma \sqrt{\phi} + (\phi - V_{\text{BS}}) \frac{\pi}{4} \frac{\epsilon_{\text{Si}}}{C_{\text{ox}} L_{\text{adj}}} \text{(DELTA)}$$

(4.2-25)

$$I_{\rm BSO} = -\frac{2}{3} \frac{K_2' W}{L_{\rm eff}} \frac{\gamma_{\rm s}}{\eta} \left[ (\phi + V_{\rm DS} - V_{\rm BS})^{\frac{3}{2}} - (\phi - V_{\rm BS})^{\frac{3}{2}} \right]$$

(4.2-26)

$$I_{BSS} = \frac{K_2'W}{L_{eff}} \left[ \left[ (V_{GS} - V_{TH}^*)(1 - \eta) - \frac{\eta}{2} (V_{DSAT} - (V_{GS} - V_{TH}^*)) \right] \right]$$

$$(V_{\text{DSAT}} - (V_{\text{GS}} - V_{\text{TH}}^*)) - \frac{2}{3} \frac{\gamma_s}{\tilde{\eta}} \left[ (V_{\text{DSAT}} - V_{\text{BS}} + \phi)^{\frac{3}{2}} - (\phi - V_{\text{BS}})^{\frac{3}{2}} \right]$$

$$(4.2-27)$$

The parameter  $K_2'$  is obtained from the expression

$$K_2' = K' \frac{\mu_s}{\mu_0} \tag{4.2-28}$$

where  $\mu_{\rm s}$  is the effective surface mobility. If not input, K' is determined from (4.2-11). The parameter DELTA is a SPICE input parameter and is used to characterize width reduction (see Problem 4.17) where the effective width,  $W_{\rm eff}$ , is given by  $W_{\rm eff}=W$  (2  $-\eta$ ).

The parameters  $V_{\rm T0}$ ,  $L_{\rm adj}$ , and  $\phi$  are determined as for the Level 1 model. The parameter  $\gamma_s$  is given by

$$\gamma_s = \gamma (1 - \alpha) \tag{4.2-29}$$

The parameter  $\alpha$  is given by:

$$\alpha = \frac{1}{2} \frac{XJ}{L_{\text{adj}}} \left[ \sqrt{1 + \frac{2W_S}{XJ}} + \sqrt{1 + \frac{2W_D}{XJ}} - 2 \right]$$

(4.2-30)

where

$$W_{\rm S} = X_{\rm D} \sqrt{\phi - V_{\rm BS}}$$

(4.2-31)

$$W_{\rm D} = X_{\rm D} \sqrt{\phi - V_{\rm BS} + V_{\rm DS}}$$

(4.2-32)

and where XJ is a SPICE input parameter representing the metallurgical junction depth.

The parameter  $L_{\text{eff}}$  is defined by the expression

$$L_{\text{eff}} = L_{\text{adi}}(1 - \lambda V_{\text{DS}}) \tag{4.2-33}$$

If not specified as an input parameter,  $\lambda$  is calculated from the expression

$$\lambda = \frac{X_{\rm D}}{L_{\rm adj} V_{\rm DS}} \left[ \sqrt{\left| \frac{X_{\rm D} V_{\rm MAX}}{2 \mu_{\rm s}} \right|^2 + (V_{\rm DS} - V_{\rm DSAT})} - \frac{X_{\rm D} V_{\rm MAX}}{2 \mu_{\rm s}} \right] (4.2-34)$$

The parameter  $X_{\rm D}$  is given by the expression

$$X_{\rm D} = \sqrt{\frac{2\epsilon_{\rm si}}{q N_{\rm SUB}}} \qquad (4.2-35)$$

The effective surface mobility,  $\mu_{\rm s}$ , is given by

$$\mu_{\rm s} = \begin{cases} \mu_{\rm o} \left[ \frac{{\rm UCRIT} \cdot \epsilon_{\rm si}}{C_{\rm ox}(V_{\rm GS} - V_{\rm TH})} \right]^{\rm UEXP} & \text{for Level 2} \end{cases}$$

$$\mu_{\rm o} \left[ \frac{{\rm UCRIT} \cdot \epsilon_{\rm si}}{C_{\rm ox}(V_{\rm GS} - V_{\rm TH} - {\rm UTRA} \cdot V_{\rm DS})} \right]^{\rm UEXP} & \text{for Level 3}$$

The parameters UCRIT, UTRA and UEXP are SPICE input parameters used to characterize mobility degradation.

### 4.2.3 High-Frequency MOSFET Model

The high-frequency MOSFET model is obtained from the dc model by adding the identifiable parasitic capacitances to the dc model previously discussed. Parasitic device capacitors in SPICE are essentially modeled as in Section 3.1.3 of Chapter 3. Those capacitors that are voltage independent are modeled by

$$C = \frac{\epsilon A}{t} \tag{4.2-37}$$

(4.2-36)

where  $\epsilon$  is the dielectric constant (permittivity), A is the area of the intersection of the two plates and t is the dielectric thickness. The voltage independent capacitors are comprised of those that are operation-region dependent and those that are not.

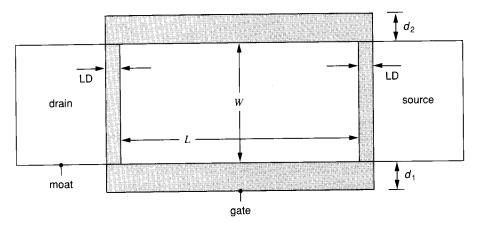

The operation-region independent capacitors are comprised of those overlap capacitors that appear on the periphery of the MOSFET. A top view of these parasitic capacitors appears in Fig. 4.2-2. All are essentially rectangular in shape.

The effective area of the overlap component of the gate-source capacitance is W-LD where W is the channel width and LD is the lateral diffusion of the source. From (4.2-37) the gate-source overlap capacitor,  $C_{\rm GSOL}$ , can be expressed as

$$C_{\text{GSOL}} = \frac{\epsilon \text{LD} \cdot W}{t}$$

$$\lambda = \frac{\chi_{1D}}{L_{\text{cr} \sigma_{1}} V_{0S}} \left[ \frac{v_{0S} - V_{0SA} r}{4} + \left\{ 1 + \left( \frac{V_{0S} - V_{0SA} r}{4} \right) \right\} \right]^{\frac{1}{2}}$$

FIGURE 4.2-2

Top view of operation-region independent, or overlap (shaded) capacitors, in MOS transistors.

or

$$C_{\text{GSOL}} = C_{\text{GSO}}W \tag{4.2-39}$$

where  $C_{\rm GSO} = \epsilon {\rm LD}/t$  represents the overlap capacitance per unit width of the gate.  $C_{\rm GSO}$  serves as an input parameter in SPICE to model the overlap capacitance. Since the dielectric thickness is the same as the gate oxide thickness, this parasitic has an area capacitance density of  $C_{\rm ox}$ . If  $C_{\rm GSO}$  is not entered in SPICE,  $C_{\rm GSOL}$  is calculated from

$$C_{\text{GSOL}} = (C_{\text{ox}})(\text{LD})W \tag{4.2-40}$$

where  $C_{ox}$  is calculated via either the entered or defaulted value of the gate oxide thickness,  $T_{ox}$ . The gate-drain overlap capacitance is modeled in the same manner.

From Fig. 4.2-2, it follows that the gate-bulk overlap capacitance is linearly proportional to L and dependent upon  $d_1$  and  $d_2$ . The dielectric thickness, however, is not constant for this parasitic. The dielectric thickness of the gate-bulk overlap is essentially equal to the gate oxide thickness on the sides adjacent to the channel and equal to the height of the field oxide on the sides farthest from the channel. Although it cannot be modeled by (4.2-37), it is voltage independent. Since it is proportional to L, it is modeled by

$$C_{\rm GBOL} = C_{\rm GBO}L \tag{4.2-41}$$

where  $C_{\rm GBO}$  represents the total gate-bulk capacitance per unit length of the device.  $C_{\rm GBO}$  serves as an input parameter in SPICE to characterize the gate-bulk overlap. Since field oxide thickness is not considered in the MOSFET model, and since  $d_1$  and  $d_2$  are layout dependent, the  $C_{\rm GBO}$  parameter must be entered if the effects of gate-bulk overlap are to be included in the model. It is common practice to assume that  $d_1=d_2=d$  where d is the minimum overlap of the poly over the moat. With this assumption, any bulk-substrate capacitance associated with a larger gate polysilicon region is accounted for by adding an additional parasitic capacitance to the circuit schematic from gate to substrate.

Those capacitors that are voltage dependent are the pn junction capacitors. They occur between bulk and source, bulk and drain, and bulk and channel. They are modeled as in Chapter 3 by

$$C = \frac{C_{j0}A}{(1 - V_{F}/\phi_{B})^{n}} \quad \text{for } V_{F} < FC \cdot \phi_{B}$$

(4.2-42)

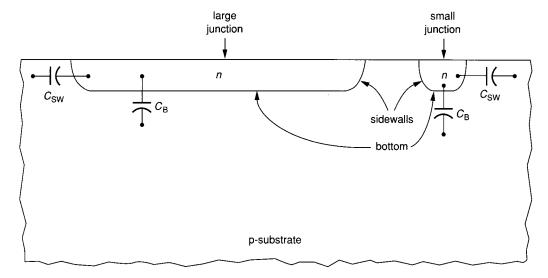

where  $C_{j0}$  is the zero-bias junction capacitance density. FC is called the forward bias capacitance coefficient (FC  $\simeq$  .5) which defines the region where (4.2-42) is valid,  $\phi_B$  is the barrier potential, n is a constant that characterizes the junction type, A is the junction cross-sectional area, and  $V_F$  is the forward bias on the junction (which is usually negative for MOS devices). The modeling of the junction capacitors is complicated somewhat by the actual geometry of the pn junction. A cross section of a pn diffused junction is shown in Fig. 4.2-3. The junction is not planar. The impurity concentrations in the p and n type materials at the bottom of the junctions are different than the concentrations along the sidewalls causing the grading coefficient, n, to vary as a function of position. Although the sidewall capacitances become negligible for large structures, they may actually dominate for small or narrow junctions. The total junction capacitance associated with the "reverse biased" (actually for  $V_F < FC \cdot \phi_B$ ) junction of either the source or drain is thus

$$C_{\text{RB. TOTAL}} = \frac{\text{CJ} \cdot A}{[1 - (V_{\text{F}}/\phi_{\text{B}})]^{\text{MJ}}} + \frac{\text{CJSW} \cdot P}{[1 - (V_{\text{F}}/\phi_{\text{B}})]^{\text{MJSW}}}$$

(4.2-43)

where CJ is the zero-bias bottom capacitance area density, CJSW is the zero-bias sidewall capacitance per unit length of the perimeter, MJ is the bottom junction

FIGURE 4.2-3

Cross section of diffused region showing parasitic junction capacitors.

grading coefficient, FC is the forward bias coefficient (which defines the region where (4.2–43) remains valid), and MJSW is the sidewall grading coefficient. A is the junction bottom area and P is the junction sidewall perimeter. The parameters FC, CJ, CJSW, MJ, MJSW and  $\phi_B$  can be entered in SPICE on the .MODEL card (line). The parameters A and P for the drain and source junctions must be entered on the device card (line). If not input, CJ is calculated internally from  $N_{SUB}$  (if input), under the assumption of a step graded junction, from the expression

$$CJ = \sqrt{\frac{\epsilon_{si}qN_{SUB}}{2\phi_{B}}}$$

(4.2-44)

As an alternative to specifying the drain and source geometries and the junction capacitance density, the user can specify the overriding parameters  $C_{\rm BD}$  and  $C_{\rm BS}$  which represent the total zero-bias bottom capacitance of the bulk-drain and bulk-source junctions, respectively. These are then used in place of CJ  $\cdot$  A in (4.2-43).

Under forward bias  $(V_F > FC \cdot \phi_B)$ , the total junction capacitances are modeled by

$$C_{\text{FB. TOTAL}} = \frac{\text{CJ} \cdot A}{(1 - \text{FC})^{(1+\text{MJ})}} \left[ 1 - \text{FC}(1 + \text{MJ}) + \frac{V_{\text{BS}}}{\phi_{\text{B}}} \text{MJ} \right] + \frac{\text{CJSW} \cdot P}{(1 - \text{FC})^{(1+\text{MJSW})}} \left[ 1 - \text{FC}(1 + \text{MJSW}) + \frac{V_{\text{BS}}}{\phi_{\text{B}}} \text{MJSW} \right]$$

(4.2-46)

This approximation represents a linear continuation of the reverse-bias capacitance which agrees functionally and in the first derivative at the transition point,  $V_F = FC \cdot \phi_B$  (see Problem 3.31 of Chapter 3).

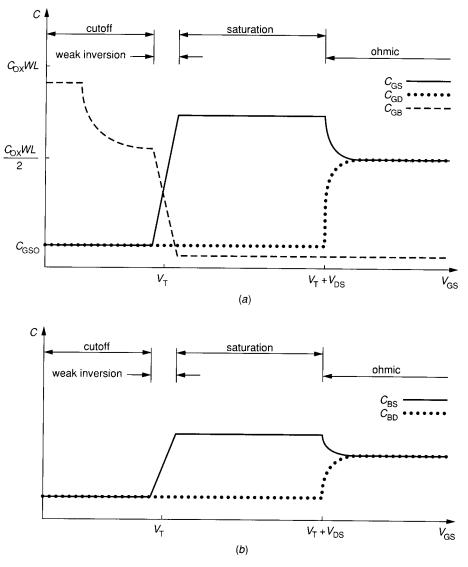

Finally, the operation-region dependent capacitances associated with the channel region itself must be considered. These are essentially distributed capacitances; as such they are more difficult to model. Furthermore, to ease calculations these parasitics are subsequently lumped internally and added to the operation-region independent components of the gate-source, gate-drain, gate-bulk, source-bulk, and drain-bulk capacitors discussed previously. Depending on the operating region, some of the channel capacitances are voltage independent and are modeled by (4.2-37), while others are actually junction capacitances modeled by (4.2-42). The user need not enter any additional parameters; the parasitic channel capacitances are calculated internally from the parameters that characterize the operation-region independent capacitors discussed above. The user is, however, at the mercy of the approximations employed in SPICE to model the channel capacitances. Some industrial groups are not satisfied with the channel capacitance modeling in SPICE and have made modifications which they believe offer some improvements. The exact formulation of the channel capacitances is quite involved and beyond the scope of this text. Details can be found in references 16 and 17, as well as in the SPICE source code itself <sup>6</sup>. The total parasitic capacitances (fixed plus voltage dependent) associated with the lumped approximation used in SPICE are basically as indicated in Fig. 4.2-4.

**FIGURE 4.2-4** Lumped parasitic capacitances for MOSFET as a function of operating point: (a) Associated with gate charge, (b) Associated with bulk charge.

#### 4.2.4 Noise Model of the MOSFET

There are four noise-current generators modeled in the MOSFET device model in SPICE.<sup>18</sup> Two of these represent thermal noise associated with the parasitic series resistances in the drain and source. These are modeled by spectral densities of

$$S_{\rm IRD} = \frac{4kT}{\rm RD} \tag{4.2-47}$$

and

$$S_{\rm IRS} = \frac{4kT}{\rm RS} \tag{4.2-48}$$

respectively, where k is Boltzmann's constant, T is the temperature in  ${}^{\circ}K$ , and RD and RS represent the drain and source parasitic resistances.

The other two noise-current generators are modeled as current sources from drain to source. One represents white shot noise and the other flicker (1/f) noise. These are characterized in the saturation region by spectral densities of I

$$S_{\rm W} = \frac{8kTg_{\rm m}}{3} \tag{4.2-49}$$

and

$$S_f = \frac{(K_{\rm F})I_{\rm DQ}^{A_{\rm F}}}{fC_{\rm ox}WL_{\rm eff}}$$

(4.2-50)

where  $K_{\rm F}$  and  $A_{\rm F}$  are user enterable parameters,  $g_{\rm m}$  is the small signal transconductance gain at the Q-point,  $I_{\rm DQ}$  is the quiescent drain current,  $L_{\rm eff}$  is the effective channel length and f is frequency in Hz. All noise sources are assumed to be uncorrelated.  $S_{\rm W}$  and  $S_f$  add to obtain the overall noise spectral density as discussed in Sec. 3.1.8.

# **4.2.5** Temperature Dependence of the MOSFET

Several of the parameters that characterize the MOSFET are temperature dependent. Specifically, SPICE models the temperature dependence of the parameters K',  $V_{T0}$ ,  $\mu_o$ ,  $\phi$ ,  $\phi_B$ ,  $I_S$ ,

$$K'(T) = \left(\frac{T}{T_1}\right)^{\frac{3}{2}} K'(T_1) \tag{4.2-51}$$

$$\mu_{o}(T) = \left(\frac{T}{T_{1}}\right)^{\frac{3}{2}} \mu_{o}(T_{1})$$

(4.2-52)

$$I_{S}(T) = I_{S}(T_{1})e^{\left[\frac{EG(T)}{V_{t}(T)} - \frac{EG(T_{1})}{V_{t}(T_{1})}\right]}$$

(4.2-53)

$$J_{S}(T) = J_{S}(T_{1})e^{\left[\frac{EG(T)}{V_{i}(T)} - \frac{EG(T_{1})}{V_{i}(T_{1})}\right]}$$

(4.2-54)

$$\phi(T) = \phi(T_1) \cdot (T/T_1) + \phi_{BF}(T) \tag{4.2-55}$$

$$\phi_{\rm B}(T) = \phi_{\rm B}(T_1) \cdot (T/T_1) + \phi_{\rm BF}(T)$$

(4.2-56)

$$C_{\rm BD}(T) = C_{\rm BD}(T_1) \cdot [1 + \theta_{\rm C}(T)]$$

(4.2-57)

$$C_{\rm BS}(T) = C_{\rm BS}(T_1) \cdot [1 + \theta_{\rm C}(T)]$$

(4.2-58)

$$CJ(T) = CJ(T_1) \cdot [1 + \theta_C(T)]$$

(4.2-59)

$$CJSW(T) = CJSW(T_1) \cdot [1 + \theta_C(T)]$$

(4.2-60)

$$\mathsf{K}_{\mathsf{F}}(T) = \mathsf{K}_{\mathsf{F}}(T_1) \cdot [\phi_{\mathsf{B}}(T)/\phi_{\mathsf{B}}(T_1)]$$

(4.2-61)

$$A_{F}(T) = A_{F}(T_{1}) \cdot [\phi_{B}(T)/\phi_{B}(T_{1})] \qquad (4.2-62)$$

where  $T_1$  is any reference temperature in  ${}^{\circ}K$ ,  $V_t = kT/q$ , and the parameters EG,  $\phi_{\rm BF}$ , and  $\theta_{\rm C}$  are defined respectively by the equations

$$EG(T) = [1.16 - (.000702T^2)/(T + 1108)] \text{volts}$$

(4.2-63)

$$\phi_{BF}(T) = -3V_t \ln (T/T_1) - EG(T) + \langle EG(T_1) \rangle \cdot (T/T_1)$$

(4.2-64)

and

$$\theta_{\rm C}(T) = {\rm MJ} \cdot \{0.0004(T - T_1) + 1 - [\phi_{\rm B}(T)/\phi_{\rm B}(T_1)]\} \quad (4.2-65)$$

#### 4.3 DIODE MODEL

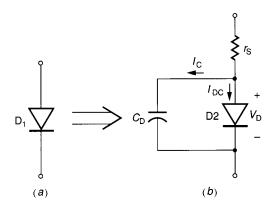

Individual diodes are modeled by a two-step process in SPICE. 1,3,5 The device element line (card) contains information about the nodal location of the device in the circuit as well as geometrical information (relative junction cross-sectional area) and optional initial condition variables useful in transient analyses. In the device element line, reference is made to a specific device model. The .MODEL line (card) contains generic information about the electrical characteristics of devices formed in the process based upon the characterizing process parameters. Each diode has a separate device element line. Typically many devices will reference a single .MODEL line. Most of the diode modeling information can be found in subroutines DIODE and MODCHK in the SPICE source code. As is the case for all device models in SPICE, the small signal parameters which characterize the small signal operation of the diode are calculated from the appropriate derivatives. A philosophy distinctly different from that used for characterizing MOS processes has been adopted for characterizing the process used to fabricate diodes. This difference lies in that the characteristics of a specific

"reference diode" are specified in the .MODEL line. The size of the reference diode is conceptually arbitrary although it is advised to select a reference that is geometrically similar in size and shape to those devices that will be modeled. In the device element line (card) the *relative area* of the reference diode used to characterize the model is specified.

The diode is modeled as the series combination of a resistor,  $r_s$ , and a non-ideal diode, D2, shunted by a parasitic capacitor  $C_D$ , as indicated in Fig. 4.3-1. The resistor,  $r_s$ , accounts for both the series resistance of the diode as well as high-level injection effects. <sup>3,19</sup> It is assumed to be an ideal resistor. In this section, emphasis will be placed upon the model of the series diode, D2, of Fig. 4.3-1b. As indicated in Fig. 4.3-1b, the current of diode D2 is modeled as the sum of a dc (large signal) current, denoted by  $I_{DC}$ , and a current that flows through a parasitic shunting capacitance associated with the pn junction. The large signal current and parasitic capacitance current will be considered separately in the following sections.

### 4.3.1 Large Signal Diode Current

The large signal diode current,  $I_{\rm DC}$  in Fig. 4.3-1b, is modeled by that given in the standard diode equation

$$I_{DC} = I_{S} A_{n} (e^{V_{D}/(nV_{t})} - 1)$$

(4.3-1)

where, as discussed in Chapter 3,

$$V_t = \frac{kT}{q} \tag{4.3-2}$$

$I_{\rm S}$  = saturation current

and

n =emission coefficient.

The parameter  $A_n$  represents the *normalized* cross-sectional area of the junction. It is a dimensionless parameter that is entered on the device element line; it represents the ratio of the cross-sectional area of the device on the device element

FIGURE 4.3-1

Diode model in SPICE: (a) Physical twoterminal device, (b) Equivalent circuit. line to the reference model which is characterized on the .MODEL line. If not specified, SPICE adopts a default value of  $A_n = 1$ . The reverse breakdown voltage, BV, is not of major concern in VLSI design since BV generally exceeds the maximum voltages which will be permitted in VLSI circuits.

### 4.3.2 High-Frequency Diode Model

At high frequencies the parasitic junction capacitance of the diode plays a major role in the performance of the diode. The junction capacitance also affects the transient response. In the following the capacitance is defined by the expression

$$C_{\rm D} = \frac{dQ}{dV_{\rm D}} \tag{4.3-3}$$

$C_{\rm D}$  thus represents the small signal parasitic capacitance. In general,  $C_{\rm D}$  is strongly a function of the instantaneous dc operating point of the diode. Although the model for  $C_{\rm D}$  will be given here, the charge Q is regularly used internally in SPICE for transient analysis.

As discussed in Chapter 3 and Section 4.2, the characterization of a junction capacitor under reverse bias is different from the characterization under forward bias. Under reverse bias (actually for  $V_{\rm D} < {\rm FC} \cdot \phi_{\rm B}$ ), the capacitance is modeled by the equation

$$C_{\rm D} = \frac{C_{\rm jo}A_{\rm n}}{[1 - (V_{\rm D}/\phi_{\rm B})]^m} + \frac{\tau I_{\rm S}A_{\rm n}}{nV_t}e^{V_{\rm D}/(nV_t)}$$

(4.3-4)

where  $I_S$ ,  $A_n$ , n, and  $V_t$  are as previously defined, and the remaining parameters are defined by

$C_{

m jo} = {

m zero-bias}$  junction capacitance  $\phi_{

m B} = {

m capacitance}$  barrier potential

$\phi_{\rm B}$  = capacitance darrier point m = grading coefficient

$\tau = \text{transit time}$

FC = coefficient for forward/reverse bias transition

As was the case for  $I_S$ , it should be noted that  $C_{jo}$  is the zero-bias junction capacitance of the specific area device referred to by the .MODEL line. Although the first term on the right-hand side of (4.3-4) is essentially functionally equivalent to that used in the model of the junction capacitance for the MOSFET, (4.2-42) of Section 4.2, it should be emphasized that in SPICE  $C_{jo}$  represents the capacitance density in (4.2-42), whereas  $C_{jo}$  represents the capacitance of the reference diode itself in (4.3-4).

The second term on the right-hand side of (4.3-4) arises from the charge stored in the junction due to minority carrier injection. The transit time,  $\tau$ , characterizes this capacitance.

For  $V_D > FC \cdot \phi_B$ , SPICE models the capacitance,  $C_D$ , with the equation

$$C_{\rm D} = \frac{C_{\rm jo}A_{\rm n}}{(1 - {\rm FC})^{(1+m)}} \left[ 1 - {\rm FC}[1+m] + \frac{mV_{\rm D}}{\phi_{\rm B}} \right] + \frac{\tau I_{\rm S}A_{\rm n}}{nV_{\rm t}} e^{V_{\rm D}/(nV_{\rm t})} (4.3-5)$$

The first term on the right-hand side of (4.3-5) represents a continuous and differentiable linear extension of the first term on the right-hand side of (4.3-4) across the boundary  $V_D = FC \cdot \phi_B$ . The second terms on the right-hand side, of Eqs. 4.3-4 and 4.3-5 are identical.

#### 4.4 BJT MODEL

The SPICE model of the BJT is based upon a modified Gummel-Poon model. <sup>20,21</sup> Simulations based upon the simpler Gummel-Poon model discussed in Chapter 3 can also be readily made by setting the appropriate Ebers-Moll parameters to zero as will be discussed later in this section. Use of the Ebers-Moll model in the early stages of a simulation may be useful for verifying theoretical hand calculations.

The bipolar junction transistor is modeled by two input lines (cards) in SPICE. The device line (card) is used for indicating the nodal connections of the BJT in a circuit. It is also used to reference a specific model, by name, which contains process information. An optional normalized parameter on the device line,  $A_n$ , is used to indicate the ratio of the area of the emitter to the emitter area of the device of the referenced model. An optional initial condition parameter can also be included on the device line if desired.

The second input line (card) that is used to model the BJT is the .MODEL line. SPICE version 2G.6 provides for user entry of up to 40 parameters on the .MODEL line for characterizing the device. As was the case with the diode, a user-selected reference transistor is used to characterize the bipolar process. The BJT model information is contained primarily in subroutines MODCHK and BJT in the SPICE source code. MODCHK does preprocessing of some of the input parameters (e.g., the reciprocals of some parameters are actually used as variables in the source code rather than the parameters themselves). The model itself basically appears in subroutine BJT.

As is the case for the other semiconductor models in SPICE, the BJT model is characterized by four types of input parameters. These are 1) large signal or dc parameters, 2) charge storage or capacitance parameters, 3) noise parameters, and 4) temperature characterization parameters.

The small signal low-frequency model used in SPICE is obtained from a symbolic differentiation of the large signal current equations evaluated at the dc operation point. As is the case for all small signal analyses in SPICE, the small signal model of the BJT is linear and thus the small signal simulation gives no distortion information. (Distortion information at a specific frequency can be obtained from a much more time consuming transient response with a sinusoidal excitation of fixed frequency and amplitude.) To obtain reliable distortion information, it is crucial that the transient analysis interval is long enough to guarantee essentially steady state operation.

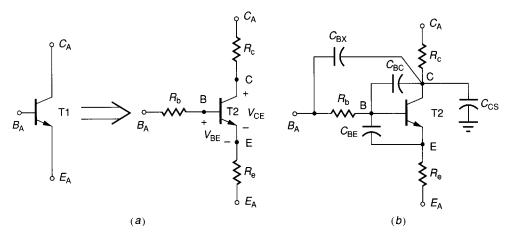

A series resistance is modeled in series with each lead of the BJT as indicated in Fig. 4.4-1. These resistances are input parameters in SPICE. In the model discussion that follows, all formulation is relative to transistor T2 (denoted by nodes C, B, and E) in this figure; specifically,  $V_{\rm BE}$  and  $V_{\rm CE}$  represent the base-emitter and collector-emitter voltages of T2 rather than the actual base-emitter and collector-emitter voltages of the device (denoted by nodes  $C_{\rm A}$ ,  $B_{\rm A}$ , and  $E_{\rm A}$ )

**FIGURE 4.4-1** Modeling of the BJT in SPICE: (a) dc modeling, (b) High-frequency modeling.

which is to be modeled, T1. In the model that follows, junction breakdown voltages will not be discussed in detail since, with the exception of the reverse base-emitter breakdown, voltage levels in bipolar integrated circuits are usually considerably below the breakdown voltages of the BJT.

## 4.4.1 Large Signal BJT Model

The collector current and base current are characterized by the equations

$$\begin{split} I_{\rm C} &= \frac{I_{\rm S}A_{\rm n}}{Q_{\rm B}}(e^{V_{\rm BE}/({\rm NF}\cdot V_{\rm t})}-1) - I_{\rm S}A_{\rm n} \Big| \frac{1}{Q_{\rm B}} + \frac{1}{{\rm BR}} \Big| (e^{V_{\rm BC}/({\rm NR}\cdot V_{\rm t})}-1) \\ &- I_{\rm SC}A_{\rm n} (e^{V_{\rm BC}/({\rm NC}\cdot V_{\rm t})}-1) - (4.4\text{-}1) \\ I_{\rm B} &= \frac{I_{\rm S}A_{\rm n}}{{\rm BF}}(e^{V_{\rm BE}/({\rm NF}\cdot V_{\rm t})}-1) + \frac{I_{\rm S}A_{\rm n}}{{\rm BR}}(e^{V_{\rm BC}/({\rm NR}\cdot V_{\rm t})}-1) + I_{\rm SE}A_{\rm n}(e^{V_{\rm BE}/({\rm NE}\cdot V_{\rm t})}-1) \\ &+ I_{\rm SC}A_{\rm n}(e^{V_{\rm BC}/({\rm NC}\cdot V_{\rm t})}-1) - (4.4\text{-}2) \end{split}$$

where  $V_t = kT/q$

$A_n$  = normalized emitter area ratio

$I_{\rm S}$  = saturation current

$I_{SE} = B-E$  leakage saturation current

$I_{SC}$  = B-C leakage saturation current

NF = forward current emission coefficient

NR = reverse current emission coefficient

NE = B-E leakage current emission coefficient

NC = B-C leakage current emission coefficient

$BF = ideal maximum forward \beta$

$BR = ideal maximum reverse \beta$

and

$$Q_{\rm B} = \left[ \frac{1}{1 - (V_{\rm BC}/V_{\rm AF}) - (V_{\rm BE}/V_{\rm AR})} \right] \cdot$$

$$\left[\frac{1+\sqrt{1+4[(I_{S}/I_{KF})(e^{V_{BE}/(NF\cdot V_{t})}-1)+(I_{S}/I_{KR})(e^{V_{BC}/(NR\cdot V_{t})}-1)]}}{2}\right]$$

(4.4-3)

The parameters in (4.4-3) are defined as

$V_{AF}$  = Forward Early Voltage

$V_{AR}$  = Reverse Early Voltage

$I_{KF}$  = Corner for forward current gain roll-off

$I_{KR}$  = Corner for reverse current gain roll-off

This completes the large signal model of the BJT. A discussion of the characterizing parameters in the BJT model follows. In addition to providing insight into how these parameters impact performance of the BJT, this discussion should provide a mechanism for obtaining SPICE parameters from measured device data.

Although it may appear that all dependence of  $I_{\rm C}$  and  $I_{\rm B}$  on  $V_{\rm BE}$  and  $V_{\rm BC}$  is exponential, it can be seen from (4.4-3) that  $Q_{\rm B}$  is a complicated function of  $V_{\rm BC}$  and  $V_{\rm BE}$ . If  $I_{\rm KF}$  and  $I_{\rm KR}$  are neglected (i.e.,  $I_{\rm KF}=I_{\rm KR}=\infty$ ), then  $Q_{\rm B}$  reduces to

$$Q_{\rm B} = \left(1 - \frac{V_{\rm BC}}{V_{\rm AF}} - \frac{V_{\rm BE}}{V_{\rm AR}}\right)^{-1} \tag{4.4-4}$$

so that the  $\frac{1}{Q_R}$  term in (4.4-1) becomes

$$Q_{\rm B}^{-1} = 1 - \frac{V_{\rm BC}}{V_{\rm AF}} - \frac{V_{\rm BE}}{V_{\rm AR}} = 1 + \frac{V_{\rm CE}}{V_{\rm AF}} - V_{\rm BE} \left( \frac{1}{V_{\rm AF}} + \frac{1}{V_{\rm AR}} \right)$$

(4.4-5)

which is approximately equal to the multiplying factor used to model Early Voltage effects in the extended Ebers-Moll model of Chapter 3. Even if  $I_{\rm KF}$  and  $I_{\rm KR}$  effects are included,  $Q_{\rm B}$  can be approximated by (4.4-4) until  $V_{\rm BE}$  or  $V_{\rm BC}$  becomes quite large, since  $I_{\rm KF}$  is typically about ten orders of magnitude larger than  $I_{\rm S}$ . For large  $V_{\rm BE}$  or  $V_{\rm BC}$ , however,  $I_{\rm C}$  varies essentially linearly with  $e^{V_{\rm BE}/2{\rm NF}\cdot V_{\rm T}}$  or  $e^{V_{\rm BC}/2{\rm NR}\cdot V_{\rm T}}$ .

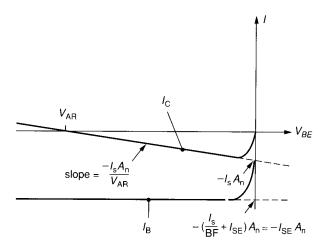

Considerable insight into how the parameters affect device performance can be obtained by plotting  $I_C$  and  $I_B$  versus one device branch voltage,  $V_{\rm BE}$  or  $V_{\rm BC}$ , with the other branch voltage set to zero. For brevity, only the  $V_{\rm BC}=0$  case will be considered here. The analysis for the  $V_{\rm BE}=0$  case is essentially a mirror image of the  $V_{\rm BC}=0$  analysis.

Under the assumption that  $V_{\rm BC}=0,~(4.4\text{-}1),~(4.4\text{-}2)$  and (4.4-3) simplify to

$$I_{\rm C} = \frac{I_{\rm S} A_{\rm n}}{Q_{\rm B}} (e^{V_{\rm BE}/({\rm NF} \cdot V_t)} - 1)$$

(4.4-6)

$$I_{B} = \frac{I_{S}A_{n}}{BF} \left(e^{V_{BE}/(NF \cdot V_{t})} - 1\right) + I_{SE}A_{n}\left(e^{V_{BE}/(NE \cdot V_{t})} - 1\right)$$

$$Q_{B} = \left[\frac{1}{1 - (V_{BE}/V_{AR})}\right] \left[\frac{1 + \sqrt{1 + 4(I_{S}/I_{KF})(e^{V_{BE}/(NF \cdot V_{t})} - 1)}}{2}\right]$$

(4.4-8)

A plot of  $I_{\rm C}$  and  $I_{\rm B}$  versus  $V_{\rm BE}$  for  $V_{\rm BE} < 0$  is shown in Fig. 4.4-2. The parameter  $A_{\rm n}$ , which denotes the relative emitter area, is obtained from geometrical information. The projection of the linear portion of the  $I_{\rm C}$  curve intercepts the I axis at  $-I_{\rm S}A_{\rm n}$ . The slope of the linear portion of the  $I_{\rm C}$  curve can subsequently be used to determine  $V_{\rm AR}$ . The vertical axis intercept of the projection of the linear portion of the  $I_{\rm B}$  curve can be used to determine  $I_{\rm SE}$  since  $I_{\rm SE}$  is typically about four orders of magnitude larger than  $I_{\rm S}/BF$ . Although the  $V_{\rm BE} < 0$  curves can be used to determine  $I_{\rm S}$ ,  $I_{\rm SE}$  and  $V_{\rm AR}$ , they are most useful for the  $V_{\rm AR}$  determination. The parameters  $I_{\rm S}$  and  $I_{\rm SE}$  are typically determined from the  $V_{\rm BE} > 0$  plots.

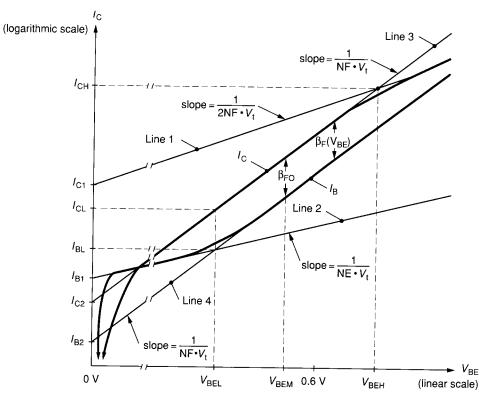

A plot of  $I_{\rm C}$  and  $I_{\rm B}$  versus  $V_{\rm BE}$  for  $V_{\rm BE}>0$  is shown in Fig. 4.4-3 on a graph with a logarithmic scale for the vertical axis. Also shown are four straight lines which essentially represent asymptotic behavior of the BJT over a fairly wide range of  $V_{\rm BE}$  values. The equations of these asymptotic lines are easily derived from (4.4-6)–(4.4-8). Several of the dc parameters that characterize the BJT can be readily determined from the curves shown in Fig. 4.4–3. A sequence of calculations follows for determining some of the dc parameters after  $V_{\rm AR}$  has been determined from Fig. 4.4-2.

First,  $I_S$  and  $I_{SE}$  can be determined from the y-intercepts of Line 3 and Line 2, respectively. With  $I_S$  known, BF can be determined from the y-intercept of Line 4.  $I_{KF}$  can be determined from either the vertical axis intercept of Line 1 or the y-coordinate of the intersection of Lines 1 and 3. NF can be obtained

FIGURE 4.4-2 Plot of collector and base current vs.  $V_{BE}$  for  $V_{BC} = 0$ .  $V_{DE} < 0$ .

$$V_{\text{BEL}} = \frac{V_{\text{t}} \cdot \text{NE} \cdot \text{NF}}{\text{NE} - \text{NF}} \ln \left( \frac{I_{\text{SE}} \cdot \text{BF}}{I_{\text{S}}} \right) \qquad I_{\text{CH}} = I_{\text{KF}} A_{\text{n}} \left( 1 + \frac{0.6 \text{ V}}{V_{\text{AR}}} \right)$$

$$V_{\text{BEH}} = V_{\text{t}} \cdot \text{NF} \cdot \ln \left( \frac{I_{\text{KF}}}{I_{\text{S}}} \right) \qquad I_{\text{C1}} = A_{\text{n}} \sqrt{I_{\text{S}} I_{\text{KF}}}} \left( 1 + \frac{0.6 \text{ V}}{V_{\text{AR}}} \right)$$

$$Line 1: I = \left( 1 + \frac{0.6 \text{ V}}{V_{\text{AR}}} \right) A_{\text{n}} \sqrt{I_{\text{S}} I_{\text{KF}}}} e^{\frac{V_{\text{BE}}}{2\text{NF} \cdot \text{V}_{\text{t}}}} \qquad I_{\text{CL}} = I_{\text{SE}} A_{\text{n}} \left( \frac{I_{\text{SE}} \cdot \text{BF}}{I_{\text{S}}} \right) \frac{\text{NF}}{\text{NE} - \text{NF}}}{I_{\text{S}}}$$

$$Line 2: I = I_{\text{SE}} A_{\text{n}} e^{\frac{V_{\text{BE}}}{\text{NE}} \cdot \text{V}_{\text{t}}} \qquad I_{\text{BL}} = A_{\text{n}} I_{\text{SE}} \frac{\text{NE}}{\text{NE}} - \text{NF}} \left( \frac{I_{\text{S}}}{I_{\text{S}}} \right) \frac{\text{NF}}{\text{NF} - \text{NE}}}{I_{\text{BF}}}$$

$$Line 3: I = \left( 1 + \frac{0.6 \text{ V}}{V_{\text{AR}}} \right) I_{\text{S}} A_{\text{n}} e^{\frac{V_{\text{BE}}}{\text{NF} \cdot \text{V}_{\text{t}}}} \qquad I_{\text{B1}} = I_{\text{SE}} A_{\text{n}}$$

$$Line 4: I = \frac{I_{\text{S}} A_{\text{n}}}{\text{BF}} e^{\frac{V_{\text{BE}}}{\text{NF} \cdot \text{V}_{\text{t}}}} \qquad I_{\text{C2}} = I_{\text{S}} A_{\text{n}} \left( 1 + \frac{0.6 \text{ V}}{V_{\text{AR}}} \right)$$

$$I_{\text{B2}} = \frac{I_{\text{S}} A_{\text{n}}}{\text{BF}}$$

**FIGURE 4.4-3**

Plot of collector current and base current vs.  $V_{\rm BE}$  for  $V_{\rm BC}=0$ ,  $V_{\rm BE}>0$  (logarithmic scale on vertical axis).

from the slope of Lines 1, 3, or 4, while NE can be determined from the slope of Line 2. At this point, it is easy to verify that *all* parameters in the dc model of (4.4-1)-(4.4-3) can be determined from the plots in Fig. 4.4-2 and Fig. 4.4-3 and the corresponding plots for  $V_{\rm BE}=0$ ,  $V_{\rm BC}>0$ .

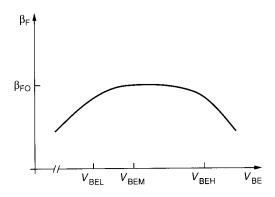

The current gain of the BJT is often of interest. Defining the forward current gain (a similar procedure can be used for the reverse current gain) by the expression

$$\beta_{\rm F} = \frac{I_{\rm C}}{I_{\rm B}} \bigg|_{V_{\rm BC} = 0} \tag{4.4-9}$$

it follows from the curves in Fig. 4.4-3 that  $\beta_F$  is  $V_{BE}$  dependent. For a rather large range of  $V_{BE}$ , however, it is essentially constant and (neglecting  $V_{AR}$  effects) approximately equal to

$$\beta_{\rm F} = BF \simeq \beta_{\rm FO} \tag{4.4-10}$$

where  $\beta_{FO}$  represents the maximum value of  $\beta_{F}$  for  $V_{BEL} < V_{BE} < V_{BEH}$  and where  $V_{BEL}$  and  $V_{BEH}$  are as defined in Fig. 4.4-3.  $V_{BEM}$  denotes value of  $V_{BE}$  where  $\beta_{F}$  is maximum. At lower  $V_{BE}$ ,  $\beta_{F}$  decreases due to changes in the characteristics of  $I_{B}$ ; for higher  $V_{BE}$ ,  $\beta_{F}$  decreases due to changes in the characteristics of  $I_{C}$ . A plot of  $\beta_{F}$  versus  $V_{BE}$  as defined by Eq. 4.4-9 appears in Fig. 4.4-4. It can be seen from Figs. 4.4-3 and 4.4-4 that the parameter  $I_{KF}$  is approximately equal to the value of collector current where high-current roll-off in  $\beta_{F}$  occurs, which explains the name for  $I_{KF}$ , "corner for forward current gain roll-off." The corresponding low-frequency roll-off, which occurs at  $V_{BE} = V_{BEL}$ , is not characterized by a single parameter but is strongly dependent upon the B–E leakage saturation current,  $I_{SE}$ .

This section concludes with a discussion of how the SPICE model parameters can be specified to do simulations based upon the simplified Ebers–Moll model of Chapter 3, characterized by Eqs. 3.3-1 and 3.3-2.

It follows from Eqs. 4.4-1–4.4-3 that if  $I_{SE} = I_{SC} = 0$ ,  $I_{KF} = I_{KR} = \infty$ ,  $V_{AF} = V_{AR} = \infty$  and NF = NR = 1, the model will agree with this Ebers–Moll model. Since these variable assignments are the default values, the user only needs to specify IS, BF, and BR to use the simplified dc Ebers–Moll model.

FIGURE 4.4-4 Forward current gain of BJT vs.  $V_{BF}(V_{BC} = 0)$ .

#### 4.4.2 High-Frequency BJT Model

The high-frequency model of the BJT used in SPICE is obtained by adding three parasitic capacitors to the transistor T2 in Fig. 4.4-1 and one capacitor, CBX, between the base of T1 (node  $B_A$ ) and the collector of T2 (node C). The parasitic capacitors are, in general, voltage dependent. The capacitor values used in SPICE are defined by the derivative

$$C = \frac{dQ}{dV} \tag{4.4-11}$$

where Q is the charge on the capacitor and V is the corresponding port voltage. Seventeen parameters are used to characterize the four parasitic capacitors in SPICE.

The parasitic capacitors are, in general, modeled by the parallel combination (sum) of a depletion region capacitor and a capacitor which occurs due to charge accumulation in the depletion region. The depletion region capacitor is voltage dependent and is modeled by Eqs. 3.2-8 and 3.2-9 of Chapter 3. The capacitor attributed to the charge accumulation is current dependent. Finally, under forward bias the model for the parasitic capacitors has a different parametric form, than under reverse bias. The voltage where transition must be made from the reverse bias parametric capacitance model to the forward bias parametric model is termed the transition voltage. A summary of the parasitic capacitors used in SPICE 2G.6 is shown in Table 4.4-1.

The depletion region reverse-biased junction capacitors are defined by the expressions

$$C_{\text{BEDR}} = A_{\text{n}} C_{\text{JE}} \left( 1 - \frac{V_{\text{BE}}}{\phi_{\text{B}}} \right)^{-M_{\text{JE}}}$$

(4.4-12)

$$C_{\text{BCDR}} = \theta A_{\text{n}} C_{\text{JC}} \left( 1 - \frac{V_{\text{BC}}}{\phi_{\text{C}}} \right)^{-M_{\text{JC}}}$$

(4.4-13)

$$C_{\text{CSDR}} = A_{\text{n}} C_{\text{JS}} \left[ 1 - \frac{V_{\text{CS}}}{\phi_{\text{S}}} \right]^{-M_{\text{JS}}}$$

(4.4-14)

$$C_{\text{XSDR}} = (1 - \theta) A_{\text{n}} C_{\text{JC}} \left[ 1 - \frac{V_{\text{B}^{\circ}\text{C}}}{\phi_{\text{C}}} \right]^{-M_{\text{JC}}}$$

(4.4-15)

where  $M_{\rm JE}, M_{\rm JS}, M_{\rm JC}, C_{\rm JE}, C_{\rm JS}$  and  $C_{\rm JC}$  are input parameters.  $\phi_B, \phi_S, \phi_C$ , and  $\theta$  are also SPICE input parameters, denoted by PB, PS, PC and XCJC, respectively. The parameter  $\theta$  represents the percentage of the B–C capacitance which is to be associated with the internal base node (base of T2 in Fig. 4.4-1).  $V_{\rm B^*C}$  is the voltage from the base of T1 to the collector of T2 in Fig. 4.4-1.

The transition voltages  $V_{\rm BCT}, V_{\rm BCT}, V_{\rm CST}$  and  $V_{\rm XST}$  are FC  $\cdot$   $\phi_{\rm B}$ , FC  $\cdot$   $\phi_{\rm C}$ , 0 V, and FC  $\cdot$   $\phi_{\rm C}$  respectively where FC is a SPICE input parameter used to characterize the transition.

The forward biased depletion junction capacitors  $C_{\rm BEDF}$ ,  $C_{\rm BCDF}$ ,  $C_{\rm CSDF}$ , and  $C_{\rm XSDF}$  are the continuous and differentiable linear extensions of Eqs. 4.4-12–

**TABLE 4.4-1** Parasitic capacitors in BJT model

|                   | Operating region      |                     |                             |                       |                     |  |  |  |

|-------------------|-----------------------|---------------------|-----------------------------|-----------------------|---------------------|--|--|--|

|                   | Rev                   | erse bias           |                             | Forward bias          |                     |  |  |  |

|                   | Depletion<br>junction | Accumulation charge | Transition voltage          | Depletion<br>junction | Accumulation charge |  |  |  |

| $C_{\rm BE}$      | $C_{BEDR}$            | $C_{\mathrm{BEAR}}$ | $V_{\mathrm{BET}}$          | $C_{BEDF}$            | $C_{BEAF}$          |  |  |  |

| $C_{\mathrm{BC}}$ | $C_{BCDR}$            | $C_{BCAR}$          | $V_{ m BCT}$                | $C_{\mathtt{BCDF}}$   | $C_{ m BCAF}$       |  |  |  |

| $C_{\rm CS}$      | $C_{CSDR}$            | $C_{CSAR} = 0$      | $V_{\rm CST} = 0 \text{ V}$ | $C_{CSDF}$            | $C_{\rm CSAF}=0$    |  |  |  |

| $C_{\rm XS}$      | $C_{ m XSDR}$         | $C_{\rm XSAR} = 0$  | $V_{XST}$                   | $C_{	ext{XSDF}}$      | $C_{\rm XSAF}=0$    |  |  |  |

4.4-15, respectively, at the transition voltage. These capacitances are functionally of the form of the corresponding extension used for characterizing the diode capacitance under forward bias as given by (3.2-9).

The accumulated charge capacitors  $C_{CSAR}$ ,  $C_{CSAF}$ ,  $C_{XSAR}$ , and  $C_{XSAF}$  are all zero. The forward and reverse bias accumulation charge capacitors are assumed equal (i.e.,  $C_{\text{BEAR}} = C_{\text{BEDF}}$  and  $C_{\text{BCAR}} = C_{\text{BCDF}}$ ). It remains to characterize  $C_{\text{BEAR}}$ and  $C_{\rm BCAR}$ . The functional form of these capacitors is given in (3.1-29) of Chapter 3. Unfortunately, the transit time is affected by the operating conditions ( $V_{\rm BE}$  and  $V_{\rm BC}$ ) of the BJT. The parameters TF, XTF, VTF, ITF, PTF, and TR are used to characterize the transit times. The expression for the effective transit times is quite unwieldly, so it will not be given here. The interested reader should examine subroutine BJT (especially the expressions for CAPBE and CAPBC) in the SPICE source code for details.6

#### 4.4.3 BJT Noise Model

Five noise sources are used to model the noise characteristics of the BJT. Thermal resistance noise sources are characterized by current sources with a spectral density of

$$S_{NR} = \frac{4kT}{R_x} \qquad \text{for } x \in \{b, e, c\}$$

(4.4-16)

These are modeled in parallel with the three resistors  $R_b$ ,  $R_e$ , and  $R_c$  of Fig. 4.4-1. Parameters in this equation are defined in Appendix 4C. Shot and flicker noise are modeled by two current sources, the first with a spectral density of

$$S_{\rm NB} = 2qI_{\rm CO} \tag{4.4-17}$$

is connected from the base to the emitter of T2 in Fig. 4.4-1. The second current source has a spectral density of

$$S_{\rm NC} = 2qI_{\rm BQ} + \frac{K_{\rm F}I_{\rm BQ}^{\rm AF}}{f}$$

(4.4-18)

and is connected from the collector to the emitter of T2 in the same figure. The parameters q, k, and T have been defined previously and are included in Appendix 4C.  $K_{\rm F}$  and AF are SPICE input parameters and f is frequency in Hz.  $I_{\rm BO}$  and  $I_{\rm CO}$  represent the quiescent values of  $I_{\rm B}$  and  $I_{\rm C}$ , respectively. All noise sources in the BJT are assumed to be uncorrelated.

### 4.4.4 Temperature Dependence of the BJT

Several of the parameters that characterize the BJT are temperature dependent. SPICE models the temperature dependence of the saturation currents  $(I_S, I_{SE}, \text{ and } I_{SC})$ , betas (BF and BR), the junction capacitance parameters  $(C_{JE}, C_{JC}, C_{JS}, \phi_B, \phi_C)$  and  $\phi_S$ , and the noise coefficients  $K_F$  and  $A_F$ . The saturation currents at a temperature T are characterized by the equations

$$I_{S}(T) = I_{S}(T_{1}) \left( \frac{T}{T_{1}} \right)^{XTI} \exp \left[ \left( \frac{T}{T_{1}} - 1 \right) \frac{EG(T) \cdot q}{kT} \right]$$

(4.4-19)

$$I_{SE}(T) = I_{SE}(T_1) \left( \frac{T}{T_1} \right)^{[(XTI/NE)-XTB]} \exp \left[ \left( \frac{T}{T_1} - 1 \right) \left( \frac{EG(T) \cdot q}{NE \cdot kT} \right) \right]$$

(4.4-20)

$$I_{SC}(T) = I_{SC}(T_1) \left(\frac{T}{T_1}\right)^{[(XTI/NC)-XTB]} \exp\left[\left(\frac{T}{T_1} - 1\right) \left(\frac{EG(T) \cdot q}{NC \cdot kT}\right)\right]$$

(4.4-21)

where  $T_1$  is any reference temperature, EG(T) is given in Eq. (4.2-63) and the remaining parameters are SPICE input parameters.

The parameters BF and BR are given by the expressions

$$BF(T) = BF(T_1) \left(\frac{T}{T_1}\right)^{XTB}$$

(4.4-22)

$$BR(T) = BR(T_1) \left(\frac{T}{T_1}\right)^{XTB}$$

(4.4-23)

The temperature dependence of  $C_{JC}$ ,  $C_{JE}$ ,  $C_{JS}$ ,  $\phi_B$ ,  $\phi_C$ , and  $\phi_S$  is given for  $Y \in$  $\{C, E, S\}$  by

$$C_{JY}(T) = C_{JY}(T_1) \cdot [1 + \theta_Y(T)]$$

(4.4-24)

where

$$\theta_Y(T) = MJY \cdot \{0.0004(T - T_1) + 1 - [\phi_Y(T)/\phi_Y(T_1)]\}$$

(4.4-25)

and

$$\phi_Y(T) = \phi_Y(T_1) \cdot (T/T_1) + \phi_{BF}(T) \tag{4.4-26}$$

and where  $\phi_{BF}(T)$  is given by Eq. (4.2-64).

The temperature dependence of  $K_F$  and  $A_F$  is modeled by (4.2-61) and (4.2-62) where  $\phi_B(T)$  is replaced with  $\phi_E(T)$ . Additional details can be found in subroutine TMPUPD of the SPICE source code.

#### 4.5 SUMMARY

Models for the MOSFET, diode, and BJT which are used in the program SPICE have been presented. The similarity between these more detailed models and the simpler models discussed in Chapter 3 should be apparent. Although these models have been presented in the context of SPICE, they should be viewed, in their own right, as a more complete analytical characterization of the three basic devices, which form the nucleus of most integrated circuits. Many parts of these models were not developed specifically for SPICE but rather evolved over the years in the technical literature as researchers attempted to understand the fundamental operation of the basic devices. In many demanding situations, the designers should find the relevant analytical model equations presented in this chapter directly useful for design, insight, and optimization.

The authors have repeatedly observed confusion and uncertainty by both students and practicing engineers about the validity of simulations. This is often attributable to either lack of knowledge of the model used in their simulator or lack of understanding of how specific model parameters impact performance. A firm understanding of the models used in a simulator is essential for utilization of these powerful tools. The glossaries and tables which appear in the appendices of this chapter should prove to be a useful reference for SPICE users.

#### REFERENCES

- A. Vladimirescu, K. Ahang, A. R. Newton, D. O. Pederson, and A. Sangiovanni-Vincentelli, "SPICE Version 2G User's Guide," Dept. of Electrical Engineering and Computer Sciences, University of California, Berkeley, CA, 1981.

- A. Vladimirescu and S. Liu, "The Simulation of MOS Integrated Circuits Using SPICE 2," UCB/ERL M80/7, University of California, Berkeley, Engineering Research Laboratory, Feb. 1980 (Revised Oct. 1980).

- 3. L. W. Nagel, "SPICE 2: A Computer Program to Simulate Semiconductor Circuits," UBC/ERL M520. University of California, Berkeley, Engineering Research Laboratory, May 1975.

- S. Liu, "A Unified CAD Model for MOSFETS," UCB/ERL M 81/31, University of California, Berkeley, Engineering Research Laboratory, May 1981.

- G. D. Anderson, "Evaluation and Optimization of MOS Device Drain Conductance Modeling in the SPICE Level 2 Model," UCB/ERL M84/3, University of California, Berkeley, Engineering Research Laboratory, Jan. 1984.

- SPICE Source Code, Version 2G.6, Electronics Research Laboratory, University of California, Berkeley, March 1983.

- B. J. Sheu, D. L. Scharfetter, and P. K. Ko, "SPICE 2 Implementation of BSIM," UCB/ERL M85/42. University of California, Berkeley, Engineering Research Laboratory, May 1985.

- 8. W. Christopher, "SPICE 3A7 User's Manual," Dept. of Electrical Engineering and Computer Sciences, University of California, Berkeley, 1986.

- T. Quarles, A. R. Newton, D. O. Pederson, and A. Sangiovanni-Vincentelli, "SPICE 3A7 User's Manual," Dept. of Electrical Engineering and Computer Sciences, University of California, Berkeley, 1986.

- 10. P. M. Lee, "BSIM Substrate Current Modeling," UCB/ERL M86/49 University of California, Berkeley, Engineering Research Laboratory, June, 1986.

- 11. J. Pierret, "A MOS Parameter Extraction Program for the BSIM Model," UCB/ERL M84/99, University of California, Berkeley, Engineering Research Laboratory, November 1984.

- 12. M.-C. Jeng, B. J. Sheu, and P. K. Ko, "BSIM Parameter Extraction-Algorithms and User's Guide." UCB/ERL M85/79, University of California, Berkeley, Engineering Research Laboratory, October 1985.

- 13. C. T. Sah, "Characteristics of the Metal-Oxide-Semiconductor Transistor," IEEE Trans. Electron Devices, vol. ED-11, pp. 324-345, July 1964.

- 14. P. Antonetti, D. D. Cariglia, and E. Profumo, "CAD Model for Threshold and Subthreshold Conduction in MOSFETs," IEEE J. Solid State Circuits, vol. SC-17, pp. 454-458, June 1982.

- 15. T. Grotjon and B. Hoefflinger, "A Parametric Short-Channel MOS Transistor Model for Subthreshold and Strong Inversion Current," IEEE J. Solid State Circuits, vol. SC-19, pp. 100-112, Feb. 1984.

- 16. P. Yang, B. Epler, and P. K. Chatterjee, "An Investigation of Charge Conservation Problem for MOSFET Circuit Simulation," IEEE J. Solid State Circuits, vol. SC-18, pp. 128-133, Feb.

- 17. D. E. Ward and R. W. Dutton, "A Charge-Oriented Model for MOS Transient Capacitances," IEEE J. Solid State Circuits, vol. SC-13, pp. 703-708, October 1978.

- 18. "PSPICE Documentation," Micro Sim Corporation, Laguna Hills, CA, 1986.

- 19. R. N. Hall, "Power Rectifiers and Transistors," Proc. IRE, vol. 40, pp. 1512–1519, Nov. 1952.

- 20. H. K. Gummel and H. C. Poon, "An Integral Charge Control Model of Bipolar Transistors," Bell Syst. Tech. Journal, vol. 49, pp. 827-852, May 1970.

- 21. I. Getreu, "Modeling the Bipolar Transistor," Tektronix Inc., Beaverton, Oregon, 1976.

- 22. P. W. Tuinenga, "SPICE: A Guide to Circuit Simulation and Analysis Using PSPICE," Prentice-Hall. Englewood Cliffs, NJ, 1988.

- 23. P. Antognetti and Massobrio, "Semiconductor Device Modeling with SPICE," McGraw-Hill, New York, 1988.

#### **PROBLEMS**

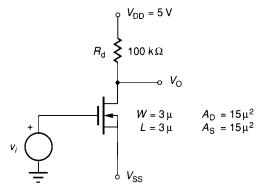

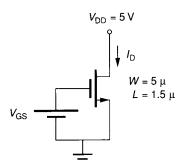

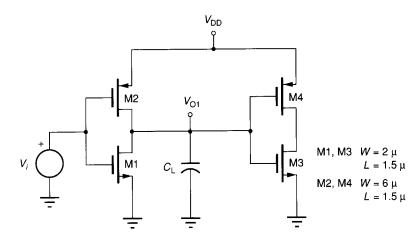

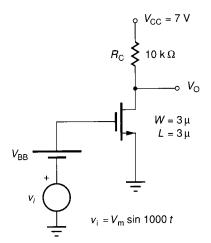

- 4.1. Assume the transistor in Figure P4.1 is fabricated in the CMOS process characterized in Appendix 2B.

- (a) Determine  $V_{SS}$  so that  $V_{OQ} = 1$  V (when  $V_i = 0$ ). Use the Level 1 SPICE MOSFET model.

- (b) Compare the small signal voltage gain using the Level 1 and Level 2 models with  $V_{SS}$  as determined in (a).

- (c) Compare the small signal 3 dB bandwidth using the Level 1 and Level 2 models at the same Q-point as used in (a) and (b).

FIGURE P4.1 Problem 4.1.

FIGURE P4.2 Problem 4.2.

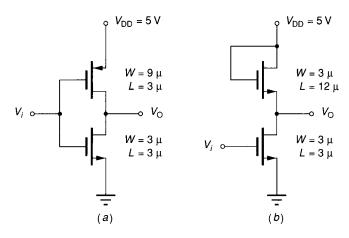

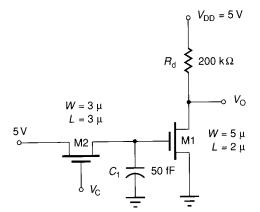

- **4.2.** (a) Use SPICE to obtain the dc transfer characteristics for the two circuits shown in Fig. P4.2, using first the Level 1 model and then the Level 2 model. Assume the transistors are characterized by the CMOS process of Appendix 2B.

- (b) Obtain the low frequency small signal voltage gain for both circuits and plot as the quiescent input voltage is varied between 0 V and 5 V.

- (c) If these circuits are loaded by a 50 fF capacitor, determine the response to a 5 V pulse input that lasts 100  $\mu$ sec.

- (d) If these circuits are biased at  $V_{\rm OQ} = 2.5$  V, determine the small signal 3 dB bandwidth of the voltage gain  $A_v = v_0/v_i$ .

- **4.3.** Compare the dc transfer characteristics ( $I_D$  vs.  $V_{DS}$  as a function of  $V_{GS}$ ) for a MOSFET using the Level 1 and Level 2 SPICE models. Use the SPICE process model parameters of Appendix 2B.

- **4.4.** Compare the small signal output conductance when  $\lambda$  is an input parameter in the Level 2 model to that obtained if  $\lambda$  is calculated by Eq. 4.2-34. Assume the process

- $I_{\rm D}$  axis. Use the process of Appendix 2B and include any subthreshold currents.

FIGURE P4.5 Problem 4.5.

FIGURE P4.6

- **4.6.** In Fig. P4.6, at time t = 0 the control voltage  $V_C$  is taken from 5 V to 0 V and maintained at 0 V.

- (a) If M2 serves as an ideal switch (short between drain and source when  $V_C = 5 \text{ V}$ and open when  $V_C = 0$  V), what is  $V_O(t)$ ?

- (b) Leakage current through the drain or source diffusion of M2 will discharge C. Use the process of Appendix 2B to find how M2 should be laid out to minimize the output voltage droop.

- (c) Plot  $V_{\rm O}(t)$  if the source diffusion of M2 contacting the gate of M1 is 3  $\mu$  ×

- **4.7.** Practically determine and illustrate the effect of the mobility degradation parameters UCRIT, ULTRA, and UEXP on the  $I_D$ - $V_{DS}$  characteristics of the MOSFET.

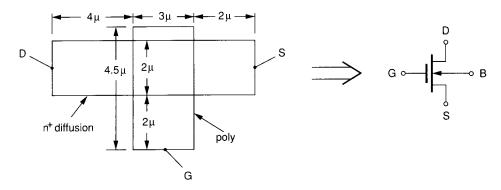

- **4.8.** Plot  $C_{GS}$ ,  $C_{GD}$ ,  $C_{BD}$ ,  $C_{BS}$ , and  $C_{BG}$  in the following two cases for the MOSFET shown in Fig. P4.8.

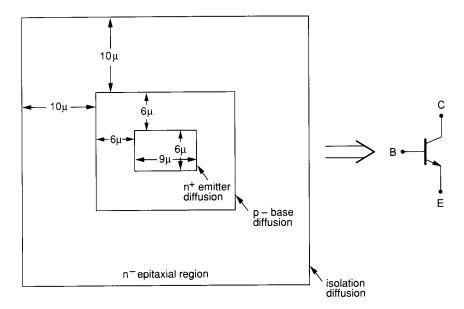

- (a) vs.  $V_{GS}$  for  $0 \le V_{GS} \le 5$  V if  $V_{DS} = 5$  V and  $V_{BS} = -5$  V. (b) vs.  $V_{GS}$  for  $0 \le V_{GS} \le 5$  V if  $V_{DS} = 5$  V and  $V_{BS} = 0$ . **4.9.** Plot  $C_{BE}$ ,  $C_{BC}$ , and  $C_{CS}$  vs.  $I_B$  for 1 nA  $\le I_B \le 100$   $\mu$ A for the BJT shown in Fig. P4.9. Assume  $V_{CE} = 5 \text{ V}$ .

FIGURE P4.8 Problem 4.8.

FIGURE P4.9 Problem 4.9.

- 4.10. A CMOS digital inverter loaded by an identical device is shown in Fig. P4.10. Assume the device is fabricated in the CMOS process of Appendix 2B.

- (a) If a pulse of height 5 V is applied to the input  $(V_i)$  at t = 0, what is the minimum pulse width that can be applied if  $V_{O1}$  must swing down to at least 0.5 V? Assume  $C_L = 0$ .

- (b) How does the minimum pulse width change if 40 identical inverters load the node  $V_{OI}$ ? Assume  $C_L = 0$ .

- (c) If the digital inverter is loaded by only a 2pF load, how does the response time of this circuit compare to that obtained in (a)?

FIGURE P4.10 Problem 4.10.

FIGURE P4.11 Problem 4.11.

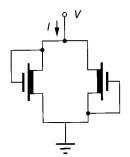

- **4.11.** Plot I vs. V for the circuit shown in Fig. P4.11 for  $-3V \le V \le 3$  V. Assume M1 and M2 matched with  $W = 3 \mu$  and  $L = 30 \mu$ . Use the NMOS process parameters of Appendix 2A.

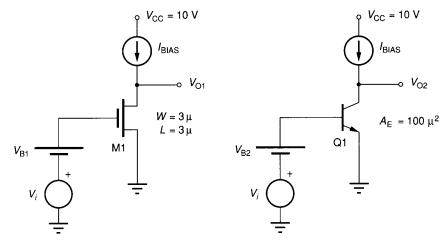

- **4.12.** If  $I_{\rm BIAS}$  in Fig. P4.12 is set to 100  $\mu A$  and  $V_{\rm B1}$  and  $V_{\rm B2}$  are adjusted so that  $V_{\rm OIQ}=V_{\rm O2Q}=5$  V, obtain from SPICE the small signal voltage gain and the 3 dB bandwidth of each circuit for a small signal excitation. Use the SPICE process model parameters of Appendices 2B and 2C and include realistic parasitics for M1 and O1.

- **4.13.** Assume that  $V_{\rm B1}$  and  $V_{\rm B2}$  in Problem 4.12 are fixed at the value needed to make  $V_{\rm O1Q} = V_{\rm O2Q} = 5$  V at room temperature (30°C). What will happen to the Q-point, voltage gain and 3 dB bandwidth for the two circuits of Fig. P4.12 if the temperature is increased to 200°C? Decreased to -50°C?

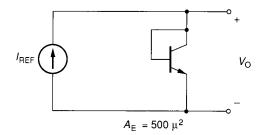

- **4.14.** The circuit shown in Fig. P4.14 has been proposed as a linear temperature transducer (output voltage linearly proportional to temperature). Plot  $V_{\rm O}$  vs. temperature for  $-50^{\circ}{\rm C} \le T \le 200^{\circ}{\rm C}$ , and comment on the suitability of this device as a temperature transducer. Use the model parameters of Appendix 2C in your simulations. Assume  $I_{\rm REF} = 1~\mu A$ .

- **4.15.** Examine the MOSFET shown in Fig. P4.15. (a) Adjust  $V_{\rm BB}$  so that  $V_{\rm OQ}=3$  V.

FIGURE P4.12 Problem 4.12.

FIGURE P4.14 Problem 4.14.

- (b) Determine  $V_{\rm m}$  so that the peak to peak output swing is about 2 V around the Q-point established in (a).

- (c) If the time varying output voltage is 2 V p-p, determine the signal to noise ratio of the output voltage in the frequency band [100 Hz, 20 KHz]. Use the MOS process of Appendix 2B and typical noise parameters.

- (d) Repeat parts (a), (b) and (c) if the MOSFET is replaced with a BJT with an emitter area of 500  $\mu^2$  that is characterized by the process of Appendix 2C and compare with the results obtained for the MOSFET.

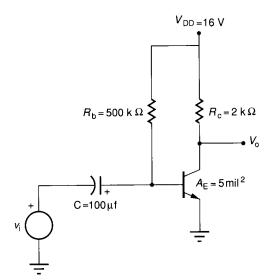

- 4.16. Use SPICE and the process description of Appendix 2C to find the following quantities in the circuit of Fig. P4.16.

- (a) Determine the quiescent output voltage and the small signal model parameters of  $Q_1$  at the Q-point.

- (b) Determine the small signal voltage gain using the ac analysis in SPICE.

- (c) Determine the steady state output voltage using a transient analysis if the input  $v_i(t)$  is defined by

$$v_{i}(t) = \begin{cases} 0 & t < 0 \\ .005 \sin 1000t & t \ge 0 \end{cases}$$

- (d) In calculating a steady state response due to a sinusoidal excitation with SPICE, how does the effort and computation time required for a transient analysis compare to that required for a small signal ac analysis?

- **4.17.** (a) From Eqs. 4.2-21 and 4.2-24, obtain an expression for the effective width reduction, WR =  $W - W_{eff}$ , where  $W_{eff} = W(2 - \eta)$  in terms of the parameter

FIGURE P4.15 Problem 4.15.

FIGURE P4.16 Problem 4.16.

DELTA when the MOSFET is operating in the saturation region.

- (b) For drawn widths of  $W=5~\mu$ , 2  $\mu$ , and 1  $\mu$  plot the effective length,  $L_{\rm eff}$ , of a MOSFET as the drawn length is reduced from 10  $\mu$  to 0.5  $\mu$ . Assume the SPICE model parameters of Appendix 2B remain valid as the drawn length is varied.

- varied.  $+ h_{ab} / h_{ab} = 5V$  and  $h_{ab} / h_{ab} = 5V$

# APPENDIX 4A MOSFET PARAMETER DEFINITIONS

A brief alphabetical listing of the major parameters used in the MOS device models follows. Those parameters that serve specifically as SPICE input parameters are summarized in Table 4A. For more details about these parameters, the reader is referred to the SPICE User's Guide<sup>1</sup> or the SPICE source code<sup>6</sup>.

**AD** represents the area of the drain diffusion. This serves as a SPICE input parameter which is entered on the device element card.

**AF** denotes the flicker noise exponent. This, along with the parameter KF, is used to characterize a noise current source that goes from drain to source in the MOSFET model. The RMS noise current density is given by

$$I_{\rm N} = \sqrt{\frac{8kTg_{\rm m}}{3} + \frac{\rm KF} \cdot I_{\rm dq}^{\rm AF}}{fC_{\rm OX}L^2}}$$

(4A-1)

where  $g_{\rm m}$  is the saturation region transconductance gain at the operating point and  $I_{\rm dq}$  is the quiescent drain current. The first term under the radical represents

TABLE 4A SPICE input parameter summary for MOSFET

|           |                    |                                                                    | ;<br>;                   | ;                        |                 | Charac<br>eqs<br>not er | Characterizing<br>eqs. if<br>not entered |

|-----------|--------------------|--------------------------------------------------------------------|--------------------------|--------------------------|-----------------|-------------------------|------------------------------------------|

| Parameter | Symbol             | Name                                                               | Default if<br>non-zero   | How entered<br>directly† | Levels<br>valid | Level 1                 | Level 1 Level 2                          |

| LEVEL     |                    | Model level (1,2, or 3)                                            | _                        | .MOD (1)                 |                 |                         |                                          |

| VTO       | $V_{ m T0}$        | Zero-bias threshold voltage                                        |                          | .MOD (2)                 | all             | 4.2-16                  | 4.2-16                                   |

| KP        | , ×                | Transconductance parameter                                         | $2 \times 10^{-5} A/V^2$ | .MOD (3)                 | all             | 4.2-11                  | 4.2-11                                   |

| GAMMA     | ٨                  | Bulk threshold parameter                                           |                          | .MOD (4)                 | all             | 4.2-14                  | 4.2-14                                   |

| PHI       | φ.                 | Surface potential                                                  | V 9.                     | .MOD (5)                 | all             | 4.2-15                  | 4.2-15                                   |

| LAMBDA    | ٧                  | Channel-length modulation                                          |                          | .MOD (6)                 | 2               | 4.2-34                  | 4.2-34                                   |

| RD        |                    | Drain ohmic resistance                                             |                          | .MOD (7)                 | all             |                         |                                          |

| RS        |                    | Source ohmic resistance                                            |                          | .MOD (8)                 | all             |                         |                                          |

| CBD       | $C_{ m BD}$        | Zero-bias bulk-drain junction                                      |                          | .MOD (9)                 | all             |                         |                                          |

|           |                    | capacitance                                                        |                          |                          |                 |                         |                                          |

| CBS       | $C_{ m BS}$        | Zero-bias bulk-source junction                                     |                          | .MOD (10)                | all             |                         |                                          |

|           |                    | capacitance                                                        |                          |                          |                 |                         |                                          |

| SI        |                    | Bulk junction saturation current                                   | $10^{-14} \text{ A}$     | .MOD (11)                | all             |                         |                                          |

| PB        | $\phi_{ m B}$      | Bulk junction potential                                            | .5 V                     | .MOD (12)                | all             |                         |                                          |

| CGSO      | $C_{ m GSO}$       | Gate-source overlap capacitance per                                |                          | .MOD (13)                | all             |                         |                                          |