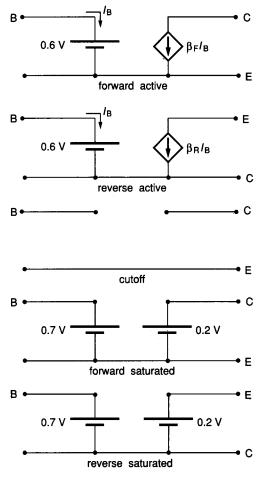

is often adequate for biasing applications and operating point calculations when the device is operating in the forward active region. In the reverse active region the simplified model becomes

$$V_{\rm BC} = 0.6 \text{ V}$$

(3.3-25)

$$I_{\rm E} = \beta_{\rm R} I_{\rm B} \tag{3.3-26}$$

The reader should be cautioned, however, not to attempt to use the value of  $V_{\rm BE}$  or  $V_{\rm BC}$  as given by (3.3-23) or (3.3-25) directly in the Ebers-Moll equations to obtain I<sub>C</sub> or I<sub>B</sub>. Small errors in these junction voltages will result in large errors in the currents because of the exponential relationship of the model.

SATURATION REGION. It will be seen later that most (although not all) digital applications involve switching the BJT between the saturation and cutoff regions. When the device is operating in the saturation region with large positive base and collector currents, it is operating near the forward active region. The base-emitter voltage will be near 0.7 V and the base-collector voltage near 0.5 V. The device can thus be modeled by two voltage sources,  $V_{\rm BE} = 0.7$  V and  $V_{\rm CE} = 0.2$  V, when operating in this region. This collector-emitter voltage in saturation is often termed  $V_{CESAT}$ . When the device is operating in saturation with a large positive base current and a large negative collector current, the device is operating near the reverse active region. The base-collector voltage will be near 0.7 V and the baseemitter voltage near 0.5 V. In this case the device will be modeled by two voltage sources,  $V_{\rm BC} = 0.7$  V and  $V_{\rm CE} = -0.2$  V. This simple modeling approach for the saturation region will be adequate for most hand manipulations. The reader again must be cautioned that these are approximate junction voltage values and thus cannot be used to obtain  $I_{\rm C}$  and  $I_{\rm E}$  in the Ebers-Moll equations since small changes or errors in  $V_{\rm BC}$  and  $V_{\rm BE}$  cause large changes in the corresponding currents. When the collector and base currents must be accurately determined for devices operating in the saturation region, they are often obtained from equations describing the network itself (KVL or KCL) rather than directly from the Ebers-Moll equations. This situation is illustrated in the following example.

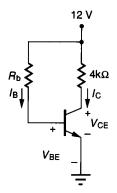

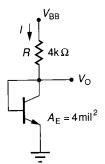

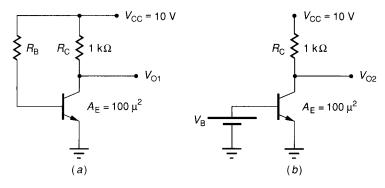

**Example 3.3-2.** Determine good approximations ( $\pm$  5% accuracy is close enough) for the base current, collector current,  $V_{\rm BE}$ , and  $V_{\rm CE}$  for the circuit of Fig. 3.3-4

Example 3.3-2.

if (a)  $R_b = 500 \text{ k}\Omega$ , (b)  $R_b = 100 \text{ k}\Omega$ . Also obtain an accurate expression for  $V_{\text{BE}}$ . Assume the transistor has an emitter area of 4 mil<sup>2</sup>,  $\beta_F = 100$ ,  $\beta_R = 0.2$ ,  $J_S = 6 \times 10^{-10} \ \mu\text{A/mil}^2$ , and  $T = 300 \ ^{\circ}\text{K}$ .

**Solution.** Assume initially that  $I_B$  is in the 0.1  $\mu$ A to 1 mA range. From Example 3.3-1 it can be concluded that  $V_{BE} \simeq 0.6$  V and consequently the current through  $R_b$ , which is also the base current, can be approximated by  $I_b \simeq (11.4 \text{ V})/R_b$ .

(a) With  $R_b = 500 \text{ k}\Omega$ , it follows that  $I_B = 0.0228 \text{ mA}$ , which satisfies the criterion established in Example 3.3-1 on  $I_B$  and thus justifies the initial assumption  $V_{\text{BE}} = 0.6 \text{ V}$ . If it is now assumed (a fact that must later be verified) that the device is operating in the forward active region, it follows from (3.3-15) that  $I_C = 2.28 \text{ mA}$ . With  $I_C = 2.28 \text{ mA}$  it follows that  $V_{\text{CE}} = 12 - (4 \text{ k}\Omega)$  (2.28 mA) = 2.88 V. With  $V_{\text{BE}}$  in the 0.6 V range, it thus can be concluded that  $V_{\text{BC}} < 0$ , thus verifying the initial assumption of operation in the forward active region. It remains to accurately determine  $V_{\text{BE}}$ . Since  $I_C$  is now approximately known, it follows from (3.3-13) with  $V_{\text{t}} = 26 \text{ mV}$  that

$$V_{\rm BE} = (.026 \text{ V}) \ln(I_{\rm C}/I_{\rm S})$$

=  $(.026 \text{ V}) \ln[2.28 \text{ mA/}(6 \times 10^{-10} \cdot 4 \mu\text{A})] = 0.717 \text{ V}$

(b) With  $R_b = 100 \text{ k}\Omega$ , it follows that  $I_B = (11.4 \text{ V})/(100 \text{ k}\Omega) = 0.114 \text{ mA}$ . If we were to assume, as in part (a), that the transistor were operating in the forward active region, we would conclude that  $I_C = 11.4 \text{ mA}$ . Consequently,  $V_{CE} = -33.6 \text{ V}$ , yielding a value for  $V_{BC}$  of 34.2 V, which is in strong violation of the assumption  $V_{BC} < 0.3 \text{ V}$  that was necessary to obtain (3.3-15). It can thus be concluded that the collector current is too large for operation in the forward active region and thus the device is operating in saturation near the forward active region. From the above modeling in the saturation region it can be concluded that

$$V_{\rm BE} \simeq 0.7 \text{ V}$$

$I_{\rm B} \simeq \frac{12 \text{ V} - 0.7 \text{ V}}{100 \text{ k}\Omega} = 0.113 \text{ mA}$

$V_{\rm CE} \simeq 0.2 \text{ V}$

$I_{\rm C} \simeq \frac{12 \text{ V} - 0.2 \text{ V}}{4 \text{ k}\Omega} = 2.95 \text{ mA}$

CUTOFF. When the BJT is operating in cutoff, the collector and base currents are very small compared to those which typically flow in the active and saturation regions. In many applications it is adequate to model the device with  $I_{\rm C}=0$  and  $I_{\rm B}=0$  when operating in the cutoff region. The relative magnitude of the currents in the BJT when operating in cutoff to those when operating in the forward active region are shown in Example 3.3-3.

BJT MODEL SUMMARY. A summary of the simplified dc model for the BJT in the four major regions of operation—forward active, reverse active, saturation, and cutoff—appears in Table 3.3-2. This simplified model should be adequate for most hand calculations except in the seldom used transition region (between cutoff and forward or reverse active) indicated by the lightly shaded region in

**TABLE 3.3-2** Simplified dc model for bipolar transistors

| npn                                                                                   |      |                   |                                                                                                        |

|---------------------------------------------------------------------------------------|------|-------------------|--------------------------------------------------------------------------------------------------------|

| $I_{\rm C} = J_{\rm S} A e^{(V_{\rm BE}/V_{\rm t})} [1 + (V_{\rm CE}/V_{\rm AF})]$    | (1)  | Forward active    | $V_{\rm BE} > 0.5 \text{ V}$                                                                           |

| $I_{\rm B} = \frac{J_{\rm S}}{\beta_{\rm F}} A e^{(V_{\rm BE}/V_{\rm t})}$            | (2)  |                   | $\left(\begin{array}{c} V_{\rm BE} > 0.5 \text{ V} \\ V_{\rm BC} < 0.3 \text{ V} \end{array}\right)$   |

| $I_{\rm E} = J_{\rm S} A e^{(V_{\rm BC}/V_{\rm l})} [1 - (V_{\rm CE}/V_{\rm AR})]$    | (3)  | Reverse active    | $\begin{pmatrix} V_{\rm BC} > 0.5 \text{ V} \\ V_{\rm BE} < 0.3 \text{ V} \end{pmatrix}$               |

| $I_{\rm B} = \frac{J_{\rm S}}{\beta_{\rm R}} A e^{(V_{\rm BC}/V_{\rm t})}$            | (4)  |                   | $V_{\rm BE} < 0.3 \text{ V}$                                                                           |

| $I_{\rm B}=I_{\rm C}=0$                                                               | (5)  | Cutoff            | $(V_{\rm CE}<0,\ V_{\rm BC}<0)$                                                                        |

| $V_{\rm BE} = 0.7  \rm V,  V_{\rm CE} = 0.2  \rm V$                                   | (6)  | Forward saturated |                                                                                                        |

| $V_{\rm BC} = 0.7 \text{ V},  V_{\rm CE} = -0.2 \text{ V}$                            | (7)  | Reverse saturated |                                                                                                        |

| pnp                                                                                   |      |                   |                                                                                                        |

| $I_{\rm C} = -J_{\rm S}Ae^{-(V_{\rm BE}/V_{\rm t})}[1 - (V_{\rm CE}/V_{\rm AF})]$     | (8)  | Forward active    | $V_{\rm BE} < -0.5 \text{ V}$                                                                          |

| $I_{\rm B} = -\frac{J_{\rm S}A}{\beta_{\rm F}}e^{-(V_{\rm BE}/V_{\rm t})}$            | (9)  |                   | $\left(\begin{array}{c} V_{\rm BE} < -0.5 \text{ V} \\ V_{\rm BC} > -0.3 \text{ V} \end{array}\right)$ |

| $I_{\rm E} = -J_{\rm S}Ae^{-(V_{\rm BC}/V_{\rm t})}[1 + (V_{\rm CE}/V_{\rm AR})]$     | (10) | Reverse active    | $\begin{pmatrix} V_{\rm BC} < -0.5 \text{ V} \\ V_{\rm RF} > -0.3 \text{ V} \end{pmatrix}$             |

| $I_{\rm B} = -\frac{J_{\rm S}A}{\beta_{\rm R}}  \mathrm{e}^{-(V_{\rm BC}/V_{\rm t})}$ | (11) |                   | $V_{\rm BE} > -0.3 \text{ V}$                                                                          |

| $I_{\rm B}=I_{\rm C}=0$                                                               | (12) | Cutoff            | $(V_{\rm CE} > 0, V_{\rm BC} > 0)$                                                                     |

| $V_{\rm BE} = -0.7 \text{ V},  V_{\rm CE} = -0.2 \text{ V}$                           | (13) | Forward saturated |                                                                                                        |

| $V_{\rm BC} = -0.7 \text{ V},  V_{\rm CE} = +0.2 \text{ V}$                           | (14) | Reverse saturated |                                                                                                        |

Design parameters: A

Process parameters:  $J_S$ ,  $\beta_F$ ,  $\beta_R$ ,  $V_{AR}$ ,  $V_{AF}$

Environmental parameter: V<sub>t</sub>

All design, process, and environmental parameters are positive for both npn and pnp transistors.

Fig. 3.3-3. For operation in this transition region, the more complicated Ebers-Moll equations 3.3-1 and 3.3-2 are needed.

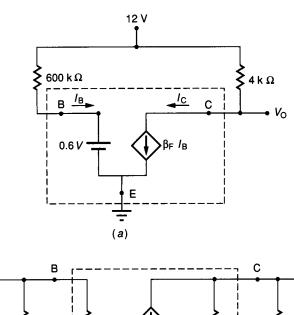

For biasing or operating point calculations, an even simpler model is often adequate. This model is summarized in Table 3.3-3. An equivalent circuit appears in Fig. 3.3-5. This model can be used in place of the model of Table 3.3-2 to reduce computational complexity with minimal loss of accuracy in most biasing applications. This simplified model is generally justified if the base current can be reasonably accurately determined from the circuit in which the BJT is embedded (as in Example 3.3-2) rather than from the exponential relationship between  $I_B$ and  $V_{\rm BE}$  (as in Problem 3.38b).

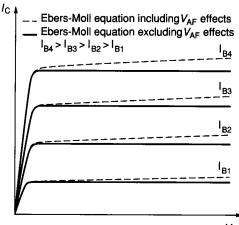

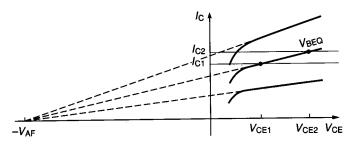

Early voltage effects can be readily included in the Ebers-Moll equations 3.3-1 and 3.3-2 by multiplying  $I_C$  by  $(1 + V_{CE}/V_{AF})$  for  $V_{CE} > 0$  or multiplying  $I_{\rm E}$  by  $(1 - V_{\rm CE}/V_{\rm AR})$  for  $V_{\rm CE} < 0$ . Since the BJT is inherently a good current amplifier, it is common to look at the collector current versus  $V_{CE}$  for different

TABLE 3.3-3

Simplified model of BJT used for biasing and operating point calculations

| Region            | npn                                   |      | pnp                                   |      |

|-------------------|---------------------------------------|------|---------------------------------------|------|

| Forward active    | $I_{\rm C} = \beta_{\rm F} I_{\rm B}$ | (1)  | $I_{\rm C} = \beta_{\rm F} I_{\rm B}$ | (11) |

|                   | $V_{\rm BE}=0.6~{ m V}$               | (2)  | $V_{\rm BE} = -0.6 \text{ V}$         | (12) |

| Reverse active    | $I_{\rm E} = \beta_{\rm R} I_{\rm B}$ | (3)  | $I_{\rm E} = \beta_{\rm R} I_{\rm B}$ | (13) |

|                   | $V_{\rm BC}=0.6~{ m V}$               | (4)  | $V_{\rm BC} = -0.6 \text{ V}$         | (14) |

| Forward saturated | $V_{\rm BE}=0.7~{ m V}$               | (5)  | $V_{\rm BE} = -0.7 \text{ V}$         | (15) |

|                   | $V_{\rm CE}=0.2~{ m V}$               | (6)  | $V_{\rm CE} = -0.2 \text{ V}$         | (16) |

| Reverse saturated | $V_{\rm BC} = 0.7 \text{ V}$          | (7)  | $V_{\rm BC} = -0.7 \text{ V}$         | (17) |

|                   | $V_{\rm CE} = -0.2 \text{ V}$         | (8)  | $V_{\rm CE}=0.2~{ m V}$               | (18) |

| Cutoff            | $I_{\rm C} = 0$                       | (9)  | $I_{\rm C}=0$                         | (19) |

| Cuton             | $I_{\rm B}=0$                         | (10) | $I_{\rm B}=0$                         | (20) |

FIGURE 3.3-5

Equivalent circuits of npn BJT for biasing and operating point calculations.

FIGURE 3.3-6

Typical output characteristics of npn BJT based upon Ebers-Moll model.

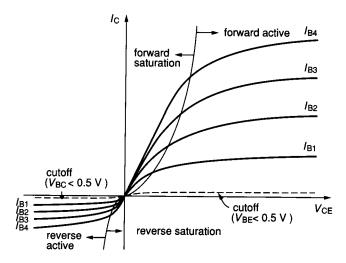

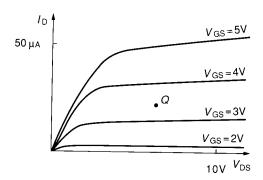

values of the base current,  $I_{\rm B}$ . Such a plot describes what are termed the *output* characteristics. A plot of the output characteristics for a typical BJT is shown in Fig. 3.3-6 for operation in Quadrant 1 of the  $I_{\rm C}$ - $V_{\rm CE}$  plane. The same basic relationship (except curves are spaced closer together) is obtained in Quadrant 3. Results are shown with and without Early voltage effects. The regions of operation of the BJT in the  $I_{\rm C}$ - $V_{\rm CE}$  plane are shown in Fig. 3.3-7. Comparison of the nomenclature used to define the regions of operation of the BJT in Fig. 3.3-7 to that used to identify the corresponding regions for the MOSFET of Fig. 3.1-7 shows that the term saturation is used to define nonanalogous regions for the BJT and MOSFET. As mentioned when the terminology for the operating regions of the MOSFET was discussed, the reader should be aware of this nomenclature to avoid possible confusion.

**FIGURE 3.3-7** Regions of operation for BJT in  $I_C$ – $V_{CE}$  plane.

**Example 3.3-3.** Compare, using the Ebers-Moll model, the collector and base currents in the forward active region to those in cutoff for a transistor with 1 mil<sup>2</sup> emitter area if  $V_{\rm BE} = 0.66$  V,  $V_{\rm BC} = -10$  V in the forward active region, and  $V_{\rm BE} = -0.3$  V,  $V_{\rm BC} = -10$  V in the cutoff region. Use the typical process parameters of Table 3.3-1.

**Solution.** From (3.3-1) and (3.3-2),  $I_{\rm C}$  and  $I_{\rm B}$  in cutoff are  $1.4 \times 10^{-9}~\mu{\rm A}$  and  $1.406 \times 10^{-9}~\mu{\rm A}$  respectively. In the forward active region, it follows from the same equations that  $I_{\rm C} = 63.4~\mu{\rm A}$  and  $I_{\rm B} = 0.641~\mu{\rm A}$ . The relative "smallness" of the device currents in the cutoff region should be apparent from these calculations.

# 3.3.2 Small Signal BJT Model

The small signal model of the bipolar transistor will now be obtained. From Sec. 3.0.2 it can be concluded that the small signal model can be obtained directly from the dc model introduced in the last section. Since there are four regions of operation that have been previously identified in the dc model, there is a different small signal model of the BJT corresponding to each of these regions. The BJT is biased to operate in the forward active region for most small signal applications. The small signal model developed here will be restricted to this region of operation. In the forward active region the collector and base currents can be obtained from

$$I_{\rm C} = J_{\rm S} A e^{(V_{\rm BE}/V_{\rm t})} \left(1 + \frac{V_{\rm CE}}{V_{\rm AF}}\right)$$

(3.3-27)

$$I_{\rm B} = \frac{J_{\rm S}A}{\beta_{\rm E}} e^{(V_{\rm BE}/V_{\rm t})}$$

(3.3-28)

Since the BJT is modeled as a three-terminal device, it remains to find  $y_{11}, y_{12}, y_{21}$ , and  $y_{22}$ , as defined in Sec. 3.0 to obtain the small signal BJT model. Convention has resulted in the selection of the emitter node as the reference. For notational convenience b and c rather than 1 and 2 will be used to denote the base and collector nodes of the BJT, respectively. The parameter  $y_{cb}$ , often termed  $g_m$ , is generally the dominant parameter in the model. From (3.0-5) and (3.3-27) it follows that

$$y_{cb} = g_{\rm m} = \frac{\partial I_{\rm C}}{\partial V_{\rm BE}} \bigg|_{\substack{V_{\rm CE} = V_{\rm CEQ} \\ V_{\rm BE} = V_{\rm BEQ}}} = \frac{J_{\rm S}A}{V_{\rm t}} e^{(V_{\rm BEQ}/V_{\rm t})} \bigg( 1 + \frac{V_{\rm CEQ}}{V_{\rm AF}} \bigg)$$

(3.3-29)

Evaluating (3.3-29) at the Q-point and observing that  $V_{\rm CEQ}/V_{\rm AF} << 1$ , it follows from (3.3-27) and (3.3-29) that

$$g_{\rm m} = \frac{I_{\rm CQ}}{V_{\rm t}} \tag{3.3-30}$$

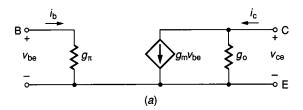

The balance of the y parameters can be readily obtained from (3.0-5), (3.3-27), and (3.3-28). These parameters are summarized in Table 3.3-4. Also listed in this table is the equivalent h parameter model. The h parameter model has been included since it is also widely used. The small signal model equivalent circuits appear in Fig. 3.3-8.

TABLE 3.3-4

Small signal model parameters for the BJT

| y Parameters                                                    | h Parameters                                          |

|-----------------------------------------------------------------|-------------------------------------------------------|

| $y_{cb} = g_{\rm m} = \frac{I_{\rm CQ}}{V_{\rm t}}$             | $h_{fe} = \beta_{\mathrm{F}}$                         |

| $y_{be} = g_{\pi} = \frac{g_{\text{m}}}{\beta_{\text{F}}}$      | $h_{ie} = \frac{\beta_{\rm F} V_{\rm t}}{I_{\rm CQ}}$ |

| $y_{bc}=0$                                                      | $h_{re}=0$                                            |

| $y_{cc} = g_o = \frac{g_m V_t}{V_{AF}} = \frac{I_{CQ}}{V_{AF}}$ | $h_{oe} = rac{I_{	ext{CQ}}}{V_{	ext{AF}}}$           |

### Fundamental parameter relationships

$$r_{\pi} = 1/g_{\pi} = h_{ie}$$

$r_{o} = 1/g_{o} = 1/h_{oe}$

$\beta_{F} = g_{m}r_{\pi}$

#### **FIGURE 3.3-8**

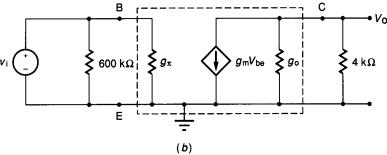

Small signal model of bipolar transistor: (a) y parameter model (Note:  $r_{\pi} = 1/g_{\pi}, r_{o} = 1/g_{o}$  and  $\beta_{F} = g_{m}r_{\pi}$ ), (b) h parameter model.

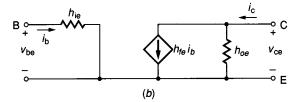

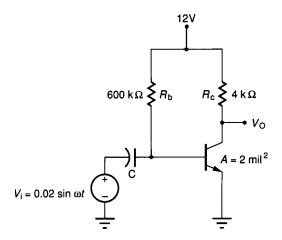

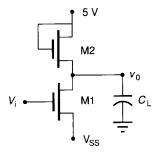

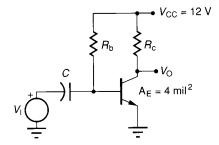

**Example 3.3-4.** For the circuit shown in Fig. 3.3-9, determine (a) the quiescent output voltage, (b) the small signal steady state output voltage, and (c) the total output voltage. Use the typical process parameters of Table 3.3-1 to characterize the BJT.

#### Solution

(a) To obtain the Q-point it suffices to use the equivalent circuits of Fig. 3.3-5. If it is assumed that the BJT is operating in the forward active region, the circuit of Fig. 3.3-10a is obtained. From Ohm's law, it follows that

$$I_{\rm BQ} = (12 \ {\rm V} - 0.6 \ {\rm V})/(600 \ {\rm k}\Omega) = 19 \ \mu {\rm A}$$

so that

$$I_{\rm CQ} = \beta_{\rm F} I_{\rm BQ} = 1.9 \text{ mA}$$

**FIGURE 3.3-9** Example 3.3-4.

**FIGURE 3.3-10** Solution of Example 3.3-4: (a) Equivalent circuit for biasing, (b) Small signal equivalent circuit.

Hence the quiescent output voltage,  $V_{OQ}$ , is given by  $V_{OQ} = 12 \text{ V} - I_{CQ}R_c = 4.4$ V. With  $V_0 = 4.4$  V it follows that the assumption of operation in the forward active region is valid.

(b) Assuming C is large enough to act as a short circuit for ac signals, it follows from the model of Fig. 3.3-8 that the circuit can be drawn as in Fig. 3.3-10b. From Table 3.3-4 it follows that the small signal transistor g parameters at room temperature ( $V_t = 26 \text{ mV}$ ) are

$$g_{\rm m} = 73.1$$

mmho

$g_{\pi} = 0.731$  mmho

$g_{\rm o} = 9.5$   $\mu$ mho

From Ohm's law

$$v_o = (-g_m v_i) \left( \frac{1}{g_o + 1/(4k\Omega)} \right)$$

$$v_o / v_i = -282$$

The small signal steady state output voltage thus becomes

$$v_{\rm o}(t) = 5.64 \sin \omega t$$

(c) The total output voltage is the sum of the quiescent and small signal steady state values; hence

$$V_{\rm O}(t) = 4.4 \text{ V} - (5.64 \sin \omega t) \text{ V}$$

The minus sign appears in the sum to maintain the correct phase relationship between  $V_0$  and  $I_1$  in this example.

# **High-Frequency BJT Model**

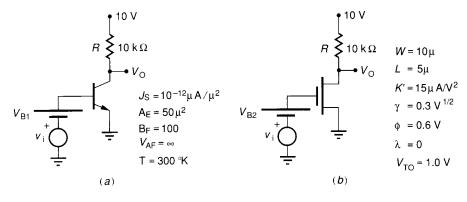

At high frequencies both the dc and small signal models of the BJT introduced in the previous sections are generally considered inadequate. These limitations are primarily attributable to the unavoidable parasitic capacitances inherent in existing bipolar integrated circuits.

These capacitances are of two types. The first type is composed of pn junction capacitances. These capacitances, which are voltage dependent, can be modeled as in the MOSFET and diode cases by (3.1-14) and (3.2-8) provided the junction is not forward biased by any more than  $\phi_{\rm B}/2$  or about 0.35 V. Since the BJT is typically operated with at least one junction forward biased, it is necessary to model the parasitic junction capacitances under forward bias.

For forward biases greater than  $\phi_B/2$ , it follows from (3.2-9) that the charge storage capacitance can be approximated by 12 region

$$C_{\rm j} = 2^n C_{\rm j0} A \left[ 2n \frac{V_{\rm F}}{\phi_{\rm B}} + (1 - n) \right]$$

(3.3-31)

where  $V_{\rm F}$  is the forward bias on the junction. This linear approximation is a continuous extension of (3.1-14) across  $V_F = \phi_B/2$  that also agrees in slope at the transition point (see Problem 3.31). The model of the BJT junction capacitances is identical to that of the pn junction diode given in (3.2-8) and (3.2-9).

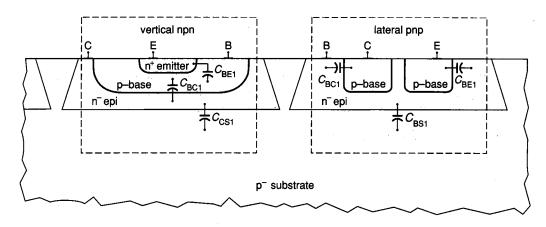

The cross sections of a vertical npn and a lateral pnp transistor are shown in Fig. 3.3-11. The parasitic junction capacitors for all junctions are identified. Note that the vertical structure has parasitic base-collector, base-emitter, and collector-substrate capacitances, whereas the lateral structure has base-emitter, base-collector, and base-substrate parasitics.

The second type of capacitance is due to majority carrier charge accumulation in the base region, which occurs under forward bias near the emitter junction and introduces a second parasitic between the base and emitter. This capacitance, which is also voltage dependent, can be modeled by

$$C_{AC} = \frac{t_{\rm f}I_{\rm CQ}}{kT} = t_{\rm f}g_{\rm m}$$

(3.3-32)

where  $t_f$  is the forward base transit time and  $I_{CQ}$  is the quiescent collector current. The process parameter  $t_f$  is related to the base width,  $W_B$ , and the electron diffusion constant,  $D_n$ , by the expression

$$t_{\rm f} = \frac{W_{\rm B}^2}{2D_n} \tag{3.3-33}$$

The capacitance  $C_{\rm AC}$  is added to the base-emitter junction capacitance to obtain the total base-emitter parasitic capacitance. Typical values of  $t_{\rm f}$  range from 0.1 to 1 ns for vertical npn transistors and from 20 to 40 ns for lateral pnp transistors. <sup>13</sup> The parasitic capacitors for both the vertical and lateral BJT are summarized in Table 3.3-5.

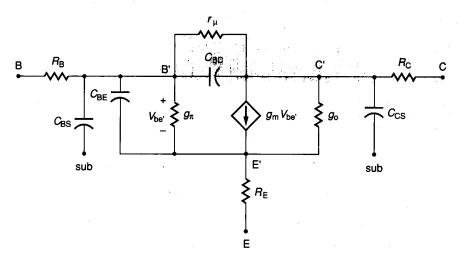

A high-frequency small signal equivalent circuit for the BJT is shown in Fig. 3.3-12. In addition to the parasitic capacitors discussed above, four resistive parasitics are shown. These resistive parasitics are present at all frequencies. The resistance  $R_{\rm C}$ ,  $R_{\rm E}$ , and  $R_{\rm B}$  represent the ohmic resistance between the metal contact and the junctions in the transistor. Layouts that minimize the distance between the contacts and junctions minimize these resistors. Note that a "primed"

FIGURE 3.3-11

Parasitic junction capacitors in vertical npn and lateral pnp transistors.

| <b>TABLE 3.3-5</b>        |     |     |

|---------------------------|-----|-----|

| Parasitic capacitance for | the | BJT |

|                           |     |     |

|                 | Transistor type       |                                  |                                  |  |  |

|-----------------|-----------------------|----------------------------------|----------------------------------|--|--|

|                 | Alternate<br>notation | Lateral                          | Vertical                         |  |  |

| C <sub>BE</sub> | $C_{\pi}$             | $C_{\text{BE1}} + C_{\text{AC}}$ | $C_{\text{BEI}} + C_{\text{AC}}$ |  |  |

| $C_{BC}$        | $C_{\mu}$             | $C_{\mathrm{BC1}}$               | $C_{\mathrm{BC1}}$               |  |  |

| $C_{BS}$        | •                     | $C_{\mathtt{BS1}}$               | 0                                |  |  |

| $C_{\rm CS}$    | ·                     | 0                                | $C_{CS1}$                        |  |  |

notation has been used to denote the E, B, and C terminals of the effective BJT. The distinction between the "primed" terminals and the actual terminals is necessary since the series ohmic resistances in the emitter, base, and collector leads were neglected when the model of the BJT was derived.

$R_{\rm E}$  is in the 1  $\Omega$  range and is essentially voltage independent. This low value is due to the shallow depth and high doping density of the emitter region. Although the value is small, the reader must be cautioned that even small resistors in the emitter circuit can significantly affect circuit performance (see Problem 3.44). The resistors  $R_{\rm C}$  and  $R_{\rm B}$  are typically in the 100  $\Omega$  range. They are both somewhat voltage dependent.

The resistor  $r_{\mu}$ , which appears from the base to collector, is large in value and can be approximated by 13

$$r_{\mu} \simeq 10\beta_{\rm F}/g_{\rm o} \tag{3.3-34}$$

In many applications  $r_{\mu}$  can be ignored.

FIGURE 3.3-12 High-frequency small signal equivalent circuit of BJT.

## 3.3.4 Measurement of BJT Model Parameters

As stated in Section 3.1.4, experimentally measured process parameters are of considerable use to the circuit designer. As in the MOS case, automated measurement equipment is available for bipolar process characterization. In the absence of such equipment, several of the more important BJT device parameters can be measured with reasonable accuracy in the laboratory using standard laboratory equipment. Techniques for measuring  $J_S$ ,  $\beta_F$ ,  $\beta_R$ ,  $V_{AF}$ , and  $V_{AR}$  will be discussed in this section.

From Table 3.3-2, the expressions for the collector and base currents of the npn transistor in the forward active region are

$$I_{\rm C} = J_{\rm S} A e^{(V_{\rm BE}/V_{\rm t})} \left( 1 + \frac{V_{\rm CE}}{V_{\rm AF}} \right)$$

(3.3-35)

and

$$I_{\rm B} = \frac{J_{\rm S}}{\beta_{\rm F}} A \exp\left(\frac{V_{\rm BE}}{V_{\rm t}}\right) \tag{3.3-36}$$

These expressions will serve as a guide for measuring  $J_S$ ,  $\beta_F$ , and  $V_{AF}$ . Measurements of the parameters should be made with  $I_C$  close to the intended operating point if possible.

**Measurement of**  $V_{AF}$ **.** Equation 3.3-35 (extended by Eq. 3.3-1 for small  $V_{CE}$ ) is plotted in Fig. 3.3-13 for several different values of  $V_{BE}$ . Note that all extended curves intersect the  $V_{CE}$  axis at  $V_{CE} = -V_{AF}$ . The parameter  $V_{AF}$  can thus be determined by fixing  $V_{BE}$  and measuring the  $V_{CE}$  axis intercept. If  $I_{C1}$  and  $I_{C2}$  are the collector currents corresponding to the two different collector–emitter voltages  $V_{CE1}$  and  $V_{CE2}$  respectively, as depicted in Fig. 3.3-13, then

$$V_{\rm AF} = \frac{I_{\rm C2}V_{\rm CE1} - I_{\rm C1}V_{\rm CE2}}{I_{\rm C1} - I_{\rm C2}}$$

(3.3-37)

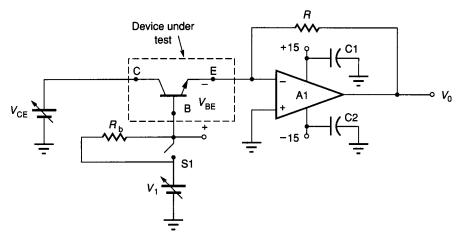

The circuit of Fig. 3.3-14 with S1 closed can be used for making this measurement. Initially set  $V_{\rm CE}$  at  $V_{\rm CE2}$  (10 V would be reasonable) and adjust  $V_1 = V_{\rm BE}$  so that the desired collector current,  $I_{\rm C2}$ , flows ( $I_{\rm C} = -V_{\rm O}/R$ ). Leav-

**FIGURE 3.3-13** Projection of I-V characteristics of BJT into second quadrant.

A 356 op amp is a reasonable choice for A1. C1 and C2, which may be needed for stability, should be as close as possible to the supply terminals of the op amp to prevent oscillation. A value of  $1\mu F$  for these capacitors is reasonable. Note: Care should be taken to avoid ever making  $V_1 > V_{CE}$  with S1 closed, as this will permanently damage the transistor since no mechanism is provided to limit current flow when the base-collector junction is forward biased.

#### **FIGURE 3.3-14**

Circuit for measuring bipolar transistor parameters.

ing  $V_{\rm BE}$  fixed ( $V_{\rm BE} = V_{\rm BEQ}$ ), reduce  $V_{\rm CE}$  (2 V would be reasonable) to  $V_{\rm CE1}$  and measure the current  $I_{\rm C1}$ .  $V_{\rm AF}$  now follows from (3.3-37). Reasonably wide separation between  $V_{\rm CE1}$  and  $V_{\rm CE2}$  should be maintained to reduce the sensitivity to the measured voltages and currents.

**Measurement of J\_S.** The previous circuit with S1 closed can be used for measuring  $I_S = J_S A$ . By measuring the temperature in  ${}^{\circ}K$ ,  $V_t$  can be calculated from Eq. 3.3-3. If  $I_{C2}$  and  $V_{CE2}$  are the initial collector current and collector—emitter voltage used in the measurement of  $V_{AF}$ , then it follows from (3.3-35) that it remains to accurately measure  $V_{BE} = V_1$  to obtain  $I_S$  from the expression

$$I_{S} = \frac{I_{C2} \exp(-V_{BE}/V_{t})}{1 + V_{CE2}/V_{AF}}$$

(3.3-38)

Once  $I_S$  is obtained,  $J_S$  can be determined by dividing by the emitter area, A. For measuring  $J_S$  little accuracy would be lost by either neglecting  $V_{AF}$  or using a typical value of  $V_{AF}$  in (3.3-38). Accurate measurement of  $V_{BE}$  is, however, required.

**Measurement of \beta\_F.** The circuit of Fig. 3.3-14 with S1 open can be used to measure  $\beta_F$ . Adjust  $V_1$  to obtain the desired collector current,  $I_C = -V_O/R$ , and adjust  $V_{CE}$  to obtain the desired collector-emitter voltage. Measure  $I_B = (V_1 - V_{BE})/R_b$ . From (3.3-34) and (3.3-35) it thus follows that

$$\beta_{\rm F} = \frac{I_{\rm C}/I_{\rm B}}{1 + V_{\rm CE}/V_{\rm AF}} \tag{3.3-39}$$

As in the case of the measurement of  $J_S$ , little accuracy is lost if  $V_{AF}$  is neglected or replaced by its nominal value. Since  $\beta_F$  is quite current dependent, it is particularly important that it be measured at a value close to the intended operating point.

Methods of measuring  $\beta_R$  and  $V_{AR}$  parallel those discussed for  $\beta_F$  and  $V_{\rm AF}$  and are left to the reader, as are modifications for measuring parameters of pnp transistors. Information about the parasitic capacitors is generally required for high-frequency applications. Because of their small size, direct measurement with an acceptable degree of accuracy using standard laboratory equipment is not possible. Special test circuits, which either have exceptionally large test devices or which can be used to measure these parasitics indirectly through an investigation of the frequency response of the circuit, are often used.

### PASSIVE COMPONENT MODELS

Discrete passive components are quite easy to model. Resistors and capacitors can generally be modeled by ideal resistors and capacitors respectively. The major limitations are manufacturing tolerances and temperature deviations—both of which can be reduced to acceptable levels in most applications through judicious component selection/specification.

Monolithic resistors and capacitors are far from ideal. They are typically both temperature and voltage dependent. The practical range of values is seriously limited by area constraints. Large resistor or capacitor values are impractical. Process deviations preclude accurate control of absolute component values. Parasitic effects are often quite significant. Relative accuracy (ratioing) between passive components is, however, often quite good.

The following figures of merit are used to characterize passive components.

#### Resistors

- 1. Sheet resistance

- 2. Resistance density

- **3.** Temperature coefficient of resistance

- 4. Voltage coefficient of resistance

- **5.** Absolute accuracy

- 6. Relative (ratio) accuracy

#### Capacitors

- 1. Capacitance density

- 2. Temperature coefficient of capacitance

- 3. Voltage coefficient of capacitance

- 4. Absolute accuracy

- 5. Relative (ratio) accuracy

The sheet resistance, temperature coefficients, and voltage coefficients were discussed in Chapter 2. The resistance density is generally a function of the process parameters and layout design rules. The capacitance density is a process parameter. The absolute accuracy is a measure of how accurately the actual resistor and capacitor values can be controlled during processing.

The relative (ratio) accuracy is a measure of how closely two resistors or capacitors can be matched. The ratio accuracy is affected by component placement on a die, device geometry, the physical size of the components, and the nominal relative values of the components themselves.

The parasitic effects were not listed above in the figures of merit primarily because of the difficulty in obtaining a single figure with which to meaningfully quantify the parasitic effects. Nevertheless, parasitic effects include contact resistance and distributed capacitances for resistors. Contact resistance, overlap stray capacitances, and edge capacitances are considered as parasitic effects for capacitors.

## 3.4.1 Monolithic Capacitors

Any structure in which a voltage-induced separation of charge occurs can serve as a capacitor. Some of the structures used for capacitors, along with their characteristics<sup>14</sup> are shown in Table 3.4-1. In a MOS process, the most common capacitors are formed by sandwiching a thin oxide layer between two conductive polysilicon layers. These capacitors are nearly independent of applied voltage and can be modeled as ideal capacitors. The major limitation is the large parasitic capacitor that is always formed between the lower plate and the substrate. This parasitic limits how these capacitors can be used although clever design techniques, such as stray-insensitive SC filters, 15-16 often evolve to minimize these effects.

When the luxury of the double polysilicon layers is not present in MOS processes, metal-poly, metal-diffusion (lower plate formed by a diffused region in the substrate), or poly-diffusion capacitors with an SiO2 dielectric are used. These capacitors typically have a lower capacitance density and/or increased voltage dependence and/or a less conductive lower plate than the double poly capacitors.

In the bipolar process, the most desirable common capacitors are metaldiffusion capacitors with an SiO2 dielectric. The heavily doped emitter diffusion is used for the lower diffusion plate. The characteristics are quite good, but an additional mask step is required for forming the dielectric region. Alternatives include the voltage-dependent junction capacitances formed by either the B-C or B-E junction. These capacitors are modeled by (3.1-14) and (3.3-31). The B-E junction offers reasonable capacitance density at the expense of a limited reverse breakdown voltage (typically 5 to 7 V). The B-C junction reverse breakdown voltage is quite high (typically in the 30 V range), but the capacitance density is quite low. All junction capacitors are limited by requirements that the junctions remain reverse biased (actually, not forward biased by more than a few tenths of a volt).

TABLE 3.4-1 Characteristics of monolithic capacitors

| Capacitor<br>type   | Process     | Dielectric       | Absolute<br>accuracy | Ratio<br>accuracy | Voltage<br>characteristic | Temperature | Comments                              |

|---------------------|-------------|------------------|----------------------|-------------------|---------------------------|-------------|---------------------------------------|

| Poly-Poly           | MOS         | SiO <sub>2</sub> | ±20%                 | ±0.06%            | —5 ppm/V                  | 25 ppm/°C   | Most popular MOS, best characteristic |

| Poly-Diffusion      | MOS         | SiO              | ÷10%                 | 790.0€            | -20  ppm/V                | 25 ppm/°C   | Lower plate potential often fixed     |

| Metal-Diffusion     | MOS/Bipolar | SiO <sub>2</sub> | ±10%                 | ₹0.06%            | -20  ppm/V                | 25 ppm/°C   | Most desirable bipolar                |

| (with thin oxide)   |             |                  |                      |                   |                           |             |                                       |

| Moat-Substrate      | MOS         | Si               |                      |                   |                           |             | Voltage dependent                     |

| Base-Collector      | Bipolar     | Si               |                      |                   |                           |             | Must be reverse biased, low           |

|                     |             |                  |                      |                   |                           |             | density                               |

| Base-Emitter        | Bipolar     | Si               |                      |                   |                           |             | Must be reverse biased                |

| Conductor-Conductor | Thin film   | Varies           |                      |                   |                           |             | Good characteristics                  |

| Screened            | Thick film  | Varies           |                      |                   |                           |             | Chip capacitors often preferred       |

### 3.4.2 Monolithic Resistors

Considerably more options exist for monolithic resistors. Some monolithic resistors are passive devices and others contain active devices. Major tradeoffs must be made between linearity, area, biasing complexity, and temperature characteristics in monolithic resistors. Table 3.4-2 lists the characteristics of some of the structures that are used for resistors.

In standard MOS processes, the most ideal resistors are merely strips of polysilicon. Diffusion strips are also used for resistors but exhibit an undesirable nonlinear relationship between voltage and current. Ion implants offer some advantages over depositions for the introduction of impurities to control absolute resistance values in diffused resistors. Thin film resistors with excellent characteristics are added in some specialized processes. For each of these types of resistors, a serpentine pattern is often used to improve packing density. The major limitations of these resistors are the low resistance densities, which limit the total resistance to quite small values; the high deviations in resistance due to process variations; and large temperature coefficients.

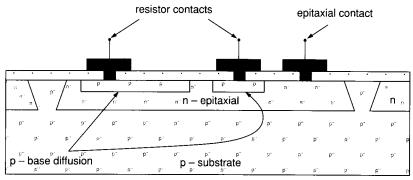

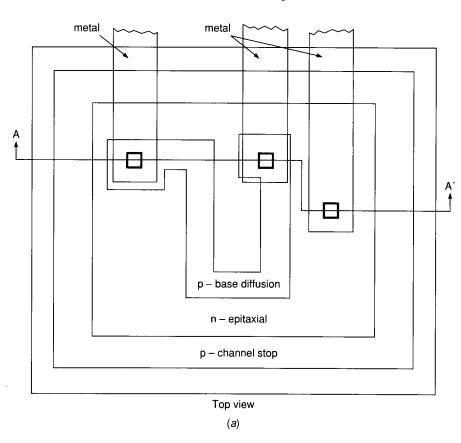

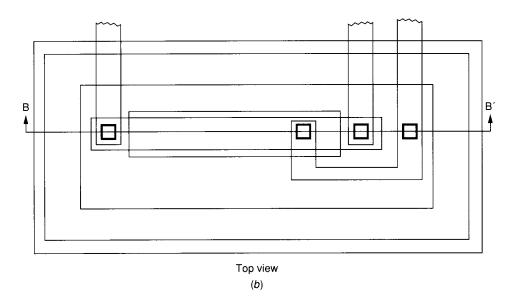

In bipolar processes epitaxial strips or diffusion strips are commonly used for resistors. These devices are quite linear. The base diffusion is often used because of its reasonably high sheet resistance. A base-diffused resistor is shown in Fig. 3.4-1a. To prevent forward biasing of the "base-collector" junction, a contact is needed to the epitaxial layer. This will be typically connected to the most positive power supply voltage used for the circuit.

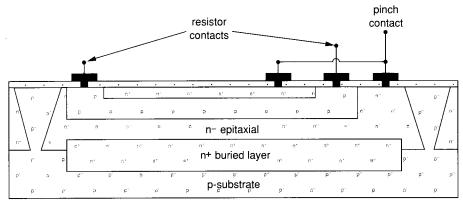

It can be argued that the resistance of the base-diffused resistor could be increased if the depth of the p-base diffusion could be decreased. The depth of this diffusion, however, is generally determined to optimize performance of the BJTs themselves. An alternative is to place an n<sup>+</sup> emitter diffusion in the p base region. This masking step already exists and will result in a significant increase of the sheet resistance of the underlying p diffusion. Such a device, which is termed a pinch resistor, is shown in Fig. 3.4-1b. Contact must be made to both the n<sup>+</sup> emitter diffusion and the n<sup>-</sup> epitaxial region. These regions are typically both connected to the most positive power supply voltage used for the circuit. Although the resistance increases significantly due to this pinching, the variance in emitter and base diffusion depths due to process variations makes the tolerances of pinch resistors quite wide. They also exhibit an increased voltage dependent nonlinearity and are limited in voltage range to circumvent breakdown of the reverse-biased base-emitter junction. Other types of pinch resistors (e.g., epitaxial pinch) can also be made.

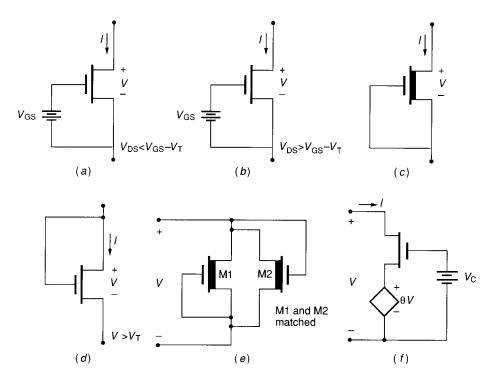

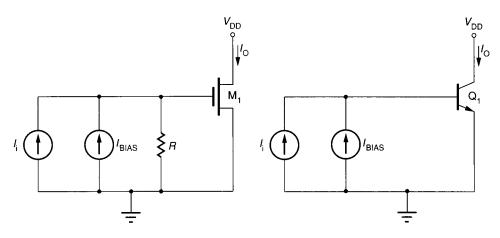

Several active resistors are shown in Fig. 3.4-2. These active resistors often offer considerable reductions in area requirements compared to passive resistors at the expense of increased nonlinearity and/or reduced signal swing and/or complicated biasing requirements. A more detailed discussion of the active resistor structures appears in Chapter 5.

The circuit of Fig 3.4-2a is merely a MOSFET biased to operate in the ohmic region. From (3) of Table 3.1-1, the relationship between  $I_D$  and  $V_{GS}$  is

$$I_{\rm D} = \frac{K'W}{L} \left( V_{\rm GS} - V_{\rm T} - \frac{V_{\rm DS}}{2} \right) V_{\rm DS}$$

(3.4-1)

TABLE 3.4-2 Characteristics of MOS Resistors

| Device                                                                                                                             | Characterizing equation                                                                     | Ideal<br>resistance†                                                      |

|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Poly Strip                                                                                                                         | $V = I R_{\square} \frac{L}{W}$                                                             | $R = R \square \frac{L}{W}$                                               |

| Diffusion                                                                                                                          | $V = I R_{\square} \frac{L}{W}$                                                             | $R = R_{\square} \frac{L}{W}$                                             |

| MOSFET (Ohmic region, Fig. 3.4-2a)                                                                                                 | $I = \frac{K'W}{L}[(V_{GS} - V_T) - \frac{V}{2}]V$                                          | $R = \frac{L}{K'W(V_{GS} - V_T)}$                                         |

| MOSFET (Saturated region, Fig. 3.4-2b)                                                                                             | $I = \frac{K'W}{2L} (V_{GS} - V_T)^2 (1 + \lambda V)$                                       | $R_{SS} = \frac{2L}{\lambda K' W (V_{GS} - V_T)^2}$                       |

| MOS depletion $I = \begin{cases} \text{MOS depletion} & I = \begin{cases} \text{MOS depletion} & \text{MOS depletion} \end{cases}$ | $\frac{K'W}{L}(-V_T)V \qquad V < -V_T$ $\frac{K'W}{2L}V_T^2(1 + \lambda V) \qquad V > V_T$  | $R = \frac{L}{K'W \mid V_T \mid}$ $R_{SS} = \frac{2L}{K'W V_T^2 \lambda}$ |

| MOS Enhancement (Fig. 3.4-2d)                                                                                                      | $I = \frac{K'W}{2L}(V - V_T)^2(1 + \lambda V)$                                              | $R_{SS} = \frac{L}{K'W(V_Q - V_T)}$                                       |

| Linearity Compensated I8 (Fig. 3.4-2e) $I = \begin{cases} I = \begin{cases} I = I \\ I = I \end{cases}$                            | $\frac{2K'W}{L}(-V_T)V \qquad V < -V_T$ $\frac{K'W}{L}V_T^2(1 + \lambda V) \qquad V > -V_T$ | $R = \frac{L}{2K'W \mid V_T \mid}$ $R_{SS} = \frac{L}{K'W V_T^2 \lambda}$ |

| Bootstrapped Budak <sup>17</sup> (Fig. 3.4-2 <i>f</i> )                                                                            | $I = \frac{K'W}{L}(V_C - V_T - V\frac{[\theta + 1]}{2})(1 - \theta)V$ $V < V_C - V_T$       | $R = \frac{L}{K'W(1-\theta)}$                                             |

If  $V_{\rm DS}$  << ( $V_{\rm GS}-V_{\rm T}$ ), then, as seen in Eq. 3.4-1, the relationship between  $I_{\rm D}$  and  $V_{\rm DS}$  is linear (assuming  $V_{\rm GS}$  is independent of  $V_{\rm DS}$ ), resulting in an equivalent resistance of

$$R_{\rm eq} \simeq \frac{L}{K'W \left(V_{\rm GS} - V_{\rm T}\right)} \tag{3.4-2}$$

This approximation is quite good for  $V_{\rm DS}$  < 0.5( $V_{\rm GS}$  -  $V_{\rm T}$ ). A model that includes the nonlinearity is

$$R_{\rm eq} \simeq \frac{L}{K'W \left[ (V_{\rm GS} - V_{\rm T}) - V_{\rm DS}/2 \right]}$$

(3.4-3)

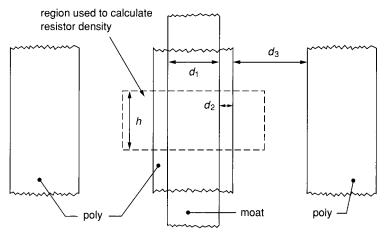

The resistance density (resistance per unit area) of the MOS resistor will now be calculated. Assume  $d_1$  is the minimum moat width,  $d_2$  the minimum

| Resistance<br>density‡                                   | Temperature characteristic | Absolute accuracy | Relative accuracy | Comments                                           |

|----------------------------------------------------------|----------------------------|-------------------|-------------------|----------------------------------------------------|

| $\frac{R_{\square}}{d_4(d_s+d_4)}$                       | 1500 ppm/°C                | ±30%              | ±2%               | Linear, low resistance density                     |

| $\frac{R_{\square}}{d_3(d_3+d_4)}$                       | 1500 ppm/°C                | ±35%              | ±2%               | Somewhat voltage dependent                         |

| $\frac{1}{K'(V_{GS}-V_T)d_1(d_1)}$                       | $+ 2d_2 + d_3$             |                   |                   | To minimize distortion, $V < (V_{GS} - V_T)/2$     |

| $\frac{1}{\lambda \frac{K'}{2} (V_{GS} - V_T)^2 d_1(a)}$ | $d_1 + 2d_2 + d_3$         |                   |                   | Small signal impedance only, high impedance values |

| $\frac{1}{K' \mid V_T \mid d_1(d_1 + 2d_2)}$             | $\frac{1}{(2+d_3)}$        |                   |                   | Popular load device                                |

| $\frac{1}{\lambda \frac{K'}{2} V_T^2 d_1 (d_1 + 2d_2 -$  | + d <sub>3</sub> )         |                   |                   | Quite nonlinear                                    |

| $\frac{1}{K'(V_Q - V_T)d_1(d_1 + \dots + d_N)}$          |                            |                   |                   | Quite nonlinear, good resistance density           |

| $\frac{1}{2K' \mid V_T \mid d_1(d_1 + 2d_1)}$            | - '                        |                   |                   | Major improvement in density                       |

| $\frac{1}{\lambda K' V_T^2 d_1 (d_1 + 2d_2 +$            | $-d_3$ )                   |                   |                   |                                                    |

| Depends upon how $\theta V$ is realized                  |                            |                   |                   | Good linearity potential                           |

$<sup>\</sup>dot{\tau}R$  denotes large signal impedance;  $R_{SS}$  denotes small signal impedance only.

\$Assuming a minimum size layout, see Fig. 3.4-3  $d_1$ ,  $d_2$ ,  $d_3$ , and  $d_4$  as defined in Sec. 3.4.2.

required overlap of poly over moat, and  $d_3$  the minimum poly-poly spacing as defined by the design rules of the process. If a large serpentine MOS device is constructed with minimum moat width and with separate polysilicon strips for each diffusion strip in the serpentine and if the incremental area required by the corners is neglected, then the diagram of Fig. 3.4-3 can be used to calculate the resistance density of this device. The section of length h has a resistance of

$$R = \frac{h}{K' d_1 (V_{GS} - V_T)}$$

(3.4-4)

and an area of

$$A = h(d_3 + d_1 + 2d_2) (3.4-5)$$

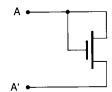

Cross-sectional view along AA

**FIGURE 3.4-1** Monolithic resistors: (a) Base diffused, (b) Base-pinch.

Cross-sectional view along BB'

FIGURE 3.4-1 (continued)

so a resistance density of

$$R_d = \frac{1}{K'(V_{GS} - V_T)(d_1 + 2d_2 + d_3)d_1}$$

(3.4-6)

Although making  $V_{\rm GS}$  close to  $V_{\rm T}$  can make  $R_d$  very high, it is generally impractical due to process variations to directly make  $V_{\rm GS}-V_{\rm T}<1$  V. Some improvements in resistance density can be realized if the polysilicon strips are merged into one large rectangular region. In this case, the minimum diffusion spacings will determine how close the serpentined strips can be placed. If the MOSFET is a depletion device, it is particularly convenient to make  $V_{\rm GS}=0$  as shown in Fig. 3.4-2c, thus eliminating the need for a voltage source.

**FIGURE 3.4-2** Active MOS resistors.

**FIGURE 3.4-3** Calculation of resistance density of MOS resistor in ohmic region.

**Example 3.4-1.** Compare the area required to make a 1 M $\Omega$  resistor using a minimum size POLY I string with that using a MOS depletion resistor operating in the saturation region with  $V_{\rm GS}=0$ . Use the design rules and process parameters of the NMOS process discussed in Appendix 2A of Chapter 2. Assume the POLY I is uncovered and the feature size of the process is 3  $\mu$  (i.e.,  $\lambda=1.5~\mu$ ).

**Solution.** The resistance density of the POLY I string can be readily obtained (see Problem 3.55) and is given by

$$R_{dp} = \frac{R_{\square}}{d_4(d_3 + d_4)} \tag{3.4-7}$$

where  $d_3$  is the minimum poly spacing,  $d_4$  is the minimum poly width, and  $R_{\square}$  is the sheet resistance of POLY I. From Tables 2A.2 and 2A.4 of Appendix A of Chapter 2,  $d_3=3$   $\mu$ ,  $d_4=3$   $\mu$ , and  $R_{\square}=25$   $\Omega/\square$ . Substituting into (3.4-7), it follows that  $R_{dp}=1.39$   $\Omega/\mu^2$ .

If the MOSFET shown in Fig. 3.4-2c is biased to operate in the saturation region, then, from (4) of Table 3.1-1, the drain current is given by

$$I_{\rm D} = \frac{K'W}{2L} (V_{\rm GS} - V_{\rm T})^2 (1 + \lambda V_{\rm DS})$$

The small signal impedance can be obtained by differentiation (assuming  $V_{\rm GS}$  and  $V_{\rm BS}$  constant) with respect to  $V_{\rm DS}$  to obtain

$$R_{\rm ss} = \frac{2L}{[\lambda K' W (V_{\rm GS} - V_{\rm T})^2]}$$

(3.4-8)

Defining  $d_1$ – $d_3$  as in Fig. 3.4-3, it follows that the resistance density for a large serpentined structure is

$$R_{ds} = \frac{2}{[\lambda K' d_1 (V_{GS} - V_T)^2 (d_1 + 2d_2 + d_3)]}$$

(3.4-9)

From Tables 2A.2 and 2A.4 of Chapter 2,  $\lambda = 0.01 \text{ V}^{-1}$ ,  $K' = 25 \,\mu\text{A/V}^2$ ,  $V_T = -3 \,\text{V}$ ,  $d_1 = 3 \,\mu$ ,  $d_2 = 3 \,\mu$ , and  $d_3 = 3 \,\mu$ . Substituting into (3.4-9) and setting  $V_{GS} = 0$ , we obtain  $R_{ds} = 74 \,\text{k}\Omega/\mu^2$ . It follows that the area ratio is the ratio of the resistance densities; that is, the ratio of  $R_{dp}$  to  $R_{ds}$ , which is about 67,000 to 1. The area required to make the 1 M $\Omega$  poly resistor is about  $9 \times 10^5 \,\mu^2$ , whereas the active resistor requires an area of around 13  $\mu^2$ .

Note that for reasonable values of  $V_{\rm GS}-V_{\rm T}$ , the  $\lambda$  in the denominator of (3.4-9) makes the resistance density of the MOS resistor in the saturation region considerably higher than the resistance density of the same device biased to operate in the ohmic region. Small signal resistances in the 1 M $\Omega$  range become practical with the MOS resistor biased to operate in the saturation region.

Several other MOS active resistors are shown in Fig. 3.4-2. Those of Fig. 3.4-2c and d have proven the most popular in NMOS applications due to their simplicity. The structures of Fig. 3.4-2e and f offer improvements in linearity at the expense of increased area and/or complexity. The characteristics of these active loads are summarized in Table 3.4-2.

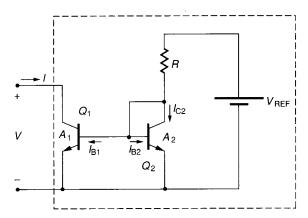

A popular bipolar active resistor is shown in Fig. 3.4-4. The equivalent resistance and resistance density will now be calculated.

FIGURE 3.4-4

Active bipolar resistor.

Assuming  $Q_2$  is operating in the active region and that  $\beta_F$  is large enough so that  $(I_{B1} + I_{B2}) << I_{C2}$ , it follows from (2) of Table 3.3-3 that

$$I_{\rm C2} \simeq (V_{\rm REF} - 0.6 \,\text{V})/R$$

(3.4-10)

and from (1) of Table 3.3-2 (neglecting  $V_{\rm AF}$ , which is justifiable since  $V_{\rm CE2} \simeq 0.6~{\rm V} << V_{\rm AF}$ ),

$$I_{\rm C2} \simeq J_{\rm S} A_2 \exp\left(\frac{V_{\rm BE2}}{V_{\rm t}}\right) \tag{3.4-11}$$

Equating the two expressions for  $I_{C2}$ , it follows that

$$\exp\left(\frac{V_{\text{BE2}}}{V_{\text{t}}}\right) \simeq \frac{V_{\text{REF}} - 0.6 \text{ V}}{RJ_{\text{S}}A_{2}} \tag{3.4-12}$$

Again, from (1) of Table 3.3-2, it follows that

$$I = J_{S}A_{I}\left(1 + \frac{V}{V_{AF}}\right) \exp\left(\frac{V_{BEI}}{V_{t}}\right)$$

(3.4-13)

Since  $V_{\rm BE1} = V_{\rm BE2}$  it follows from (3.4-12) and (3.4-13) that

$$I = \frac{A_1 \left(1 + \frac{V}{V_{AF}}\right) (V_{REF} - 0.6 \text{ V})}{A_2 R}$$

(3.4-14)

The small signal impedance follows from differentiation with respect to V and is given by

$$R_{eq} = \frac{V_{AF} A_2 R}{A_1 (V_{REF} - 0.6 \text{ V})}$$

(3.4-15)

It can be shown that for large R, the area of R dominates that of  $Q_1$  and  $Q_2$ ; hence the resistance density is approximately m times that of R where

$$m = \left(\frac{V_{\text{AF}}}{V_{\text{REF}}}\right) \left(\frac{A_2}{A_1}\right) \tag{3.4-16}$$

It can be seen that this active resistor can easily result in an area savings of from 10 to 1000 over that required for the resistor R. The high output impedance of the circuit of Fig. 3.4-4 will be exploited in the discussion of current mirrors in Chapter 5.

Both active and passive resistors are used in IC designs. When area required for passive resistors becomes excessive, the designer should consider the active resistor alternative but must bear in mind that the active resistors are typically nonlinear and often require special biasing considerations.

### 3.5 SUMMARY

In this chapter, models for MOSFETs, diodes, BJTs, and passive components have been developed. Included are large signal dc models, small signal models, and high-frequency models of varying degrees of complexity. Small signal models were obtained by differentiation of the large signal dc models, and high-frequency models were obtained by identifying the relevant parasitic capacitances inherent in the processes in which the devices were fabricated. This multiple-model approach allows the user to select the simplest model acceptable for a given application. The most notable differences between the MOSFET and the BJT are (1) square law contrasted to exponential dc transfer characteristics, and (2) different input impedances, characterized by a nearly infinite input impedance for the MOSFET contrasted to a small input impedance for the BJT. The models developed here will be used for analysis and design throughout later chapters and will be expanded for use in computer simulations in Chapter 4.

### REFERENCES

- 1. C. T. Sah, "Characteristics of the Metal-Oxide-Semiconductor Transistor," IEEE Trans. Electron. Devices, vol. ED-11, pp. 324-345, July 1964.

- 2. H. Shichman and D. A. Hodges, "Modeling and Simulation of Insulated-Gate Field-Effect Transistor Switching Circuits," IEEE J. Solid State Circuits, vol. SC-3, pp. 285-289, Sept. 1968.

- 3. R. Muller and T. Kamins, Device Electronics for Integrated Circuits, Wiley, New York, 1977, Chapter 7.

- 4. J. Millman and C. Halkias, Integrated Electronics: Analog and Digital Circuits and Systems, McGraw-Hill, New York, 1972.

- 5. A. Sedra and K. Smith, Microelectronic Circuits, Holt, Rinehart & Winston, New York, 1982.

- 6. C. Duvurry, "A Guide to Short Channel Effects in MOSFETS," TI Engineering Journal, Texas Instruments Inc., pp. 52-56, July-August 1984.

- 7. A. Vladimirescu and S. Liu, "The Simulation of MOS Integrated Circuits Using SPICE2," Memorandum No. UCB/ERL M80/7, Electronics Research Laboratory, University of California, Berkeley, Feb. 1980.

- 8. L. Stotts, "Introduction to Implantable Biomedical IC Design," IEEE Circuits and Devices Magazine, pp. 12-18 January 1989.

- Y. Tsividis and P. Antognetti, eds., Design of MOS VLSI Circuits for Telecommunications, Prentice-Hall, Englewood Cliffs, New Jersey, 1985, Chapter 4.

- 10. P. Gray, D. Hodges, and R. Brodersen, eds., Analog MOS Integrated Circuits, IEEE Press, New York, 1980, p. 31.

- 11. J. J. Ebers and J. L. Moll, "Large Signal Behavior of the Junction Transistor," Proc. IRE, Vol. 42, pp. 1761-1772, Dec. 1954.

- 12. I. Getreu, Modeling the Bipolar Transistor, Tektronix Inc., Beaverton, Oregon, 1976.

- P. Gray and R. Meyer, Analysis and Design of Analog Integrated Circuits, Wiley, New York, 1977.

- P. E. Allen and D. R. Holberg, CMOS Analog Circuit Design, Holt, Rinehart & Winston, New York, 1987.

- R. Gregorian and G. C. Temes, Analog MOS Integrated Circuits for Signal Processing, Wiley, New York, 1986.

- P. E. Allen and E. Sánchez-Sinencio, Switched Capacitor Circuits, Van Nostrand Reinhold, New York, 1984.

- 17. K. Nay and A. Budak, "A Voltage-Controlled Resistance with Wide Dynamic Range and Low Distortion," *IEEE Trans. on Circuits and Systems*, vol. CAS-30, pp. 770–772, October 1983.

- 18. K. Peterson and R. L. Geiger, "CMOS OTA Structures with Improved Linearity," *Proc. 27th Midwest Symposium on Circuits and Systems*, Morgantown, WV, pp. 63–66, June 1984.

- B. J. Sheu, D. L. Scharfetter, and P. K. Ko, "SPICE2 Implementation of BSIM", UCB/ERL M85/42, Engineering Research Laboratory, University of California, Berkeley, May 1985.

## **PROBLEMS**

### Section 3.0

**3.1.** A linear three-terminal network can be characterized in terms of the *y*-parameters by the equations

$$i_1 = y_{11}v_1 + y_{12}v_2$$

$$i_2 = y_{21}v_1 + y_{22}v_2$$

Obtain the corresponding small signal equivalent circuit.

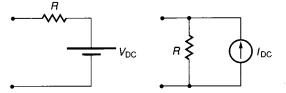

- 3.2. Show that the small signal Thevenin equivalent circuits of both of the circuits in Fig. P3.2 are resistors of value R using the definitions of Section 3.0-3.

- 3.3. Develop a small signal model for a device characterized by the following equations:

$$I_1 = 5(V_1 - 4)$$

$I_2 = -25(V_1 - 2)^3 \left(1 + \frac{V_2}{5}\right)$

#### Section 3.1

- **3.4.** Verify that if a MOSFET is modeled by Eq. (3.1-1), the designation of "source" and "drain" is arbitrary (i.e., the same I–V characteristics are obtained if the node initially labeled "drain" is called the "source" and the node initially labeled "source" is called the "drain").

- 3.5. Derive an expression for the MOSFET for the locus of points in the  $I_{\rm D}$ - $V_{\rm DS}$  plane where

**FIGURE P3.2** Circuits for Problem 3.2.

$$\frac{\partial I_{\rm D}}{\partial V_{\rm DS}} = 0$$

Assume the device is modeled by Eq. 3.1-1.

3.6. Assume a MOS device is to be modeled in the saturation region by the equation

$$I_{\rm D} = \frac{K'W}{2L} (V_{\rm GS} - V_{\rm T})^2 \tag{P1}$$

but that the device is actually characterized by the equation

$$I_{\rm D} = \frac{K'W}{2L} (V_{\rm GS} - V_{\rm T})^2 \left(1 + \frac{V_{\rm DS}}{20}\right)$$

(P2)

where  $V_{\rm T}$  is assumed constant in both equations. Also assume that the unknown parameters K' and  $V_{\rm T}$  are to be experimentally obtained from (P1) by measuring  $I_{\rm D}$  at  $V_{\rm GS}=2.0$  V and again at  $V_{\rm GS}=2.2$  V with  $V_{\rm DS}=2$  V and then solving simultaneously the two versions of (P1) to obtain the two unknowns. Further assume that W=5  $\mu$ , L=15  $\mu$ , and the measured values of  $I_{\rm D}$  are 6.336  $\mu$ A and 8.624  $\mu$ A at 2.0 and 2.2 V respectively.

- (a) What values will be obtained for the parameters K' and  $V_T$ ?

- (b) What percentage error between experimental and theoretical results will be obtained in using Eq. P1 and the parameters obtained in (a) to predict  $I_D$  if the device is to operate at  $V_{GS} = 2.1$  V and  $V_{DS} = 2.5$  V?

- (c) What percentage error between experimental and theoretical results will be obtained in using Eq. P1 and the parameters obtained in (a) to predict  $I_D$  if the device is to operate at  $V_{GS} = 6$  V and  $V_{DS} = 15$  V?

- (d) How can correlation between theoretical and experimental results be improved?

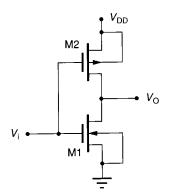

- **3.7.** The transfer characteristics for the CMOS inverter shown in Fig. P3.7 are plotted parametrically in Fig. 3.1-13b for the case that  $V_{\rm DD} > V_{\rm T0N} V_{\rm T0P}$ . Plot parametrically the transfer characteristics of this circuit if  $V_{\rm DD} < V_{\rm T0N} V_{\rm T0P}$  and identify the mode of operation of each transistor in each region.

- **3.8.** The small signal model of the MOSFET is used most often for the analysis of MOS circuits in which the transistors are operating in the saturation region.

- (a) Derive the small signal low frequency model for the MOS transistor operating in the ohmic region with Q-point  $I_{\rm DQ}$ ,  $V_{\rm GSQ}$ ,  $V_{\rm DSQ}$ , and  $V_{\rm BSQ}$ .

- (b) What does this reduce to if  $V_{DSQ} = 0$  V?

FIGURE P3.7 Circuit for Problem 3.7.

FIGURE P3.9 Circuit for Problem 3.9.

3.9. One easy way to include  $\lambda$  and  $\gamma$  effects in the calculation of  $V_0$  for the circuit shown in Fig. P3.9 is to set up an iteration defined for N=1 by

$$V_{\text{T1}} = V_{\text{T0}}$$

$$I_{\text{D1}} = \frac{K'W}{2L} (V_{\text{T1}})^2$$

$$V_{\text{O1}} = I_{\text{D1}}R$$

and for N > 1,

$$\begin{split} V_{\text{TN}} &= V_{\text{TO}} + \gamma \Big( \sqrt{\phi + V_{\text{O},N-1}} - \sqrt{\phi} \Big) \\ I_{\text{DN}} &= \frac{K'W}{2L} (V_{\text{TN}})^2 [1 + \lambda (V_{\text{DD}} - V_{\text{O},N-1})] \\ V_{\text{ON}} &= I_{\text{DN}} R \end{split}$$

How many iterations are required for  $I_{DN}$  to converge to within 0.01% of its actual value if M1 is fabricated in the NMOS process of Table 3.1-2 and if  $W = 3 \mu$ ,  $L = 12 \mu$ ,  $R = 20 \text{ k}\Omega$ , and  $V_{DD} = 6 \text{ V}$ ?

- **3.10.** Obtain an expression for and plot the maximum deviation over the ohmic region, in percentage, from the current as predicted by (3.1-1) from that obtained if (3.1-1) is multiplied by  $(1 + \lambda V_{DS})$  to maintain continuity at the ohmic region-saturation region interface.

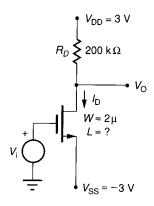

- **3.11.** Assume the MOSFET in Fig. P3.11 is characterized by the CMOS model parameters of Table 3.1-2.

FIGURE P3.11 MOSFET for Problem 3.11

- (a) Determine L so that  $A_V = v_0/v_1 = -25$ . What is the Q-point  $(V_{OQ}, I_{DQ})$  with this value of L?

- (b) Determine L so that  $V_{\rm OQ}=OV$  . What is  $A_V=v_{\rm o}/v_{\rm i}$  with this value of L?

- **3.12.** Obtain the dc model for the devices shown in Fig. P3.12. Make a qualitative comparison of the performance of these structures.

- 3.13. The output characteristics for a MOSFET with  $V_{\rm BS}=0$  are shown in Fig. P3.13.

- (a) Determine as many parameters as possible from the set

$$\{K', V_{T0}, \gamma, \lambda, W, L, K'W/L, \phi, C_{ox}\}$$

(b) If the device is biased to operate at the point Q, determine as many parameters as possible of the set  $\{g_{\rm m}, g_{\rm ds}, g_{\rm mb}\}$ .

FIGURE P3.12 Devices for Problem 3.12.

FIGURE P3.13 Graph for Problem 3.13.

- **3.14.** Plot  $g_m$ ,  $g_{ds}$ , and  $g_{mb}$  versus  $I_{DQ}$  on the same axis for  $I_{DQ}$  in the interval [100] nA, 10 mA] for a MOSFET with  $W = L = 5 \mu$  designed in the CMOS process characterized in Table 3.1-2.

- 3.15. Determine the small signal model of the MOSFET operating in weak inversion saturation. Compare this model to that of the same device if it operates in strong inversion.

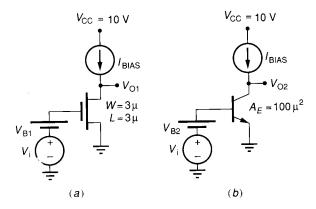

- 3.16. A simple single transistor amplifier is shown in Fig. P3.16.

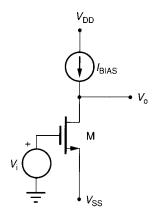

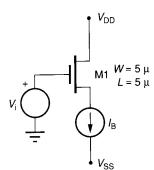

- (a) Using the typical CMOS process parameters of Table 3.1-2, determine W/L of M so that  $I_{DQ} = I_{BIAS} = 20 \mu A$ , if  $V_{SS} = -2 \text{ V}$  and  $V_i = 0 \text{ V}$ .

- (b) Determine the small signal voltage gain  $A_V = v_0/v_i$  for the value of W/Lobtained in (a).

- (c) If the subthreshold parameters  $I_{\rm DO}$  and n of (3.1-32) are  $I_{\rm DO}=20$  nA and n=2, determine W/L of M so that  $I_{DQ}=I_{BIAS}=20~\mu A$  at room temperature if  $V_{SS} = -0.1 \text{ V}$  and  $V_i = 0 \text{ V}$ .

- (d) Determine the small signal voltage gain  $A_{\rm V} = v_{\rm o}/v_{\rm i}$  for the value of W/Lobtained in (c) and compare these results with that obtained for operation in strong inversion.

- 3.17. Obtain an expression for and plot I versus V for the enhancement load circuit of Fig. P3.17 based upon the MOSFET model of Table 3.1-1, and compare these transfer characteristics with those used for the simple model of Eq. 3.1-45.

Problem 3.16.

FIGURE P3.17 Circuit for Problem 3.17.

- 3.18. Derive the small signal model for the MOSFET operating in the saturation region from the dc model of the MOSFET given by Eq. 3.1-5. Verify that these results are equivalent to those given in Table 3.1-3.

- **3.19.** If  $I_B = 50 \,\mu\text{A}$ , then M1 in Fig. P3.19 is operating in strong inversion for  $V_i = 0$ . If  $I_B$  remains constant, how much must the W/L ratio of M1 be increased to force M1 into subthreshold? Assume  $I_{DO} = 20$  nA, n = 2,  $K' = 24 \mu A/V^2$ , and  $V_T =$ 0.75 V.

- **3.20.** Consider a single MOS transistor. If  $V_{\rm BS}=0$  and  $V_{\rm DS}>3V_{\rm t}$ , determine the value of  $V_{\rm GS}$  at the intersection of the strong inversion drain saturation current of (4) in Table 3.1-1 with the weak inversion current. How does this relate to the transition region of Eq. 3.1-31? Assume  $I_{DO} = 20$  nA, n = 2 in Eq. 3.1-32,  $K' = 24 \mu A/V^2$ , and  $\lambda = 0$ .

- **3.21.** Obtain the output voltage for the circuit layout of Color Plate 10 if  $V_{\rm DD} = 5 \text{ V}$  and  $V_{\rm I} = 2$  V. Assume the devices were fabricated in the NMOS process summarized in Appendix 2A.

- 3.22. In the saturation region of operation, most of the channel region is characterized by an inversion layer, which is an extension of the source as depicted in Fig. 2.2-2f. This represents a series impedance in the source. Assuming the voltage drop is sufficiently small that Eq. 3.1-8 applies, calculate the series source-channel impedance, R<sub>sc</sub>. Note: Due to a tapering of the channel near the drain, the source-channel impedance is actually about 50% larger than that predicted by (3.1-8).

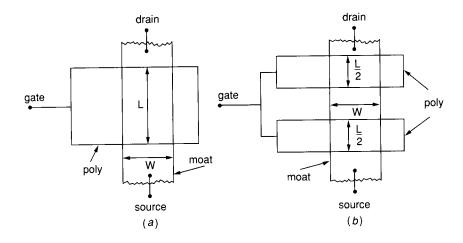

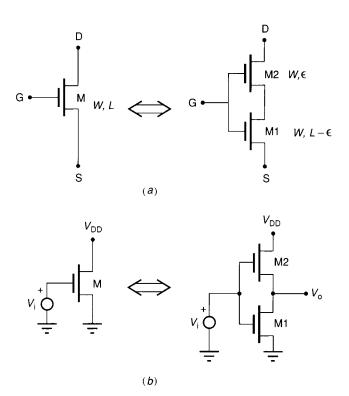

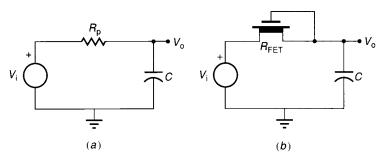

- 3.23. If  $\gamma$  and  $\lambda$  effects are neglected, a MOSFET of width W and length L is equivalent to the series connection of the two devices as shown in Fig. P3.23 where  $\epsilon$  is any real number which satisfies the expression  $0 < \epsilon \le L$ .

FIGURE P3.19 Circuit for Problem 3.19.

FIGURE P3.23

Circuits for Problem 3.23.

- (a) If the MOSFET M is operating in the saturation region, show that in the equivalent circuit of Fig. P3.23a, M1 is operating in the ohmic region and M2 in the saturation region.

- (b) If the equivalent MOSFET is connected as shown if Fig. P3.23b and M is operating in the saturation region, derive an expression for  $V_0$  in terms of  $V_i$ .

- (c) Calculate the equivalent impedance of M1 in Fig. P3.23b assuming  $V_i$  is sufficiently small that (3.1-8) applies.

# 3.24. For the circuit of Fig. P3.24,

(a) Calculate parametrically the output thermal noise current in the frequency band  $10 \text{ kHz} \le f \le 200 \text{ kHz}$  and the output flicker noise current in the same

FIGURE P3.24 Circuit for Problem 3.24.

FIGURE P3.25

Circuit and graph for Problem 3.25.

band if  $K_f = 3 \times 10^{-24} \text{ V}^2 \cdot \text{F}$  at the dc operating point determined by  $V_i = 0$ .

- (b) Calculate parametrically the equivalent input referred offset voltage.

- (c) Calculate the signal to noise ratio of the output current if  $V_{\rm BIAS} = 2$  V and  $V_{\rm i} = 0.25 \sin 10^5 t$  over the frequency band given in (a). Neglect  $\lambda$  and  $\gamma$  effects and assume the remaining process parameters given in Appendix 2B.

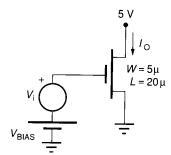

- **3.25.** A plot of  $V_{\rm GS}$  versus  $\sqrt{I_{\rm D}}$  for an NMOS transistor is shown in Fig. P3.25. It has  $\mu C_{\rm ox} = 60~\mu {\rm A/V}^2,~V_{\rm BS} = 0$ , and the remainder of the characterization parameters as indicated in the NMOS design rules discussed in Chapter 2.

- (a) Is the device a depletion or enhancement transistor?

- (b) What mode of operation is the device in?

- (c) What is W/L?

- (d) What is the threshold voltage?

- (e) What will the horizontal axis intercept if  $V_{BS}$  is changed to -9 V?

- **3.26.** The pn junction between an n<sup>+</sup> moat diffusion and substrate is used to form a capacitor. Determine the value of this capacitor with a reverse bias of 6 V if the area of the n<sup>+</sup> moat diffusion is 16 mil<sup>2</sup>. Assume the process parameters of the NMOS process of Appendix 2A.

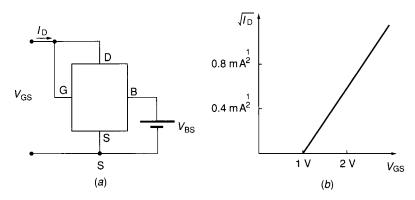

- **3.27.** Compare the minimum area required to build a first-order lowpass filter with a 3 db cutoff frequency of 2 kHz using the two techniques shown in Fig. P3.27a and b

FIGURE P3.27

Circuits for Problem 3.27.

FIGURE P3.28

Circuit for Problem 3.28.

respectively. Assume  $R_p$  is made of a poly resistor with  $R_{\square} = 30 \ \Omega/\square$ .  $R_{\text{FET}}$  is biased to operate in the ohmic region ( $K' = 15 \,\mu\text{A/V}^2$ ,  $V_{\text{T0}} = -3.5 \,\text{V}$ ,  $\gamma = 0$ ,  $\phi = 0$ ,  $\lambda = 0$ ), the capacitance density is 0.2 pF/mil<sup>2</sup>, and both  $R_p$  and  $R_{\text{FET}}$  are serpentined with minimum feature width of 5  $\mu$ , minimum feature spacing of 5  $\mu$ , and a gate-moat overlap of 2.5  $\mu$ . Derive all equations needed.

- **3.28.** The voltage  $V_{\rm SS}$  can be used to establish the quiescent drain currents with  $V_{\rm i}=0$ . Obtain an expression for the 3 db bandwidth of the circuit in Fig. P3.28 in terms of  $I_{\rm DQ}$  and the model parameters of M1 and M2. Neglect all parasitic capacitors in M1 and M2.

- 3.29. Determine the small signal equivalent circuit for the circuit shown in Fig. P3.29.

- **3.30.** Assume a MOSFET is characterized in strong and weak inversion by Eqs. (3.1-4) and (3.1-33) respectively.

- (a) Show that if the transconductance gain is to be continuous at the strong inversion-weak inversion interface, then the transition must occur at  $V_{\rm GS} = V_{\rm T} 2n\,V_{\rm t}$ .

- (b) Show that if  $I_D$  is to be continuous at the transition determined in (a), then  $I_{DO}$  and K' must be related by the equation

$$I_{DO} = \frac{K'2(nV_{\rm t})^2}{e^2}$$

### Section 3.2

- **3.31.** Show that the forward-biased pn junction capacitance model of Eq. 3.2-9 is a continuous and differentiable extension of the reverse-bias model of Eq. 3.2-8 at the transition  $V = \phi_B/2$ .

- **3.32.** Assume a depletion region capacitor is characterized by  $C_{\rm ox} = 250 \, {\rm fF/mil}^2$ ,  $\phi = 0.6 \, {\rm V}$ , n = 1/2, and  $A = 6 \, {\rm mil}^2$ . Determine the bias voltage required to reduce the capacitance to half of what it is at 0 V bias.

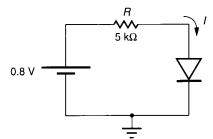

- 3.33. Accurately determine I in Fig. P3.33. Assume the diode is characterized by the BE diffusion of the bipolar process of Appendix 2C with a junction area of  $500 \,\mu^2$ . Assume operation at  $T=30^{\circ}$  C.

FIGURE P3.29 Circuit for Problem 3.29.

FIGURE P3.33 Circuit for Problem 3.33.

- **3.34.** Assume the vertical npn base-collector junction of the process of Appendix 2C is to be used as a varactor diode.

- (a) Determine the area of the base needed to generate a capacitance of 50 pF with a reverse bias of 3 V.

- (b) Plot the capacitance of this diode versus reverse bias for  $-5 \le V_{\rm BC} \le 0$ .

- (c) Repeat part (a) if the BE junction is used instead of the BC junction in the same process.

- **3.35.** A diode can be fabricated in the bipolar process of Appendix 2C in several ways. Give all ways that the diode can be fabricated and compare the performance characteristics from both dc and ac viewpoints. Include in your discussion a characterization of all relevant parasitics.

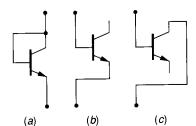

- **3.36.** A "diode-connected transistor" is shown in Fig. P3.36a. Compare the performance of this to that of the BE and BC diodes (Figs. P3.36b and c) in the bipolar process of Appendix 2C.

- **3.37.** The circuit shown in Fig. P3.37 is proposed as a rectifier. Compare the dc performance of this to that of the pn junction and that of the diode-connected transistor of Problem 3.36. How does the performance of this circuit as a rectifier change with W and L?

FIGURE P3.36 Diodes for Problem 3.36.

FIGURE P3.37 Circuit for Problem 3.37.

FIGURE P3.38

Circuit for Problem 3.38.

## Section 3.3

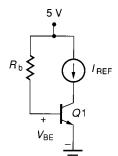

- **3.38.** Using Fig. P3.38, obtain  $V_0$  to within  $\pm 1\%$  if (a)  $V_{BB} = 12$  V and (b)  $V_{BB} = 0.9$  V. Assume the BJT is characterized by the parameters of Table 3.3-1 and modeled by the Ebers-Moll Eqs. 3.3-1 and 3.3-2.

- **3.39.** Determine the maximum error, in percentage, that results from using (3.3-10) and (3.3-11) instead of the more complicated Ebers-Moll equations of (3.3-1) and (3.3-2) in the region  $V_{\rm BE} > 0.5$  V,  $V_{\rm BC} < 0.3$  V. Assume the BJT is at room temperature and characterized by the parameters of Table 3.3-1.

- **3.40.** Calculate the power that would be dissipated in a BJT if  $A_{\rm E}=4~{\rm mil}^2$  and the device is operating with (a)  $V_{\rm BE}=0.6~{\rm V}$  and  $V_{\rm BC}=-5~{\rm V}$ , and (b)  $V_{\rm BE}=1.6~{\rm V}$  and  $V_{\rm BC}=-5~{\rm V}$ . Assume the BJT is characterized by the process parameters of Table 3.3-1.

- **3.41.** Plot the transconductance gain,  $g_{\rm m}$ , versus bias current (collector or drain) for a MOSFET with  $W=L=10~\mu$  and a BJT with  $A_{\rm E}=100~\mu^2$ . Use the typical process parameters of Tables 3.1-2 and 3.3-1.

- **3.42.** Rewrite the Ebers-Moll equations of (3.3-1) and (3.3-2) using  $V_{\text{BE}}$  and  $V_{\text{CE}}$  as the independent variables in terms of the parameters  $I_{\text{S}}$ ,  $\beta_{\text{F}}$ ,  $\beta_{\text{R}}$ , and  $V_{\text{T}}$ .

- **3.43.** At high frequencies, a small signal gate current flows into the gate of the MOSFET. Compare the unity small signal-short circuit current gain frequency (of  $A_{\rm I} = i_0/i_1$ )

FIGURE P3.43 Circuit for Problem 3.43.

FIGURE P3.44 Circuit for Problem 3.44.

for the MOSFET to that of the BJT (see Fig. P3.43). Assume both devices are in their high-gain operating region, are of minimum size, are biased at  $I_{\rm OQ}=200\,\mu{\rm A}$ , and are characterized by the process of Tables 2A and 2C of the Appendices of Chapter 2. Assume R is large.

- **3.44.** (a) For the circuit shown in Fig. P3.44, bias the circuit (determine  $R_b$ ) so that  $V_{\rm OQ} = 2$  V when  $R_c = 500~\Omega$ . Determine the small signal voltage gain  $A_{\rm v} = v_{\rm o}/v_{\rm i}$  if it is assumed C is large. Use the typical process parameters of Table 3.3-1.

- (b) Repeat part (a) if the parasitic emitter resistance is  $R_{\rm E}=2~\Omega$ . Compare the results with those obtained in (a).

- (c) Repeat parts (a) and (b) if  $R_C = 10 \text{ k}\Omega$  and  $V_{OQ} = 6 \text{ V}$  and compare with the results obtained in parts (a) and (b).

- **3.45.** Assume the BJT of Fig. P3.45 is biased with  $R_b$  so that Q1 operates in the forward active region. What will be the tolerance in the value of  $V_{\rm BE}$  due to processing? What will be the wafer-level tolerance in the value of  $V_{\rm BE}$  due to wafer-level parameter variations? Assume the BJT process in which Q1 is fabricated is characterized by Table 2C.4 of Appendix 2C and that wafer-level variations (matching) are characterized by footnote 1 of that table.

- **3.46.** The depletion region capacitance of the BE junction of an npn transistor with a rectangular emitter that is 0.3 mil  $\times$  6 mil is 0.63 pF at zero volts reverse bias. A circular transistor of the same test bar has the same emitter area. What is the depletion region capacitance of this device for a 6 V reverse bias at room temperature if the built-in potential,  $\phi_B$ , is 0.70 V?

- **3.47.** For the transistor shown in Fig. P3.47,  $I_s = 2 \times 10^{-15}$  A and the emitter area is 1.5 mil<sup>2</sup>. With V = 1 V, the current I is 52  $\mu$ A, and with V = 21 V, I is 56  $\mu$ A.

- (a) Determine  $V_{AF}$ .

- (b) Determine  $\beta_F$ .

- (c) Determine  $V_{\rm BE}$  at room temperature (300 °K).

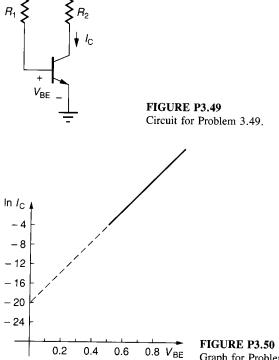

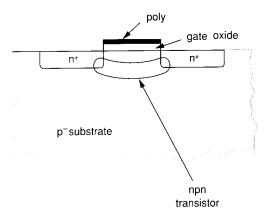

- **3.48.** If we plot  $\ln I_{\rm C}$  (vertical) versus  $V_{\rm BE}$  (horizontal) for a bipolar transistor operating

FIGURE P3.45 Circuit for Problem 3.45.

FIGURE P3.47 Transistor for Problem 3.47.

in the forward-active region, how can the area of the emitter be determined from the plot? What can be determined from the slope? Neglect Early voltage effects.

- 3.49. For the circuit shown in Fig. P3.49, assume the collector current is 10 mA, the emitter is a square with sides of 1 mil, the base is a square with sides of 3 mil, and the collector area is defined by a square with sides of 6 mil. For the following, assume that no changes are made in the circuit schematic.

- (a) What will be the collector current if the sides of the base are increased to 4 mil?

- (b) What will be the collector current if the emitter sides are decreased to 0.5 mil?

- (c) What will be the collector current if the collector sides are increased to 7 mil?

- **3.50.** A plot of  $\ln I_{\rm C}$  versus  $V_{\rm BE}$  for a BJT transistor, with emitter area 4 mil<sup>2</sup>, and a base area of 10 mil<sup>2</sup>, operating in the forward active region is shown by the solid line in Fig. P3.50. Determine as many of the following model parameters as possible:  $J_{\rm S}$ , T,  $V_{\rm T}$ ,  $\beta_{\rm F}$ ,  $\beta_{\rm R}$ ,  $\alpha_{\rm F}$ .

0.6

• 12 V

FIGURE P3.50 Graph for Problem 3.50.

FIGURE P3.51 NMOS structure for Problem 3.51.