# PROTOTYPE IMPLEMENTATION OF A WWW BASED ANALOG CIRCUIT DESIGN TOOL

M. E. Schlarmann, R. L. Geiger

Iowa State University 348 Durham Center Ames, Iowa 50011, USA

# ABSTRACT

A new CAD tool used for the interactive exploration of a design space has been developed. The interactive nature of the tool facilitates the acquisition of designer knowledge which may accelerate the development of improved circuit topologies in the future. The tool's cross-platform compatibility and network centric architecture prevents reinvention and facilitates organization-wide or worldwide communication via *design knowledge repositories*.

To demonstrate its utility in the area of analog circuit design, the tool was used to model the design tradeoffs available during the design of a telescopic cascode amplifier. There was good agreement between the response predicted by the new tool and a full SPICE simulation.

## **1. INTRODUCTION**

Many attempts to automate the analog circuit design process have chosen to eliminate humans from the design process altogether [1][2][3][4][7][8]. In most cases, the designer defines the required specifications up front and the design automation tool completes the entire design process with little or no human intervention.

As a side effect, the use of a complete design automation tool does not substantially contribute to the designer's understanding of the relationships among the performance parameters and the design parameters. This is problematic because coming up with improved circuit designs and circuit topologies is a creative process that draws upon a designer's experience and understanding. The use of automated procedures may actually impede the development of improved circuit topologies because the non-interactive nature of an automated approach results in slower assimilation of designer knowledge [5].

Although substantive progress is being made in the areas of qualitative and fuzzy reasoning [6], evolutionary algorithms [7], and expert systems [8], practical systems that synthesize new analog circuits have not yet emerged. Thus, to maximize the rate of progress toward new topologies humans still need to be involved in the design process.

Rather than eliminating humans from the design process altogether, more practical benefit may be derived by implementing small, easily used, interactive design tools that facilitate human interaction and acquisition of knowledge. Instead of completing the entire design task, these tools perform smaller sub-tasks. They make the designer's job easier but the designer still guides the overall design process Except in the most trivial of cases, analog circuit design problems are knowledge-intensive, complex, multi-dimensional problems. In many cases, it is not possible to derive tractable analytical relationships for the parameters used to characterize the performance of the circuit. In these cases, it is not clear by inspection how changing one circuit degree of freedom will affect the performance parameter of interest.

For example, an engineer designing a multistage amplifier may be able to derive the analytical expression for the gain-bandwidth product but the relationship may be too complicated to clearly understand how the gain-bandwidth relates to the circuit's degrees of freedom. The mathematical expressions for the performance parameters are often too complicated to be tractable. In those cases, it is not clear how changing one circuit degree of freedom will affect the performance parameter of interest.

Under these conditions, performance optimization is very difficult. Due to the complexity of the problem, designers are forced to make approximations that result in sub-optimal solutions. They are confident that better solutions exist but it is not clear by inspection of the analytical expressions how to find these solutions.

In these situations, the designer can gain valuable insight to help guide him/her to improved solutions by using an equations-based approach to interactively explore the design space and observe the relationships between the performance parameters and the circuit's degrees of freedom. To do this effectively requires a great deal of effort because each performance parameter has to be recomputed every time a degree of freedom is modified. Doing this task by hand can be overwhelming, even for small circuits.

To address this problem, a prototype CAD tool that makes the task of design space exploration easier has been developed. It allows designers to rapidly deepen their understanding of a design by interactively exploring a design space and observing the corresponding effects on and the relationships between the performance parameters. The additional insight into design performance gained by manual exploration of the design space will aid the designer in creating improved design topologies in the future. A preliminary discussion of the tool was provided in [9]. This work reviews the operation of the tool and describes how it was used to explore the design tradeoffs made during the design of a telescopic cascode amplifier.

### 2. The Prototype Application

The new tool can be used in the traditional desktop-centric manner by downloading the media and executing it stand-alone

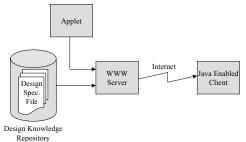

in a compliant Java Virtual Machine. Alternatively, it can be executed as an applet in a Java compatible WWW browser via a network connection. Figure 1 illustrates the network-centric operation of the proposed system. The executable, in the form of a Java applet, is transmitted to a Java capable web browser via a network connection. The applet runs on the client end within the WWW browser. A collection of design specification files is maintained in a repository on the server side. Each design specification file in the repository embodies the design knowledge available for a specific circuit topology that, at the request of a client, can be downloaded and used to program the applet.

Figure 1 Block diagram illustrating the network-centric operation of the proposed system

Operation of the tool in the network-centric fashion results in several notable advantages:

- Facilitates organization-wide (or worldwide) accumulation, sharing, and archiving of design knowledge by making well-documented design specification files available in a *Design Knowledge Repository*. Due to the fact that users can search the repository for circuit topologies that have already been characterized, the use of one centralized knowledge repository prevents duplication of work already performed.

- The tool is available for use anytime, from any networked location, worldwide.

- Other than a Java capable web browser, no special application software is required.

- Cross-platform compatibility is assured by the use of Java. This is especially beneficial for large enterprises with multiple platforms because it helps facilitate communication of design knowledge between disparate groups.

- Since the computation occurs on the client-end, the system is scalable to support virtually any number of clients.

- Lower administration costs. Once the required Java capable browser is installed, users do not need to spend time acquiring, installing and updating software on their machine(s). Since the most recent software version resides in one place on the server, revision maintenance becomes trivial.

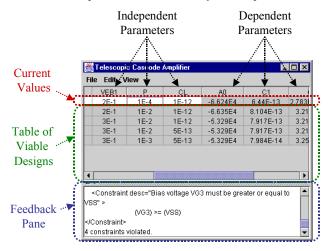

Figure 2 shows a screen snapshot of the application's main window. It contains a table in which the columns each correspond to different design parameters. Parameters that do not depend on other parameters are termed *independent* parameters while those that depend on others are termed

*dependent parameters.* The first row in the table is a special row that is referred to as the *current-values row*. This is the only place where the user is allowed to enter or edit data. The cells in the current-values row that have a light background color are modifiable while those that have dark backgrounds are computed and cannot be modified. The remainder of the table is called the *table of viable designs*. The significance of the table of viable designs will be described later. The bottom of the main window contains a pane used to provide informational and error messages to the user. This pane is referred to as the *feedback pane*.

Figure 2 Annotated screen snapshot

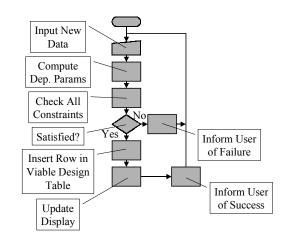

Figure 3 shows a simplified flowchart of the operation of the tool. Most of the time the application waits for new input data. When the user enters new data, the tool recomputes all of the dependent parameters and then checks all the constraints on the solution. If any of the constraints are violated, an error message is generated and fed back to the user via the feedback pane. However, if none of the constraints were violated, the design is viable and an entry corresponding to the new design is added to the table of viable designs. Upon successful completion of the addition an informational message is generated and displayed in the feedback pane.

Figure 3 Simplified operational flowchart

The table of viable designs grows as the user creates new designs that satisfy all of the constraints. In this way, the application automatically maintains a running history of viable designs that have been encountered. The user can easily recall any of these archived designs for additional consideration by simply clicking on the design of to recall. The use of the tabular form facilitates rapid comparisons and trend spotting.

Productivity is enhanced by allowing the user to control parameter visibility and display order. This feature allows the user to focus only on the parameters of interest, shielding them from unnecessary complexity. Additionally, the user is given the ability to reorder the rows of the table based upon a column-wise sorting criterion. This allows the user to quickly rank the viable designs based upon the parameters of interest. Plotting capabilities have also been integrated into the tool. This feature allows the users to plot how a parameter varies as another parameter is swept over a finite interval. Amplifier designers, for example, may use this feature to plot open and closed-loop frequency and phase responses as well as other relationships of interest.

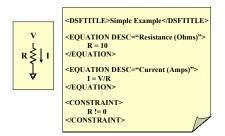

The tool is extendible to new circuit topologies by writing custom design specification files for the new topologies. Design specification files are plain-text files written in a simple XMLlike language.

The design specification file is simply a list of *elements* that are delimited by *tags*. The tags mark the beginning and end of each element. Differing types of elements represent the variety of different components that may be present in an input file. For example, one element represents a design equation, another type represents a constraint. There are other elements used to represent bibliographical information such as the authors' names, the title, the creation date, etc. To illustrate, Figure 4 contains a simple example of a design specification file used to model the current through a resistor as a voltage is applied across it. Full documentation of the input language is contained in the Design Space Explorer Users Manual.

Figure 4 Simple design specification file for a voltage applied across a resistor

# 3. TELESCOPIC CASCODE AMPLIFIER DESIGN

As a demonstration of the tool's utility, it was used to explore the tradeoffs made during the design of a telescopic cascode amplifier.

To avoid unnecessary complexity, reduce the potential for error, and speed up calculations, it is desirable that the design specification file be no more complicated than is needed to adequately model the response of the system. Therefore, simplified system models are used during design space exploration. After interactively using the tool to explore tradeoffs, designers verify and refine the resultant circuits using more accurate models in Spice.

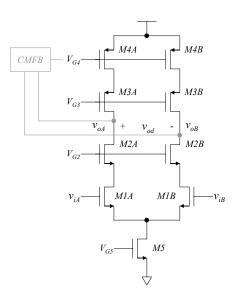

A design specification file was written for the circuit topology shown in Figure 5. Second-order effects such as mobility degradation, non-uniform doping profiles, velocity saturation, etc. were neglected. However, channel length modulation and the body effect were modeled. Assumptions regarding the layout of the devices were made based on process design rules and were used to estimate the circuit parasitics. Interconnect related capacitances were not modeled. The design was targeted for implementation in a  $0.18\mu$  CMOS process.

Figure 5 Schematic diagram of the telescopic cascode amplifier

After interactively using the tool to explore the design tradeoffs, a suitable design was chosen from the viable candidates that were found. Table 1 lists the design parameters of the chosen design.

Table 1 Amplifier Design Parameters

| W <sub>1A,B</sub> | 4.73μ  | All L's               | 1μ     |

|-------------------|--------|-----------------------|--------|

| W <sub>2A,B</sub> | 15.6µ  | VDD                   | 3.3V   |

| W <sub>3A,B</sub> | 49.8µ  | VSS                   | 0.0V   |

| W <sub>4A,B</sub> | 14.99µ | C <sub>L(diff.)</sub> | 0.25pF |

| W <sub>5A,B</sub> | 9.45µ  | Р                     | 1mW    |

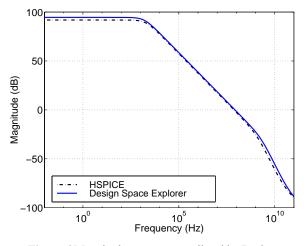

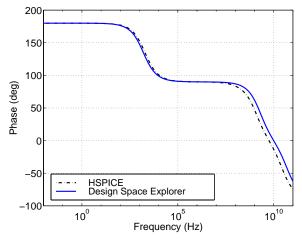

To verify that the design specification file adequately models the response the amplifier, the resultant circuit was simulated using HSPICE with Level 49 (BSIM3) Models. Figure 6 and Figure 7 contain the HSPICE and Design Space Explorer predicted magnitude and phase responses respectively. Notice that there is a reasonable level of agreement between the models. Slight discrepancies in the DC gain and the locations of the parasitic poles are apparent. This is most likely caused by inaccuracies in the modeling of the MOSFET channel conductance.

Figure 6 Magnitude responses predicted by Design Space Explorer and HSPICE

Figure 7 Phase responses predicted by Design Space Explorer and HSPICE

#### 4. SUMMARY

Design automation tools that eliminate human interaction altogether may impede the acquisition of designer knowledge and thus delay or stall the development of improved circuit topologies. Rather than removing all designer interaction, more practical benefit might be derived from the use of CAD tools that facilitate the acquisition of knowledge. Rather than replacing the designer altogether, these tools require the designer to guide the overall process but they would make their jobs easier To address these problems, a prototype network-centric circuit design tool and design knowledge repository has been developed. It allows a designer to interactively explore a circuit design space of pre-characterized circuit topologies using a convenient graphical user interface. Any user can extend the system to include new or custom circuit topologies by writing their own design specification files.

To demonstrate its utility in the area of analog circuit design, the tool was used to model the design tradeoffs available during the design of a telescopic cascode amplifier. There was good agreement between the response predicted by the new tool and a full SPICE simulation.

### ACKNOWLEDGMENT

Support for this project has been provided in part by Texas Instruments Inc., RocketChips Inc., and the R. J. Carver Charitable Trust.

### REFERENCES

- H. Y. Koh, C. H. Sequin, and P. R. Gray, "OPASYN: A Compiler for CMOS Operational Amplifiers," *IEEE Trans. Computer-Aided Design*, Vol. 9, No. 2, pp. 113-125, 1990

- [2] F. Medeiro, B. Perez-Verdu, A. Rodriguez-Vazquez, and J. L. Huertas, "A Vertically Integrated Tool for Automated Design of ΣΔ Modulators," *IEEE J. Solid-State Circuits*, Vol. 30, No. 7, pp. 762-772, Jul. 1995

- [3] H. Onodera, H. Kanbara, and K. Tamaru, "Operational-Amplifier Compilation with Performance Optimization," *IEEE J. Solid-State Circuits*, Vol. 25, No. 2, pp. 466-473, Apr. 1990

- [4] R. Phelps, M. Krasnicki, R. A. Rutenbar, R. Carley, and J. R. Hellums, "Anaconda: Simulation-Based Synthesis of Analog Circuits Via Stochastic Pattern Search," *IEEE Trans. Computer-Aided Design*, Vol. 19, No. 6, pp. 703-717, Jun. 2000

- [5] K. Swing, G. Gielen, and W. Sansen, "An Intelligent Analog IC Design System Based on Manipulation of Design Equations," *Proc. of 1990 IEEE CICC*, pp. 8.6.1-8.6.4

- [6] A. Torralba, J. Chavez, and L. G. Franquelo, "FASY: A Fuzzy-Logic Based Tool for Analog Synthesis," *IEEE Trans. Computer-Aided Design*, Vol. 15, No. 7, pp. 705-715, Jul. 1996

- [7] J. R. Koza, F. H. Bennet III, D. Andre, M. A. Keane, and F. Dunlap, "Automated Synthesis of Analog Electrical Circuits by Means of Genetic Programming," *IEEE Trans. Evolutionary Computation, Vol. 1, No. 2, pp. 109-128, Jul. 1997*

- [8] V. R. Babu, B. Mazhari, and M. M. Hasan, "An Expert System Approach to Analog Circuit Synthesis," *Proc. International Conference on VLSI Design*, pp. 425-428, Jan. 1997

- [9] M. E. Schlarmann and R. L. Geiger, "Preliminary discussion of a world-wide-web based analog circuit design tool and design knowledge repository," in Proc. Third International Workshop on Design of Mixed-Mode Integrated Circuits and Applications, Puerto Vallarta, Mexico, July 26-28, 1999, pp. 61-64