# Wire Retiming Problem with Net Topology Optimization

Dennis K.Y. Tong, Evangeline F.Y. Young, Chris Chu and Sampath Dechu

Abstract-In this paper, we study the retiming problem of sequential circuits with net topology optimization. Both interconnect and gate delay are considered in retiming. Most previous retiming algorithms have assumed ideal conditions for the nonlogical portions of data paths, which are not sufficiently accurate to be used in high performance circuits today. In our modeling, we assume that the delay of a wire is directly proportional to its length. This assumption is reasonable since the quadratic component of a wire delay is significantly smaller than its linear component when the more accurate Elmore delay model is used. A simple experiment was conducted to illustrate the validity of this assumption. We present two approaches to solve the retiming problem, both of which have polynomial time complexity. The first one can compute the optimal clock period while the second one is an improvement over the first one in terms of practical applicability. The second approach gives solutions very close to the optimal (0.06% more than the optimal on average) but in a much shorter runtime.

The optimally retimed circuit will then be realized physically by placing the registers and finding the net topologies. In contrast to many previous works [1], [2] that performed simple calculations to determine the register positions, our approach can preserve the optimal clock period obtained by the retiming step and utilize as few registers as possible. Minimization of register number saves both area and power in register and clock loading. Our topology optimization step is shown to be optimal for nets with four or fewer pins and this type of nets constitutes over 90% of the nets in a sequential circuit on average.

Using the ISCAS89 benchmark, we tested our algorithm with a  $0.35\mu m$  CMOS standard cell library. Silicon Ensemble was used to layout the design with row utilization of 50%. Experimental results showed that our algorithm could find the best sharing of registers for a net in most of the cases, i.e., using the minimum number of registers while preserving the target clock period obtained by the retiming step, within a minute run on an Intel Pentium IV 1.5GHz PC with 512MB RAM.

## I. INTRODUCTION

Retiming [3] is a useful and popular technique for performance optimization of sequential circuits. It relocates registers to reduce cycle time while preserving the functionalities of circuits. Much effort has been made to apply this technique in different areas like power reduction [4], [5], testability [6],

Dennis K.Y. Tong and Evangeline F.Y. Young are with the Department of Computer Science and Engineering, Chinese University of Hong Kong, Shatin, N.T., Hong Kong e-mail: fyyoung@cse.cuhk.edu.hk.

Chris Chu is with the Department of Electrical and Computer Engineering, Iowa State University, Ames, IA 50011-3060 USA e-mail: cnchu@iastate.edu. Sampath Dechu is with the Blaze-dfm, Inc., Sunnyvale CA USA e-mail: sampath@blaze-dfm.com.

This work was supported by the Direct Grant for Research of the Chinese University of Hong Kong, under Projects 2050321 and 2050352.

Copyright (c) 2006 IEEE. Personal use of this material is permitted. However, permission to use this material for any other purposes must be obtained from the IEEE by sending an email to pubs-permissions@ieee.org.

[7], logic resynthesis [8], circuit partitioning [9]–[11] and physical planning [12]. Some extended its applicability to large practical circuits efficiently [13]–[20]. However, most retiming algorithms have assumed ideal conditions for the non-logical portions of data paths, specifically ignoring interconnect delay. As process technology gets down to deep sub-micron, interconnect delay becomes a major factor of path delay. Without including this delay component, existing retiming algorithms are not sufficiently accurate to be used in practical high performance circuits today. Besides, it's very important to be able to realize a retimed circuit physically to achieve the optimal clock period obtained by the retiming step. In this paper, we study the problem of retiming with both interconnect and gate delay, and proposed a scheme to realize an optimally retimed circuit physically to achieve the target clock period.

1

The choice of an accurate interconnect delay model is important. In the papers [21], [22], interconnect delay was incorporated into the retiming process, but simplified assumptions were made such that the interconnect delay between adjacent registers on the same wire was neglected. Another approach to integrate retiming into detailed placement was presented in [1]. After an initial place and route, heuristics were used to estimate interconnect delay. Retiming and postretiming placement were then performed to optimize the circuit performance. A recent paper [23] by Tabbara et al. applied retiming in the DSM domain and interconnect delay was considered. It was done by having a lower bound on the number of registers on each wire  $e_{uv}$ , while the delay at nodes were irrelevant. Registers could be retimed into a node that represented a component and affected the total area of the components. Retiming was performed to satisfy the constraint on the number of registers on each wire while minimizing the total area of the components. In the paper [15], a clock skew solution corresponding to an optimal clock period was converted into a retiming solution which was guaranteed to be at most one gate delay larger than the optimal clock period. However, their current approach to perform this conversion considered only gate delay. Lin et al. [24]–[26] have considered the retiming problem with linear interconnect delay model, but they have formulated the problem differently on chip level with macroblocks, etc.

In our model, the delay of a wire is assumed to be directly proportional to its length. When a wire is short, the

<sup>1</sup>Please note that the retiming result in section III can also be applied to other delay models since the result is independent of how the interconnect delay  $d_{ij}$  between two gates i and j changes with the length of the wire from i to j.

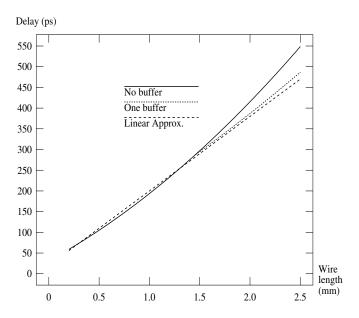

quadratic component of the wire delay is significantly smaller than its linear component. For a long wire, buffer insertion can be performed to break the wire into short segments. A simple experiment was conducted to illustrate the validity of this assumption and the result was shown in fig. 1. In this experiment, the Elmore delay model was used and the parameters were based on the  $0.07\mu m$  technology. This graph shows the relationship between wire delay (*y*-axis) and wire length (*x*-axis). If the wire is shorter than 1.46 mm, the error of using a linear approximation is at most 5.48%. If the wire is longer than 1.46 mm, the delay can be reduced by inserting a buffer and the error resulted is even less.

We present two retiming approaches in this paper both of which have polynomial time complexity. The first one is extended from the MILP approach in the paper [3] to consider both gate and wire delay and can solve the retiming problem optimally, i.e., relocating the registers in a circuit to give the smallest possible clock period. The second one transforms the problem into a single-source longest path problem and then applies a technique to reduce the size of the graph for the longest path computation. It is an improvement over the first one in terms of practical applicability. It gives solutions very close to the optimal (0.06% more than the optimal on average) but in a much shorter runtime.

After a circuit is retimed, we need to realize it physically. A net is represented as a branch of edges in a retiming graph model which does not bear any information about the net topology and register positions. It is unknown whether the clock period obtained by retiming can be realized in the design. Being able to obtain the net topologies and place the registers to preserve the target clock period is important, or it will make the retiming optimization meaningless. Minimizing the number of registers used is also essential as the size of a register is usually several times larger than that of a simple gate, regardless of the process technology being used. There are several previous works on post-retiming register placement, but many of them suffer from the problem of oversimplification when wire delay dominates. For example, in [1], the authors assume that a register is located at the geometric center of the connected gates. A similar problem occurs in [2] in which the authors determine the position of a register in such a way that the sum of the net lengths connected to that register is minimized.

We devised a scheme to realize a retiming solution physically to achieve a target clock period, given the gate positions. This problem involves two main sub-problems, namely, topology finding and register placement. As we have mentioned before, a net is modeled as a branch of edges in the retiming graph, topology finding refers to the problem of finding an optimal sharing of registers among the fanout edges of a net given the geometric positions of the connected gates. After topology finding, we need to compute an appropriate position for each register given the constraints in placement (some occupied areas do not allow register insertion) and this problem is known as register placement. Given a circuit with its placement (we used standard cell design in our experiments), retiming is first performed on the circuit to obtain the optimal clock period, then topology finding and register

Fig. 1. A simple experiment to illustrate the relationship between wire delay and wire length.

placement will be performed to realize the retimed solution physically. Our approach can find the optimal topology, i.e., using the minimum number of registers while preserving the clock period, for four or fewer pin nets. Since nets with four or fewer pins constitute, on average, over 90% of the nets in a circuit, our proposed algorithm offered an agreeable performance in the experiments. Nearly all the nets had their best topologies found and registers were inserted successfully to achieve the target clock period.

The remainder of this paper is organized as follows. We present the problem statement in Section II. The optimal and fast approach for the retiming problem are presented in Section III-A and Section III-B, respectively. The topology finding and register placement step are discussed in Section IV-A and Section IV-B, respectively. Experimental results are shown in Section V. A conclusion follows in Section VI.

# II. PROBLEM FORMULATION

Given a sequential circuit C and its placment  $\mathcal{D}$ , we want to retime C to obtain the optimal clock period and implement this retimed solution in  $\mathcal{D}$  by inserting registers into  $\mathcal{D}$  and finding the connection topologies between the gates/registers. This problem can be divided into two parts: retiming and topology optimization. We will describe these two sub-problems in details in the following sections.

#### III. RETIMING WITH INTERCONNECT AND GATE DELAY

A sequential circuit C can be represented by a directed graph G(V,E), where each node v corresponds to a combinational gate, and each directed edge  $e_{uv}$  represents a connection from the output of gate u to the input of gate v, through zero or more registers. Without loss of generality, we assume that G is strongly connected. If not, we can add a source node s and connect it to all primary inputs, add a target node t and

Fig. 2. An example to illustrate the meaning of a(v).

connect all primary outputs to it, and connect t to s. Then the resulting graph is strongly connected. If we set the delay of s, t and all the added edges to zero, and set the number of registers on  $e_{ts}$  to one and that on the other added edges to zero, a retiming solution of the modified graph will also be a valid retiming solution of the original graph as long as  $e_{ts}$  still has one register. Let  $w_{uv}$  be the number of registers on edge  $e_{uv}$ . Let  $d_{uv}$  be the interconnect delay of edge  $e_{uv}$  if all the registers are removed. Note that the delay of an interconnect segment is assumed to be proportional to the length of the segment. Let  $d_u$  be the gate delay of node u.

Traditionally, interconnect delay is ignored during retiming. A retiming solution can be viewed as a labeling of the nodes  $r: V \to Z$ , where Z is the set of integers [3]. The retiming label r(v) for a node v represents the number of registers moved from its outputs toward its inputs. After retiming, the number of registers  $\hat{w}_{uv}$  on an edge  $e_{uv}$  is given by  $\hat{w}_{uv} = r(v) + w_{uv} - v$ r(u).

As interconnect delay is dominating in the VDSM technology, the exact position of each register will affect the clock period. A retiming solution should specify both the retiming label r(v) for each node v and the exact positions of the  $\hat{w}_{uv}$ registers on each edge  $e_{uv}$ . Retiming should be formulated as a problem of determining a feasible retiming solution, i.e., a retiming solution in which the number of registers  $\hat{w}_{uv}$  on each edge  $e_{uv}$  is non-negative, such that the clock period of the retimed circuit is minimized. In the following, we show how to check whether a particular clock period T can be achieved by a feasible retiming solution. The minimum achievable clock period  $T_{opt}$  can then be found by binary search.

# A. An Exact Approach

This approach is extended from the mixed integer linear programming (MILP) approach in [3]. In the original formulation, only gate delay is considered and there is thus no differences between having one or more than one registers on a wire. Their technique can be extended to solve the problem with both gate and interconnect delay optimally by modifying some of the constraint formulation. In order to formulate the problem as an MILP, for each gate v, we need to define a term a(v) that represents the maximum arrival time at the output of gate v. An example to illustrate this definition is shown in fig. 2. We can then formulate the problem as the following MILP:

$$d_v \le a(v) \quad \forall v \in V \quad (1)$$

$$a(v) \le T \quad \forall v \in V \quad (2)$$

$$r(v) + w_{uv} - r(u) \ge 0 \quad \forall e_{uv} \in E$$

(3)

3

$$a(v) \ge a(u) + d_{uv} + d_v - T(r(v) + w_{uv} - r(u)) \quad \forall e_{uv} \in E$$

(4)

where T is the clock period that we want to check whether it is achievable. Since a(v) is the longest delay to the output of gate v from a register connected directly to an input of v, this delay must be at least the delay of gate v, so  $d_v \le$ a(v) as stated in (1). Besides, this delay cannot exceed the clock period T as required in (2). Constraint (3) is needed for a feasible retiming solution. Constraint (4) is to ensure that enough registers are on each edge  $e_{uv}$  to achieve a clock cycle T. As the largest possible delay between two adjacent registers is T, the right-hand side of constraint (4) is reduced by T for each register on edge  $e_{uv}$ . Note that this constraint also captures the scenario when there is no registers on edge  $e_{uv}$ . In that case, the arrival time at node u contributes directly to the arrival time at node v. In [3], wire delay is not considered, so we only need to differentiate the cases when a wire has zero or non-zero registers on it. Therefore, the inequality (4) is written as  $a(v) \ge a(u) + d(v)$  whenever  $e_{uv} \in E$  and r(u) $r(v) = w(e_{uv})$ , i.e., whenever an edge  $e_{uv} \in E$  has no registers on it.

By introducing a variable R(v) at each node v that is defined as a(v)/T + r(v), the above set of constraints (1)–(4) can be rewritten as a set of difference constraints as follows:

$$R(v) - r(v) \ge \frac{d_v}{T} \qquad \forall v \in V$$

$$R(v) - r(v) \le 1 \qquad \forall v \in V$$

(6)

$$R(v) - r(v) \le 1 \quad \forall v \in V$$

(6)

$$r(u) - r(v) \le w_{uv} \quad \forall e_{uv} \in E \tag{7}$$

$$R(v) - R(u) \ge \frac{d_{uv}}{T} + \frac{d_v}{T} - w_{uv} \quad \forall e_{uv} \in E$$

(8)

Notice that (5)-(8) is a set of difference constraints involving both integer and real variables. There are |V| real variables R(v), |V| integer variables r(v), and 2|V|+2|E| constraints. This can be solved in polynomial time of O(|V||E| + $|V|^2 \lg |V|$  if Fibonacci heap is used as the data structure [27].

If the above set of constraints is solvable, the values of r(v)and a(v) for all  $v \in V$  are known. We can then find the exact position of each register on a wire one by one as follows. For each edge  $e_{uv}$ , if there are registers retimed on it, i.e.,  $r(v) + w_{uv} - r(u) > 0$ , the first register on this edge will be placed at a distance of delay T - a(u) from the output of gate u. Other registers are then placed as far from each other as possible, i.e., at a distance of delay T from the previous one, until reaching the gate v. All the remaining registers on this edge are then placed right before v.

## B. A Fast Approximate Approach

In this approach, we first replace each gate by a wire of the same delay and then solve the problem with only interconnect delay optimally and efficiently. Those registers retimed "into" a gate are moved either to the input or the output wires of the gate. The exact positions of the registers on the wires are then determined by a linear program to minimize the clock period. The solution obtained by this approach is very close to the optimal on average as shown by the experimental results. In the following, we first show how the retiming problem with interconnect delay only can be solved optimally. Then we describe in details how gate delay can be handled simultaneously.

1) Retiming with Interconnect Delay Only: In this subsection, we assume that  $d_v = 0$  for all  $v \in V$ . This problem with zero gate delay is the same as the maximum cycle ratio problem, which has been studied in many previous works [28]–[31] before. We first show that the clock period feasibility problem can be reduced to a single-source longest paths problem. We then present a fast algorithm to solve the longest paths problem. We solve the set of constraints (5)–(8) with the help of the following lemma.

Lemma 1: Assume that  $d_v = 0$ . Given R(v) for all  $v \in V$  satisfying constraint (8), we can obtain a solution to constraints (5)–(8) by setting r(v) = |R(v)| for all  $v \in V$ .

*Proof:* It is clear that  $0 \le R(v) - \lfloor R(v) \rfloor < 1$  for all  $v \in V$ . Therefore, (5) and (6) are satisfied. For any  $e_{uv} \in E$ ,

$$\begin{array}{lll} r(u)-r(v) & \leq & R(u)-r(v) & \text{as } r(u) \leq R(u) \\ & \leq & (\frac{d_{uv}}{T}+R(u))-r(v) & \text{as } \frac{d_{uv}}{T}>0 \\ & \leq & (w_{uv}+R(v))-r(v) & \text{by constraint (8)} \\ & < & w_{uv}+1 & \text{as } R(v)-r(v)<1 \end{array}$$

As r(u) - r(v) is an integer, it must be less than or equal to  $w_{uv}$ . Hence, constraint (7) is also satisfied.

Lemma 1 implies that we can first solve constraint (8) to find R(v) and it is then easy to find r(v) to satisfy the other three constraints. Notice that if  $d_v \neq 0$  for some  $v \in V$ , Lemma 1 does not hold as constraint (5) is not satisfied. This technique is similar to that used in [30] to find an approximately optimal retiming in a non-unit-delay circuitry with gate delay only. The problem of finding R(v) for all  $v \in V$  to satisfy constraint (8) can be viewed as a single-source longest paths problem on G with length  $l_{uv}$  equals  $d_{uv}/T - w_{uv}$  for each  $e_{uv} \in E$ . As G is strongly connected, we can pick an arbitrary node as the source node s. Note that edge lengths can be positive. If G has a positive cycle, the set of constraints has no solutions. It means that the clock period T is infeasible.

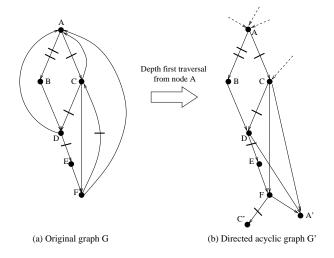

The single-source longest paths problem in Section III-B1 can be solved by the Bellman-Ford algorithm [32] and the time complexity is O(|V||E|). This algorithm may still be slow in practice. An interesting idea of using small feedbacks to speed up the Bellman-Ford algorithm is found in [33] with time complexity  $O(|E||E^-|)$  where  $E^-$  is the set of edges in G with negative weights. In this section, we present a singlesource longest paths algorithm which is faster in practice. The basic idea is to reduce the size of G by compacting some paths into edges before the Bellman-Ford algorithm is applied. The details are given below. We first transform the graph G(V, E)into a directed acyclic graph (DAG) G'(V', E') by performing a depth-first traversal [32] starting from the source node s. The depth-first traversal defines a tree in G. Those non-tree edges running from a node u to an ancestor v of u are called back edges. If we point all incoming back edges of a node v to an extra node v', the resulting graph will be a DAG because every

Fig. 3. An example to illustrate the transformation to a DAG.

simple cycle in G involves at least one back edge. Formally, we use  $E_b$  to denote the set of back edges and  $V_b$  to denote the set of nodes with an incoming back edge. For each node v in  $V_b$ , we introduce an extra node v'. The back edge  $e_{uv}$  is removed from the graph and the edge  $e_{uv'}$  is added. The resulting DAG is G'(V',E') where  $V'=V\cup\{v'|v\in V_b\}$  and  $E'=(E-E_b)\cup\{e_{u,v'}|e_{u,v}\in E_b\}$ . We set the length  $l_{uv'}$  of the edge  $e_{uv'}$  to  $l_{uv}$ . To illustrate the transformation, consider the graph G in fig. 3(a) with source node A. Suppose the depth-first traversal visits the nodes in the order ACDEFB. Then  $E_b=\{e_{DA},e_{CA},e_{FC},e_{FA}\}$  and  $V_b=\{A,C\}$ . We introduce two extra nodes A' and A' and A' and replace the four edges A' and A' and A' and A' and replace the four edges A' and A' an

We then construct a graph H with node set  $V_b$ . The edge set  $E_H$  contains an edge  $e_{uv}$  for  $u, v \in V_b$  if there exists a path from u to v in G with either no back edge or one back edge at the end. The length of the edge  $e_{uv}$  in H ( $l_{uv}^H$ ) is the longest path distance among those paths. Note that the longest path distance from u to v in G with no back edge (respectively, with one back edge at the end of the path) equals the longest path distance from u to v (respectively, from u to v') in G'. Hence  $l_{uv}^H$  for all  $u, v \in V_b$  can be computed by solving  $|V_b|$  single-source longest paths problems in G' for different source nodes in  $V_b$ . As G' is a DAG, each single-source longest paths problem can be solved in linear time by visiting the nodes in topological order. The time complexity to construct H is therefore  $O(|V_b||E|)$ .

It is obvious that every path in H corresponds to at least one path in G of the same length. Therefore if H contains a positive cycle, G will also contain a positive cycle. On the other hand, if G contains a positive cycle, the cycle can be broken up into a set of paths  $p_1, p_2, \ldots, p_k$  such that both endpoints of each path  $p_i$  are in  $V_b$ . Notice that each path  $p_i$  corresponds to an edge in H of at least the same length. So H must also contain a positive cycle. Therefore we can solve the positive cycle detection problem on H instead of on G. If H has no positive cycles, R(v) for all  $v \in V_b$  can be found from H. R(v) for all  $v \in V - V_b$  can then be found in linear time by propagating

<sup>&</sup>lt;sup>2</sup>If the original circuit is not strongly connected, a source node s has already been added.

R(v) for all  $v \in V_h$  through G' in topological order.

The most time consuming steps are step 7 and step 8 inside the binary search loop. Step 7 can be done in  $O(|V_b||E|)$  time as discussed above. Step 8 can be done in  $O(|V_b||E_H|)$  time by the Bellman-Ford algorithm. As  $V_b$  contains much fewer nodes than V and  $E_H$  usually contains comparable or fewer edges than E, this technique is usually more efficient than applying the Bellman-Ford algorithm to G directly. The total time complexity is  $O(|V_b| \max\{|E|, |E_H|\} \lg \frac{K}{\epsilon T_{opt}})$ , where  $\epsilon$  is the error bound for the binary search, K is the difference between the upper and lower bounds of the clock period initially, and  $T_{opt}$  is the optimal clock period. Notice that the number of iterations in the binary search, i.e., the logarithmic term, can be reduced by finding the maximum delay-to-register ratio which is a lower bound to the minimum clock period [30].

## **Algorithm** *I-Retiming()*

/\* Retime a sequential circuit with interconnect delay only to \*/ /\* achieve the minimum possible clock cycle with an error \*/ /\* bound ε. \*/

Input: A sequential circuit C with interconnect delay only Output: An optimally retimed circuit of C

- 1. Build graph G(V,E) from C

- Build DAG G' by DFS(G)

- $C_{up}$  = a feasible clock,  $C_{low}$  = an infeasible clock

- 4. Do

- 5.  $T = (C_{up} + C_{low})/2$

- Update edge lengths of G' according to T

- 7. Build graph  $H(V_b, E_H)$  with

- $E_H = \{e_{uv} | u \in anc(v) \cup anc(v') \text{ in } G'\}$

- by finding single-source longest paths in G'

- If H does not have any positive cycle then 8.

- $C_{up} = T$

- 10. Else

- 11.  $C_{low} = T$ 12. while  $(C_{up} C_{low})/C_{up} > \varepsilon$ 13.  $T = C_{up}$  //  $C_{up}$  is always a feasible clock period

- 14. Compute R(v) and r(v) for each node  $v \in V$

- 15. Compute the exact position of each register on a wire

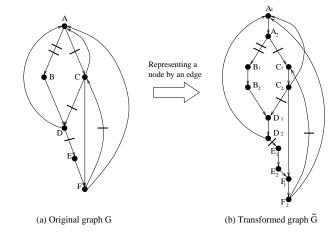

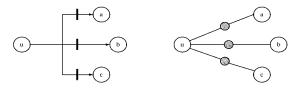

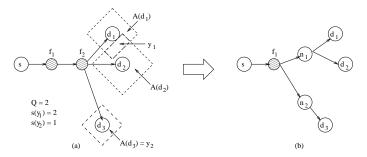

- 2) Retiming with Interconnect and Gate Delay: In this section, we discuss how to consider interconnect and gate delay simultaneously based on the above algorithm for interconnect delay only. To consider gate delay, we first represent a gate v with delay  $d_v$  by a wire  $e_{v_1v_2}$  with delay  $d_{v_1v_2} = d_v$ . This transformation for the circuit in fig. 3(a) is shown in fig. 4(b). We can then obtain an optimal retiming on this transformed circuit  $\tilde{G}$  using the algorithm in Section III-B1. However the retiming solution obtained on  $\tilde{G}$  may not be feasible for the original circuit G because some registers may be retimed into a wire that represents a gate. Therefore, we need to perform a post-processing step to get back a feasible retiming solution for G from the optimal retiming solution for  $\tilde{G}$ . This is done by linear programming.

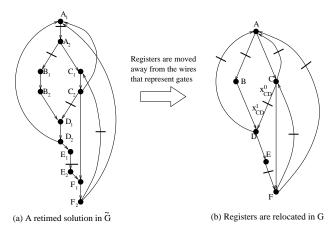

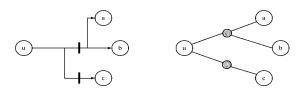

First of all, we move the registers in a gate either backward to the input wires or forward to the output wires of the gate, depending on which direction has a shorter distance. An example showing the relocation of registers is given in fig. 5. After this relocation step, the number of registers  $\hat{w}_{uv}$  on each edge  $e_{uv}$  is fixed. A linear program is used to determine the exact positions of the registers on the edges. Alternatively, the method in [26] can be used to minimize the clock period when the r values are unchanged in  $O(|V|^2|E|)$  time. The objective of the linear program is to minimize the clock period T subject to the constraints in register count on each edge. In

Fig. 4. Representation of gates by wires.

Fig. 5. Relocation of registers retimed into a gate.

the following, we use  $x_{uv}^k$  to denote the delay from the  $k^{th}$ register to the  $k+1^{st}$  register of the wire from node u to node v in G for  $k = 0, 1, ..., \hat{w}_{uv}$ . Notice that when  $\hat{w}_{uv} = 0$ ,  $x_{uv}^0$  is the delay of the whole wire; and when k = 0 and  $k = \hat{w}_{uv} > 0$ ,  $x_{uv}^k$  are the delays of the wire from node u to the first register and from the last register to node v, respectively. The linear program is formulated as follows:

Minimize T

Subject to

$$\sum_{k=0}^{\hat{w}_{uv}} x_{uv}^{k} = d_{uv} \quad \forall e_{uv} \in E$$

(9)

$x_{uv}^{\hat{w}_{uv}} + d_{v} \leq a(v) \quad \forall e_{uv} \in E \text{ s.t. } \hat{w}_{uv} > 0$  (10)

$a(u) + x_{uv}^{0} \leq T \quad \forall e_{uv} \in E \text{ s.t. } \hat{w}_{uv} > 0$  (11)

$a(u) + d_{uv} \leq a(v) \quad \forall e_{uv} \in E \text{ s.t. } \hat{w}_{uv} = 0$  (12)

For the circuit in fig. 5(b), example constraints are  $x_{CD}^0$  +  $x_{CD}^{1} = d_{CD}$  for type (9),  $x_{CD}^{1} + d_{D} \le a(D)$  for type (10),  $a(C) + x_{CD}^{0} \le T$  for type (11), and  $a(B) + d_{BD} \le a(D)$  for type (12). We can solve this linear program to obtain the best possible clock period  $T^*$  under the register count constraint on each edge. Notice that this linear program can solve the subproblem of finding the best possible position of each register on a wire optimally to minimize the clock cycle only when the register count on each edge is fixed, but the overall approach of handling both interconnect and gate delay is not optimal. The overall algorithm IG-Retiming() to handle both interconnect

and gate delay is summarized as follows:

## **Algorithm** *IG-Retiming()*

/\* Retime a sequential circuit with both interconnect and gate \*/

/\* delay to achieve a clock cycle very close to the minimum. \*/

Input: A sequential circuit C with both interconnect and gate delay

Output: A retimed circuit of C

- 1. Build graph G from C

- 2. Build  $\tilde{G}$  by replacing each gate in G by a wire of the same delay

- 3. Solve the retiming problem of  $\tilde{G}$  by *I-Retiming()*

- 4. Move registers away from wires that represent gates

- 5. Set up a linear program based on the register count on each edge edge has a register.

- 6. Solve the linear program to obtain a feasible retiming solution and the smallest possible clock period  $T^*$

#### IV. FLOP TOPOLOGY OPTIMIZATION

After retiming, we need to realize the circuit physically so that the optimal clock period obtained by retiming can be achieved. Given a retiming solution of the circuit (i.e., a target clock period T, a retiming label r(v) at each gate v and the maximum arrival time a(v) at the output of gate v) and the positions of its gates, we want to find the topologies of the nets and place the registers to realize the circuit, preserving the target clock T as much as possible.

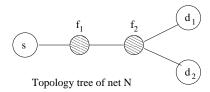

Now, consider a net N(s,D,L) in the retimed circuit, where s denotes the driving gate, D denotes the set of all driven gates, and L denotes the set of interconnections between s and each of the gates  $d_i \in D$ . Obviously,  $\{s\} \cup D \subseteq V$  and  $L \subseteq E$ . For each edge  $e_{sd_i} \in L$ , we have a value  $\hat{w}_r(s, d_i)$  representing the number of registers along the edge  $e_{sd_i}$  after retiming. The problem is to insert the minimum number of registers for this net into the circuit such that the target clock period is preserved as much as possible. This problem comprises two main subproblems known as topology finding and register placement. Topology finding is the problem of finding a topology,  $\Upsilon_N$ , of a net N given the exact geometric positions of the gates such that the minimum number of registers will be used and the target clock period will be preserved. Register placement is the problem of finding a position for each register given the topology  $\Upsilon_N$  of net N.

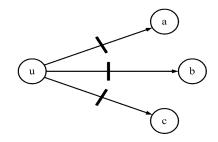

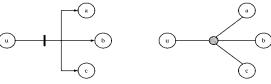

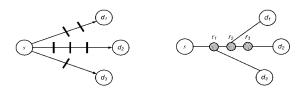

A topology  $\Upsilon_N = (P, K)$  is a tree (an acyclic graph with no designated root yet) that describes the structure of net N on the plane. Each node  $p \in P$  corresponds to either a combinational gate or a register, and each edge  $k_{uv} \in K$  represents a physical connection between gate/register u and gate/register v. Each node  $p \in P$  that has only one adjacent node in  $\Upsilon_N$ , i.e., deg(p) = 1, represents a combinational gate while an internal node  $p \in P$  that has more than one adjacent nodes, i.e., deg(p) > 1, represents a register. In fig. 6, an example of a 4-pin net in which each source-to-sink edge has a register after retiming is shown. There are five possible register sharing topologies in this example: (i) all the edges share a single register (maximum sharing) as shown in fig. 7(a); (ii) each edge has its own register (no sharing) as shown in fig. 7(b); and (iii) for the rest three equivalent cases, two edges share a single register while the other one has a separate register, as shown in fig. 7(c).

Although we can always identify the topology tree which has the maximum sharing of registers for a net, it is not always possible to place the registers on a chip using that topology

Fig. 6. Graph model of a 4-pin net obtained after retiming in which each edge has a register.

(a) A single register is shared between the edges (maximum sharing).

(b) Each edge has a separate register (no sharing).

(c) Two edges share a register while the other edge has a separate one.

Fig. 7. Five possible register sharing topologies. The topology tree of each configuration is shown on the right.

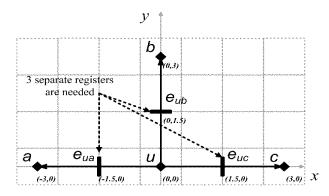

while preserving the target clock period. Using case (a) in fig. 7 as an example, suppose the clock period resulted from retiming, T, equals 1.5 units and the positions of the gates u, a, b and c are (0,0), (-3,0), (0,3) and (3,0) respectively, as depicted in fig. 8. Obviously, it is impossible to share a single register among the three edges without clock violation. Three separate registers have to be allocated and inserted exactly at (-1.5,0), (0,1.5) and (1.5,0) for edge  $e_{ua}$ ,  $e_{ub}$  and  $e_{uc}$  respectively in order to achieve the optimal clock period T.

Even if we have a feasible topology tree, it can happen that the suggested position for a register has been occupied, and we have to look for another appropriate position. The following sections will address how a feasible topology tree can be found and how the positions of the registers can be obtained.

## A. Topology Finding

In this section, an algorithm is proposed to find the topology of a net given the constraints in placement such that the maximum sharing of registers is achieved and the clock period

Fig. 8. A situation in which the registers cannot be shared in order to preserve the clock period T = 1.5 units.

Fig. 9. The retiming graph model (left) and the corresponding best possible topology  $\Upsilon_{N_{opt}}$  (right) of a 4-pin net example.

is preserved. This method can find the optimal topology for a net with four or fewer pins, and can give near-optimal solution for a net with five or more pins according to the experimental results.

Given a net N(s,D,L), a clock period T, and the maximal arrival time at the output of gate v, a(v), we can obtain a feasible topology tree of N,  $\Upsilon_N$ , as follows. First, we construct the best possible topology  $\Upsilon_{N_{opt}}$  for N, i.e., a topology having the minimum number of internal nodes (an internal node represents a register). Obviously, the number of internal nodes in  $\Upsilon_{N_{opt}}$  equals  $Q = \max_{d_i \in D} \{\hat{w}_r(s, d_i)\}$ , where  $\hat{w}_r(s, d_i)$  denotes the number of registers on edge  $e_{sd_i}$  after retiming. We label each internal node as  $f_i$  representing the *i*-th register on the net counting from the source s for  $1 \le i \le Q$ . An example of the retiming graph model and the corresponding best possible topology  $\Upsilon_{N_{opt}}$  for a 4-pin net is shown in fig. 9.

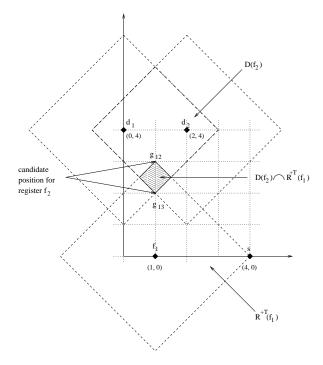

We call the region on the plane where a register f can be placed the *candidate region* of f and is denoted by D(f). For consistency, the candidate region D(v) of a combinational gate v is the position of v itself, i.e., its coordinates  $(x_v, y_v)$ , since v is already fixed in the placement. An  $\delta$ -extended region of a region  $\Re$ , denoted by  $R^{+\delta}(\Re)$ , is the region on the plane at a distance  $\delta$  or less from some point in  $\Re$ , assuming that the distance between two points is measured by their shortest Manhattan distance.

Besides, we define an adjacent-gate region for each node p in a topology tree, denoted by A(p), as an  $\delta$ -extended region from its candidate region D(p), i.e.,  $A(p) = R^{+\delta}(D(p))$ where  $\delta$  is defined differently for different types of nodes. The physical meaning of A(p) refers to the region on the plane that encompasses all the possible positions of an adjacent gate of p. The value  $\delta$  for the A(p) of a node p is described as follows. If node p is an internal node,  $\delta$  equals T. If node prepresents a driven gate,  $\delta$  equals  $a(p) - d_p$ . Otherwise, node p

Fig. 10. An example illustrating the SetY and ChangeTree process.

represents a driving gate, and we set  $\delta$  to T - a(p). Notice that all these regions are 45°-rotated rectangles on the rectilinear plane because of the Manhattan distance measurement.

Starting from the best possible topology  $\Upsilon_{N_{opt}}$ , we will modify the topology tree incrementally until an optimal feasible topology  $\Upsilon_N$  is obtained for net N. First of all, we choose the node that represents the driving gate s as the root in  $\Upsilon_{N_{out}}$  and direct all the edges away from s. Then, we will process each internal node  $f_i$  in  $\Upsilon_{N_{opt}}$  from i=Q to i=1, i.e., from the furthest register to the closest one, in the following manner. For each internal node  $f_i$  with a set of children  $q_1, \ldots, q_m$ , find a minimal set of the overlapping regions between  $A(q_j)$ for  $1 \le j \le m$ , denoted by  $Y_{min} = \{y_1, \dots, y_k\}$ , such that the union of the elements in  $Y_{min}$  covers at least one point from each region  $A(q_j)$ . For each  $y_l$  in  $Y_{min}$ , we call the number of regions that has at least one point in  $y_l$  as the *size* of  $y_l$ , denoted by  $s(y_l)$ . An example is shown in fig. 10(a). The elements in  $Y_{min}$  are then sorted in a non-ascending order of their sizes. The set  $Y_{min}$  can be found by the following procedure SetY:

```

Algorithm SetY(f_i, \Upsilon_N)

```

/\* Find the  $Y_{min}$  of an internal node  $f_i$  in a topology tree  $\Upsilon_N$ . \*/ Input: An internal node  $f_i$  with children  $q_1, \ldots, q_m$  in  $\Upsilon_N$ Output: Ymin 1.  $Y_{min} = \emptyset$

```

2. Add A(q_1) to Y_{min}, i.e., y_1 = A(q_1)

3. For j = 1 to m

overlapped = false

5.

For l = 1 to |Y_{min}|

6.

If (y_l \cap A(q_j) \neq \emptyset)

7.

```

$y_l = y_l \cap A(q_j)$ Sort the elements in  $Y_{min}$  in a non-ascending order of

9 overlapped = true10. Break

11. End if 12. End for

13. If (overlapped = false)Increment  $|Y_{min}|$  by 1

15. Add  $A(q_j)$  to  $Y_{min}$  at the end, i.e.,  $y_{|Y_{min}|} = A(q_j)$

End if 16. 17. End for

Notice that the union of the elements in  $Y_{min}$  covers at least one point from each region,  $A(q_j)$ , for  $1 \le j \le m$ . Next, we can remove all the edges from  $f_i$  to its children  $q_1, \ldots, q_m$  in  $\Upsilon_{N_{opt}}$ , and split the node  $f_i$  into k new internal nodes,  $n_1, \ldots, n_k$ , where node  $n_l$  corresponds to element  $y_l$  in  $Y_{min}$  for  $1 \le l \le k$ . In addition, we will assign region  $y_l$  as the candidate region of  $n_l$ , i.e.,  $y_l = D(n_l)$ , for  $1 \le l \le k$ . Starting from the  $y_l$  with the largest size in  $Y_{min}$ , an edge is added from  $n_l$  to each  $q_j$ that has no parent node yet and has  $A(q_j)$  covered by  $y_l$ . This step is repeated until all the  $y_l$  have been processed. Finally, an edge is added from the parent node of  $f_i$  to every newly

created internal nodes  $n_l$  and  $f_i$  will then be removed from the topology tree. An example is shown in fig. 10(b). The above operations are described by the procedure *ChangeTree* as follows.

```

Algorithm ChangeTree(f_i, Y_{min}, \Upsilon_N)

/* Modify a topology tree \Upsilon_N by replacing an internal node f_i */

/* by several other nodes. */

Input: An internal node f_i in \Upsilon_N and the corresponding Y_{min}

Output: A modified topology tree

1. Remove all the edges from f_i to its children q_1, \ldots, q_m in \Upsilon_N

Instantiate k new internal nodes, n_1, \ldots, n_k, where k = |Y_{min}|

Assign region y_l as the candidate region of n_l, i.e.,

y_l = D(n_l) \forall 1 \le l \le k

For l = 1 to k

For j = 1 to m

If (y_l \cap A(q_i) \neq \emptyset and q_i has no parent node yet)

6.

7.

Add an edge from n_l to q_i

8.

End if

End for

10.

Add an edge from the parent node of f_i to n_l

11. End for

12. Remove f_i

13. Output(\Upsilon_N)

```

After visiting all the internal nodes  $f_i$  in  $\Upsilon_{N_{opt}}$  and modifying the topology as described above, we will get a new topology tree  $\Upsilon_N$  at the end. The whole algorithm of *topology finding* of a net N is described in the following procedure *TopTree*.

```

Algorithm TopTree(N)

```

```

/* Construct a feasible topology tree \Upsilon_N of a net N. */

Input: A net N in a circuit

Output: A topology tree \Upsilon_N for N

1. Construct the best possible topology tree \Upsilon_{N_{opt}} for net N

2. \Upsilon_N = \Upsilon_{N_{opt}}

3. For i = Q to 1 where Q is the number of internal nodes in \Upsilon_{N_{opt}}

4. Y_{min} = GetY(f_i, \Upsilon_N)

5. \Upsilon_N = ChangeTree(f_i, Y_{min}, \Upsilon_N)

```

6. End for

7. Output( $\Upsilon_N$ )

To prove the correctness of the above algorithms, i.e., the statement of Theorem 1, we need to prove the following three lemmas first.

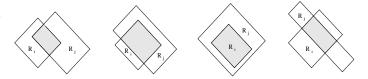

*Lemma 2:* Given a set of n 45°-rotated rectangles  $R_1, \ldots, R_n$  on a rectilinear plane, if  $R_1 \cap \ldots \cap R_n \neq \emptyset$ , then  $R^{+x}(R_1) \cap \ldots \cap R^{+x}(R_n) \neq \emptyset$ , where x is a non-negative real number.

*Proof:* Since  $R_1 \cap ... \cap R_n \subseteq R^{+x}(R_1) \cap ... \cap R^{+x}(R_n)$ , the argument follows.

*Lemma 3:* Given a set of n 45°-rotated rectangles  $R_1, \ldots, R_{n-1}$  and S on a rectilinear plane, if  $S \cap R_i \neq \emptyset$  for  $1 \leq i \leq n-1$  and  $R_1 \cap \ldots \cap R_{n-1} \neq \emptyset$ , then  $S \cap (R_1 \cap \ldots \cap R_{n-1}) \neq \emptyset$ .

*Proof:* It can be proved by induction. For the base case when n=3, consider three  $45^{\circ}$ -rotated rectangles  $R_1$ ,  $R_2$  and S on a rectilinear plane. If  $R_1 \cap R_2 \neq \emptyset$ , there are only four ways that  $R_1$  and  $R_2$  overlap with each other, as shown in fig. 11. It is easy to see that in each case if  $S \cap R_1 \neq \emptyset$  and  $S \cap R_2 \neq \emptyset$ ,  $S \cap R_1 \cap R_2 \neq \emptyset$ . When n>3, let  $R'_{n-2}=R_1 \cap \ldots \cap R_{n-2} \neq \emptyset$ . By the inductive hypothesis,  $S \cap R'_{n-2} \neq \emptyset$ . Since,  $S \cap R_{n-1} \neq \emptyset$  and  $R'_{n-2} \cap R_{n-1} \neq \emptyset$ , we can conclude that  $S \cap R'_{n-2} \cap R_{n-1} \neq \emptyset$ , i.e.,  $S \cap (R_1 \cap \ldots \cap R_{n-1}) \neq \emptyset$ , following a similar argument as in the case for n=3.

*Lemma 4:* Given two 45°-rotated rectangles, A and B, on a rectilinear plane, we denote the *n times T-extended regions* of A and B as  $A_n$  and  $B_n$  respectively, i.e.,  $A_n = R^{+(n \times T)}(A)$  and

Fig. 11. Four possible ways that two 45°-rotated rectangles overlap

$B_n = R^{+(n \times T)}(B)$ . Suppose  $A \cap B = R_{AB} \neq \emptyset$ , we denote the n times T-extended region of  $R_{AB}$  by  $(R_{AB})_n$ , i.e.,  $(R_{AB})_n = R^{+(n \times T)}(R_{AB})$ . It is claimed that if there exists a point  $x \in A_n \cap B_n$ ,  $x \in R^{+T}((R_{AB})_{n-1})$  for all  $n \ge 1$ .

*Proof:* We prove by induction on n.

Base case:

Consider the case when n=1. Suppose  $x \in A_1 \cap B_1$ , the T-extended region from the position of x is given by  $R^{+T}(x)$ . Obviously,  $R^{+T}(x) \cap A_0 \neq \emptyset$  and  $R^{+T}(x) \cap B_0 \neq \emptyset$  because  $x \in A_1 \cap B_1$ . Since  $A_0 \cap B_0 \neq \emptyset$  (because  $A_0 = A, B_0 = B$  and  $A \cap B \neq \emptyset$ ),  $R^{+T}(x) \cap (A_0 \cap B_0) \neq \emptyset$  by *lemma 3*. Therefore,  $x \in R^{+T}((R_{AB})_0)$  and the claim is true. *Inductive step:*

Assume that the claim is true for n=j-1, where j is a positive integer  $\geq 2$ , i.e., if there exists a point  $x \in A_{j-1} \cap B_{j-1}$ ,  $x \in R^{+T}((R_{AB})_{j-2})$ . Consider the case when n=j. Given a point  $x \in A_j \cap B_j$ , the T-extended region from x is denoted by  $R^{+T}(x)$ . Obviously,  $R^{+T}(x) \cap A_{j-1} \neq \emptyset$  and  $R^{+T}(x) \cap B_{j-1} \neq \emptyset$  because  $x \in A_j \cap B_j$ . By  $lemma\ 2$ , since  $A_0 \cap B_0 \neq \emptyset$ ,  $A_{j-1} \cap B_{j-1} \neq \emptyset$ . Therefore,  $R^{+T}(x) \cap (A_{j-1} \cap B_{j-1}) \neq \emptyset$  by  $lemma\ 3$ . By the induction hypothesis, if  $R^{+T}(x) \cap (A_{j-1} \cap B_{j-1}) \neq \emptyset$ ,  $R^{+T}(x) \cap R^{+T}((R_{AB})_{j-2}) \neq \emptyset$ . Therefore,  $x \in R^{+T}((R_{AB})_{j-1})$ .

Theorem 1: The proposed algorithm TopTree() can find a topology that maximizes the sharing of registers for an i-pin net, where  $2 \le i \le 4$ , and the target clock period T is preserved.

*Proof:* We prove the three possible cases one-by-one.

#### **Case 1:** i = 2

This case is trivial because there is only one source s, one sink  $t_1$  and one edge  $e_{st_1}$  in a 2-pin net, and there is no other edges to share registers with. The algorithm will start from the furthest internal node  $f_Q$  and take the adjacent-gate region of  $t_1$ ,  $A(t_1) = R^{+(a(t_1)-d_{t_1})}(D(t_1))$ , as the candidate region of  $f_Q$ , i.e.,  $D(f_Q) = A(t_1)$ . Next, the algorithm will process node  $f_{Q-1}$  and take the adjacent-gate region of  $f_Q$ ,  $A(f_Q) = R^{+T}(D(f_Q))$ , as the candidate region of  $f_{Q-1}$ , i.e.,  $D(f_{Q-1}) = A(f_Q)$ .

By substitution,  $D(f_{Q-1})$  can be represented as an extended region from the position of the sink  $t_1$ ,  $D(f_{Q-1}) = R^{+((a(t_1)-d_{t_1})+T)}(D(t_1))$ . The algorithm repeats the above steps until it reaches the first internal node  $f_1$  where  $D(f_1) = R^{+((a(t_1)-d_{t_1})+(Q-1)\times T)}(D(t_1))$ . Since the retiming solution is valid, the interconnect delay between s and  $t_1$  will not exceed  $(T-a(s))+((Q-1)\times T)+(a(t_1)-d_{t_1})$ . Therefore, the algorithm can find the candidate region for every register and return the best possible topology when it terminates.

### **Case 2:** i = 3

Given a 3-pin net, let s be the source, and  $t_1$  and  $t_2$  be the two sinks. Let  $\hat{w}_r(s,t_1)$  and  $\hat{w}_r(s,t_2)$  be p and q respectively, where  $1 \le p \le q$ . Suppose that there exists a topology tree of maximum register sharing for the 3-pin net such that the first

k registers, where  $1 \le k \le p$ , are shared (notice that if the k-th register can be shared, the k-th register can also be shared where  $1 \le k \le k$ ), but that the algorithm cannot find such a topology.

Since the algorithm cannot find that optimal topology, it must fail to find an overlapping region for the k-th register to be shared. At the point of failure, the algorithm should find that the regions  $R^{+((a(t_1)-d_{t_1})+T\times(p-k-1))}(t_1)$  and  $R^{+((a(t_2)-d_{t_2})+T\times(q-k-1))}(t_2)$  do not overlap. However, these two regions encompass all the possible positions for the k-th register from  $t_1$  and  $t_2$  respectively such that the clock period T will not be violated. Therefore, should the k-th register be able to be shared as assumed, it must lie within these two regions and the algorithm must be able to find it. Contradiction occurs.

Given a 4-pin net, let s be the source, and  $t_1$ ,  $t_2$  and  $t_3$  be the three sinks. Let  $\hat{w}_r(s,t_1)$ ,  $\hat{w}_r(s,t_2)$  and  $\hat{w}_r(s,t_3)$  be p, q and r respectively, where  $1 \le p \le q \le r$ . Suppose the algorithm is attempting to share the k-th register where  $1 \le k \le p$ , i.e., it is trying to find a minimal subset of the overlapping regions such that it covers all the extend regions  $R^{+((a(t_1)-d_{t_1})+T\times(p-k-1))}(t_1)$ ,  $R^{+((a(t_2)-d_{t_2})+T\times(q-k-1))}(t_2)$  and  $R^{+((a(t_3)-d_{t_3})+T\times(r-k-1))}(t_3)$ , denoted by A, B and C respectively. Notice that we only consider when  $k \le p$  and assume that the three paths from s to  $t_1$ ,  $t_2$  and  $t_3$  are not merged yet (i.e., no sharing of registers from k+1 to r). Otherwise, the situation will fall into case 1 or case 2 as discussed above.

There are 4 distinct sub-cases. First, A, B and C are disjoint. It means that the k-th register cannot be shared and the algorithm will introduce three new internal nodes to represent the registers and continues with the next internal node  $f_{k-1}$ . Second, A, B and C overlap with each other. It means that the k-th register can be shared among  $t_1$ ,  $t_2$  and  $t_3$ . The algorithm will introduce a single internal node to represent the register and continues. The correctness of the algorithm in these two cases is trivial and will not be elaborated.

The third sub-case is, without loss of generality, that  $A \cap B \neq \emptyset$  and  $B \cap C \neq \emptyset$  but  $A \cap C = \emptyset$ . Denote the region  $A \cap B$  as  $R_{AB}$  and the region  $B \cap C$  as  $R_{BC}$ . There are three possible options that the algorithm can choose from when evaluating the k-th register: (i) it does not share the k-th register and introduces three different registers for the sinks; (ii) it shares the k-th register between  $t_1$  and  $t_2$  but a separate one for  $t_3$ ; (iii) it shares the k-th register between  $t_2$  and  $t_3$  but a separate one for  $t_1$ . Our algorithm will choose arbitrarily between (ii) and (iii) (since  $R_{AB}$  and  $R_{BC}$  have the same size and their order in  $Y_{min}$  is arbitrary), but it will never choose (i). We assume that the algorithm chooses (ii) in the following analysis.

First, we compare the choices of (i) and (ii). Notice that (i) can be better than (ii) only when the three separate paths can be merged together at a subsequent step when register h is being processed where  $1 \le h < k$ , while the combined path of  $(t_1 \text{ and } t_2)$  and the path of  $t_3$  cannot be merged at the h-th register. We are going to show that this will not happen.

If we choose (i), suppose that there exists a point x on the plane such that  $x \in A_j \cap B_j \cap C_j$ , where  $A_j$ ,  $B_j$  and  $C_j$  represent the j times T-extended regions of A, B and C respectively, during a subsequent step when register h is being

processed where  $1 \le h < k$ . By *lemma 4*, it is shown that  $x \in R^{+T}((R_{AB})_{j-1})$ , where  $(R_{AB})_{j-1}$  is the (j-1) times T-extended region from  $R_{AB}$ . This means that if it is possible to share the h-th register among the three edges without sharing the k-th register at the first place, by choosing (ii), i.e., to share the k-th register between  $t_1$  and  $t_2$ , the algorithm will also be able to share the k-th register among the edges. Therefore, (ii) is better than (i) by sharing more registers.

Next, we compare the choices of (ii) and (iii) similarly. Consider at a subsequent step when register h is being processed where  $1 \le h < k$ . Suppose we choose (iii) and there exists a point x on the plane such that  $x \in A_j \cap (R_{BC})_j$ , where  $A_j$  and  $(R_{BC})_j$  represent the j times T-extended regions of A and  $R_{BC}$  respectively. Obviously, there exists a point y covered by  $A_j \cap B_j \cap C_j$ , i.e.,  $y \in A_j \cap B_j \cap C_j$ . By lemma 4,  $y \in R^{+T}((R_{AB})_{j-1})$ , i.e.,  $y \in R^{+T}((R_{AB})_{j-1}) \cap C_j$ , so the h-th register can also be shared among the three edges by choosing (ii). Therefore, (ii) is no worse than (iii). As a result, the algorithm will find the optimal solution by choosing arbitrarily either (ii) or (iii).

Finally, if two pairs of the regions overlap while the other is disjoint, i.e.,  $A \cap B \neq \emptyset$  but  $A \cap C = \emptyset$  and  $B \cap C = \emptyset$ , the analysis is similar to the third sub-case above.

## B. Register Placement

In this section, we discuss how registers are actually placed using the topology tree yielded from the algorithm TopTree(). Since some parts of the chip are occupied, we need to know where on the chip a register can be placed. To tackle this problem, we divide the chip into a mesh of  $m \times n$  grids. For each grid  $g_{ij}$ , we keep track of its center coordinates,  $(x_{g_{ii}}, y_{g_{ii}})$ , and the size of the free space in the grid,  $F(g_{ij})$ .

Given a topology tree  $\Upsilon_N$ , choose arbitrarily an internal node f to be the root of  $\Upsilon_N$ , and direct the edges of  $\Upsilon_N$  away from f. Starting from the root f, we choose a grid whose center is contained in D(f), i.e., the candidate region for placing the register f, and it has the largest free space available. We denote this grid as g(f). If  $F(g(f)) \geq z$ , where z denotes the size of a register, we take the center of g(f) as the position of register f. Otherwise, we allow a controlled degree of inaccuracy by extending D(f) one grid width further, i.e.,  $R^{+g_w}(D(f))$ , where  $g_w$  represents the width of a grid, by repeating the same process with  $R^{+g_w}(D(f))$  instead of D(f) in searching of a feasible grid for placing register f. If no such grid is found, the placement of this register is reported as unsuccessful. This could happen because the register counts may increase greatly after retiming.

Let  $q_1, \ldots, q_m$  be the set of nodes which are the children of f in the topology tree  $\Upsilon_N$ . After fixing the position of f, register  $q_j$ , for  $1 \le j \le m$ , is placed arbitrarily in its candidate region  $D(q_j)$  provided that it is at a distance T or less units from f. After visiting all the internal nodes of  $\Upsilon_N$ , the position of each register is fixed.

Suppose we have a 3-pin net N(s,D,L) and its topology tree  $\Upsilon_N$  is shown in fig. 12. The topology tree  $\Upsilon_N$  shows that the two driven gates  $d_1$  and  $d_2$  will share two registers represented by the internal nodes  $f_1$  and  $f_2$ . In this example, we assume

Fig. 12. The topology tree  $\Upsilon_N$  of a 3-pin net where  $f_1$  and  $f_2$  are two shared registers.

Fig. 13. An illustration of the register placement procedure.

that T = 3 units. Consider a  $5 \times 5$  mesh as shown in fig. 13, where the driving gate s and the two driven gates,  $d_1$  and  $d_2$ , are assumed to be at the centers of the grids containing them correspondingly, i.e., gate s is located at (4,0), gate  $d_1$ is located at (0,4) and gate  $d_2$  is located at (2,4). Suppose  $\Upsilon_N$ is rooted at node  $f_1$  and the algorithm has fixed its position at (1,0), let us examine how the position of  $f_2$  is determined. The candidate region  $D(f_2)$  of  $f_2$  covers the centers of grids  $g_{03}$ ,  $g_{04}$ ,  $g_{12}$ ,  $g_{13}$ ,  $g_{14}$ ,  $g_{23}$  and  $g_{24}$ . Then starting from the position of  $f_1$ , the algorithm expands a rectangle of distance T from it, denoted by  $R^{+T}(f_1)$  as shown. Next, the algorithm will find that  $D(f_2) \cap R^{+T}(f_1)$  is not empty and covers the center of grid  $g_{12}$  and  $g_{13}$  - the candidate positions of register  $f_2$ . Assuming that the free space of  $g_{12}$  is greater than that of  $g_{13}$ , i.e.,  $F(g_{12}) \ge F(g_{13}) \ge z$ , the algorithm will then assign the center of  $g_{12}$  as the position of  $f_2$ .

# V. EXPERIMENTAL RESULTS

We performed retiming and topology optimization on the ISCAS89 benchmark suite. The program was implemented in C language and run on a 1.5GHz Intel Pentium IV processor with 256KB cache and 512MB RAM. In our experiments, we implemented the circuits using a  $0.35\mu m$  CMOS standard cell library from Austria Micro Systems and Silicon Ensemble was

used to layout the design with a setting of 50% row utilization. Gate delays were referenced from the data book while wire lengths were estimated using the shortest Manhattan distance between the connected cells. We scaled the wire delay according to [34] in which a 1mm wire was assumed to have a delay of 150ps approximately. The size of a grid was set to be twice as large as a D-type flip flop. During the placement of a register, we allowed an error of one-grid width, i.e., the width of a D-type flip flop.

The results are shown in Table 1. The first column indicates the names of the circuits, and the numbers shown in brackets are the total numbers of gates in the circuits (cell\_no). The second column shows the numbers of logical registers ( $f f_{old}$ ) in the retiming graph model after retiming, and the numbers shown in brackets are the numbers of registers in the original input circuits before retiming. The number of registers had increased after retiming for most of the circuits because the retiming method that we used did not minimize the number of registers as one of its objectives. In the third column, the minimum possible numbers of registers required after sharing are shown, i.e., assuming that every net could be realized using the best topology. The fourth column shows the numbers of registers  $(ff_{new})$  that have actually been inserted after the flop topology optimization step. It can be observed that the numbers in the fourth column are the same as those in the third column except for circuit s3271 and s4863. This observation showed that almost all the nets in our test cases could have their registers inserted using the best topology, showing that our proposed algorithm can very often find a near-optimal solution for register insertion. The fifth column shows the percentage reduction in area due to the topology optimization step. This is calculated as  $(ff_{old} - ff_{new})X/cell\_no$  where X is the average ratio of the size of a register to the size of a simple gate. We can see from the fifth column that the reduction in area is about 8.1X% on average. Since the size of a register is usually several times larger than that of a simple gate, the reduction in area is significant for most of the circuits. The sixth column shows the statistics of the numbers of nets containing 4 or fewer edges with registers whereas the seventh column shows the numbers of nets having 5 or more edges with registers. The eighth column shows the numbers of registers that are placed within their candidate regions while the ninth column shows the numbers of registers that are placed outside their candidate regions but with a controlled error range (one grid size). As we can see, all the registers are placed in their candidate regions successfully in all the test cases. Finally, the CPU runtime is shown in the last column.

In this set of experiments, the topology optimization step is performed on top of a retiming solution with minimum delay. For a min-area retiming solution, the circuit is retimed to minimize the total number of registers. The benefit of this topology optimization step might be less in that case since the registers will tend to be moved towards the fanins or the fanouts of a gate depending on whichever is smaller in number in a min-area retiming solution, and the number of possible sharings achieved in the topology optimization step might be reduced. However, different from the min-area retiming that it minimizes the number of registers by retiming, the topology

13.41

|                 | No. of      | Min. no. | Actual no. |           | Nets with  | Nets with  | No. of regs. | No. of regs. |      |

|-----------------|-------------|----------|------------|-----------|------------|------------|--------------|--------------|------|

|                 | logical     | of regs. | of regs.   | Reduction | 4 or fewer | 5 or more  | placed in    | placed with  | CPU  |

| Circuit         | regs. after | after    | using our  | in area   | edges      | edges      | candidate    | controlled   | time |

|                 | retiming    | sharing  | method     | (%)       | with regs. | with regs. | region       | error        | (s)  |

| s641 (381)      | 87 (19)     | 53       | 53         | 8.9X      | 53         | 0          | 53           | 0            | 0.01 |

| s713 (395)      | 94 (19)     | 55       | 55         | 9.9X      | 54         | 1          | 55           | 0            | 0.02 |

| s820 (291)      | 24 (5)      | 23       | 23         | 0.34X     | 23         | 0          | 23           | 0            | 0.01 |

| s832 (289)      | 23 (5)      | 22       | 22         | 0.35X     | 22         | 0          | 22           | 0            | 0.01 |

| s1196 (531)     | 31 (18)     | 18       | 18         | 2.4X      | 17         | 1          | 18           | 0            | 0.00 |

| s1238 (510)     | 32 (18)     | 18       | 18         | 2.7X      | 17         | 1          | 18           | 0            | 0.00 |

| s1269 (571)     | 259 (74)    | 127      | 127        | 23X       | 113        | 14         | 127          | 0            | 0.02 |

| s1488 (655)     | 90 (6)      | 73       | 73         | 2.6X      | 71         | 2          | 73           | 0            | 0.02 |

| s1494 (649)     | 78 (6)      | 62       | 62         | 2.5X      | 60         | 2          | 62           | 0            | 0.01 |

| s3271 (1574)    | 826 (232)   | 342      | 438        | 25X       | 276        | 18         | 438          | 0            | 0.18 |

| s4863 (2344)    | 622 (208)   | 408      | 417        | 8.7X      | 360        | 22         | 417          | 0            | 0.25 |

| s15850.1 (9774) | 1554 (534)  | 1264     | 1264       | 3.0X      | 1203       | 26         | 1264         | 0            | 2.52 |

16X

2601

280

TABLE I

EXPERIMENTAL RESULTS OF REGISTER PLACEMENT WITH CLOCK PRESERVATION.

optimization step tries to reduce the register count by sharing the registers along the fanout connections of a gate physically. Therefore, it will still be beneficial to perform the optimization step on top of a min-area retiming solution.

2899

2899

5455 (728)

s35932 (16067)

Another set of experiments was performed to study the optimal and near-optimal retiming algorithms. In these experiments, the circuits were layout by Silicon Ensemble and wire delays (shortest Manhattan distance) were then extracted. The lower and upper bounds of the binary search were set to 0 and 100ns respectively. In the near-optimal approach, we performed the procedure *I-Retiming()* with an error bound of 1%. After assigning the registers retimed into a gate to the appropriate wires, a linear program was set up to relocate the registers on the wires to get the smallest possible clock period  $T^*$ . In the optimal approach, binary search was performed until an error bound of 0.01% was obtained. We call the resulting clock period  $T_{opt}$ . Notice that we do not need to obtain a very accurate result from *I-Retiming()* because the solution is optimized by the linear program afterwards. On average, the number of binary search iterations is 9.6 for the near-optimal approach and 16.5 for the optimal approach.

The results are shown in Table II. The second and third columns give the numbers of nodes and the numbers of edges in the graph G, respectively. Notice that all circuits are not strongly connected. The numbers of nodes and edges listed are those after the addition of the source node, the target node, and the associated edges. The fourth and fifth columns show the numbers of nodes and the numbers of edges in the reduced graph H, respectively. These two values are dependent on the node chosen as the root in the depth-first traversal. In our current implementation, we always pick the additional node s as the root. We notice that using other nodes as the root does not change the result significantly. The speedup of the Bellman-Ford algorithm by the graph reduction approach in Section III-B1 is  $(|V||E|)/(|V_b||E_H|)$ , which is given in the sixth column. The graph reduction approach is faster in all circuits. On average, it is faster by 19.15 times. However, the speedup is less for larger circuits. The reason is that  $|E_H|$ is roughly quadratic in  $|V_b|$ . For the circuits in Table II, the ratio of  $|E_H|$  to  $|V_b|^2$  is from 0.21 to 0.86 with an average of 0.55. Therefore, the graph reduction approach may not be useful for large circuits. We can avoid a slowdown of the Bellman-Ford algorithm by determining whether to use G or H based on the ratio  $(|V||E|)/(|V_b||E_H|)$ .  $|V_b|$  and  $|E_H|$  can be found in  $O(|V_b||E|)$  time. We only need to perform this checking once for each circuit. Hence, the runtime overhead is insignificant compared with the total runtime. The seventh, eighth, and ninth columns show the runtime of the *I-Retiming()* procedure, the time taken to solve the linear program, and the total runtime, respectively. The tenth column shows the runtime for the optimal approach. We can see that the nearoptimal approach is much more efficient than the optimal approach (especially for large circuits). The eleventh and twelfth columns show the clock periods  $T^*$  and  $T_{opt}$  obtained by the near-optimal approach and the optimal approach, respectively. The last column is the percentage increase of  $T^*$  over  $T_{opt}$ . The clock period produced by the near-optimal approach is only 0.06% more than that by the optimal approach on average.

2899

## VI. CONCLUSION

In this paper, we proposed an algorithm to retime a circuit with both gate and interconnect delay, and then realize the retimed circuit physically to achieve the optimal clock period. The proposed algorithm can preserve the target clock period obtained by retiming with a controlled error using as few registers as possible. In addition, the algorithm is proved to be giving the optimal topology for nets with four or fewer pins. Since this type of nets makes up for about 90% of the nets in a sequential circuit on average, the algorithm performs very well and effectively under most situations. For the circuit retiming problem, we presented two elegant approaches to perform retiming on sequential circuits with both interconnect and gate delay. Our first approach is extended from the MILP approach in the paper [3] and can solve the problem optimally. Our second approach is an improvement over the first one in terms of practical applicability. The main idea is to transform the problem into a single-source longest paths problem in a reduced graph. Experimental results show that the second

|         | No. of | No. of | No. of   | No. of   |              | CPU Time                         |       |         |         | Clock Period |                               |      |

|---------|--------|--------|----------|----------|--------------|----------------------------------|-------|---------|---------|--------------|-------------------------------|------|

| Circuit | Nodes  | Edges  | Nodes    | Edges    | V  E         | I-Retiming + LP = $IG$ -Retiming |       | Optimal | $T^*$   | $T_{opt}$    | $\frac{T^*-T_{opt}}{T_{opt}}$ |      |

|         | in $V$ | in $E$ | in $V_b$ | in $E_H$ | $ V_b  E_H $ | (sec)                            | (sec) | (sec)   | (sec)   | (ns)         | (ns)                          | (%)  |

| s1488   | 655    | 1405   | 27       | 627      | 54.36        | 0.09                             | 0.19  | 0.28    | 5.62    | 18.85        | 18.82                         | 0.16 |

| s1494   | 649    | 1411   | 30       | 749      | 40.75        | 0.09                             | 0.16  | 0.25    | 4.37    | 20.78        | 20.78                         | 0.00 |

| s3271   | 1574   | 2707   | 112      | 3360     | 11.32        | 0.38                             | 0.71  | 1.09    | 33.70   | 10.24        | 10.24                         | 0.00 |

| s4863   | 2344   | 4093   | 154      | 20413    | 3.05         | 2.13                             | 0.99  | 3.12    | 87.75   | 23.58        | 23.58                         | 0.00 |

| s15850  | 9774   | 13794  | 603      | 100738   | 2.22         | 21.42                            | 2.60  | 24.02   | 1545.59 | 67.82        | 67.82                         | 0.00 |

| s35932  | 16067  | 28590  | 884      | 163945   | 3.17         | 54.59                            | 6.66  | 61.25   | 8644.27 | 29.59        | 29.54                         | 0.17 |

Using a 1.8GHz Intel Xeon PC with 512 KB cache and 512 MB RAM.

TABLE II

THE RUNTIME OF THE RETIMING ALGORITHMS AND THE CLOCK PERIODS OBTAINED.

approach gives solutions that are only 0.06% larger than the optimal on average but in a much shorter runtime. Together with this powerful retiming methods, our proposed algorithm can be applied to pipeline long global interconnects. This is particularly useful in today's designs in which multiple clock cycles are required to propagate a signal across a global wire.

#### REFERENCES

- T. C. Tien, H. P. Su, and Y. W. Tsay. Integrating Logic Retiming and Register Placement. In *Proceedings IEEE International Conference on Computer-Aided Design*, pages 136–139, 1998.

- [2] I. Neumann and W. Knuz. Layout Driven Retiming Using the Coupled Edge Timing Model. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, 22(7), 2003.

- [3] C. E. Leiserson and J. B. Saxe. Retiming Synchronous Circuitry. Algorithmica, 6:5–35, 1991.

- [4] C. V. Schimpfle, S. Simon, and J. A. Nossek. Optimal Placement of Registers in Data Paths for Low Power Design. In *Proceedings IEEE International Symposium on Circuits and Systems*, pages 2160–2163, 1997

- [5] J. Monteiro, S. Devadas, and A. Ghosh. Retiming Sequential Circuits for Low Power. In *Proceedings IEEE International Conference on Computer-Aided Design*, pages 398–402, 1993.

- [6] A. El-Maleh, T. E. Marchok, J. Rajski, and W. Maly. Behavior and Testability Preservation under the Retiming Transformation. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, 16:528–542, 1997.

- [7] S. Dey and S. Chakradhar. Retiming Sequential Circuits to Enhance Testability. In *Proceedings IEEE VLSI Test Symposium*, pages 28–33, 1994

- [8] R. K. Ranjan, V. Singhal, F. Somenzi, and R. K. Brayton. On the Optimization Power of Retiming and Resynthesis Transformation. In Proceedings IEEE International Conference on Computer-Aided Design, pages 402–407, 1998.

- [9] P. Pan, A. K. Karandikar, and C. L. Liu. Optimal Clock Period Clustering for Sequential Circuits with Retiming. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, 17(6):489–498, 1998.

- [10] J. Cong, H. Li, and C. Wu. Simultaneous Circuit Partitioning/Clustering with Retiming for Performance Optimization. In Proceedings ACM/IEEE Design Automation Conference, pages 460–465, 1999.

- [11] J. Cong, S. K. Lim, and C. Wu. Performance Driven Multi-level and Multiway Partitioning with Retiming. In *Proceedings ACM/IEEE Design Automation Conference*, pages 274–279, 2000.

- [12] J. Cong and S. K. Lim. Physical Planning with Retiming. In *Proceedings IEEE International Conference on Computer-Aided Design*, pages 2–7, 2000.

- [13] N. Shenoy and R. Rudell. Efficient Implementation of Retiming. In Proceedings IEEE International Conference on Computer-Aided Design, pages 226–233, 1994.

- [14] N. Shenoy, R. K. Brayton, and A. Sangiovanni-Vincentelli. Retiming of Circuits with Single Phase Transparent Latches. In *Proceedings IEEE International Conference on Computer-Aided Design*, pages 86–89, 1991.

- [15] R. B. Deokar and S. S. Sapatnekar. A Fresh Look at Retiming via Clock Skew Optimization. In *Proceedings ACM/IEEE Design Automation Conference*, pages 310–315, 1995.

- [16] M. C. Papaefthymiou. Asymptotically Efficient Retiming under Setup and Hold Constraints. In *Proceedings IEEE International Conference* on Computer-Aided Design, pages 396–401, 1998.

- [17] H. J. Touati and R. K. Brayton. Computing the Initial States of Retimed Circuits. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, 12:157–162, 1993.

- [18] I. Karkowski and R.H.J.M. Otten. Retiming Synchronous Circuitry with Imprecise Delay. In *Proceedings ACM/IEEE Design Automation Conference*, pages 322–326, 1995.

- [19] V. Singhal, S. Malik, and R. K. Brayton. The Case for Retiming with Explicit Reset Circuitry. In *Proceedings IEEE International Conference* on Computer-Aided Design, pages 618–625, 1996.

- [20] N. Maheshwari and S. S. Sapatnekar. An Improved Algorithm for Minimum-area Retiming. In *Proceedings ACM/IEEE Design Automation Conference*, pages 2–7, 1997.

- [21] T. Soyata and E. G. Friedmann. Retiming with nonzero clock skew, variable register and interconnect delay. In *Proceedings IEEE International Conference on Computer-Aided Design*, pages 234–241, 1994.

- [22] K. N. Lalgudi and M. C. Papaefthymiou. DELAY: An Efficient Tool for Retiming with Realistic Delay Modeling. In *Proceedings ACM/IEEE Design Automation Conference*, pages 304–309, 1995.

- [23] A. Tabbara, R. K. Brayton, and A. R. Newton. Retiming for DSM with Area-Delay Trade-offs and Delay Constraints. In *Proceedings ACM/IEEE Design Automation Conference*, pages 725–730, 1999.

- [24] C. Lin and H. Zhou. Retiming for Wire Pipelining in System-On-Chip. Proceedings IEEE International Conference on Computer-Aided Design, 2003

- [25] C. Lin and H. Zhou. Wire Retiming for System-On-Chip by Fixpoint Computation. Design, Automation and Test in Europe Conference and Exhibition, 2004.

- [26] C. Lin and H. Zhou. Optimal Wire Retiming Without Binary Search. Proceedings IEEE International Conference on Computer-Aided Design, 2004.

- [27] C. E. Leiserson and J. B. Saxe. A Mixed-Integer Programming Problem Which is Efficiently Solvable. *Journal of Algorithms*, 9:114–128, 1988.

- [28] E. L. Lawler. Combinatorial Optimizations: Networks and Matroids. Holt, Rinehart and Winston, 1976.

- [29] S. M. Burns. Performance Analysis and Optimization of Asynchronous Circuits. Ph.D. Thesis, California Institute of Technology, 1991.

- [30] M.C. Papaefthymiou. Understanding Retiming Through Maximum Average-delay Cycles. *Mathematical Systems Theory*, (27):65–84, 1994.

- [31] A. Dasdan, S. S. Irani, and R. K. Gupta. Efficient Algorithms for Optimum Cycle Mean and Optimum Cost to Time Ratio. *Proceedings* ACM/IEEE Design Automation Conference, pages 37–42, 1999.

- [32] T. H. Cormen and C. E. Leiserson and R. L. Rivest. *Introduction to Algorithms*. McGraw Hill, eighth edition, 1992.

- [33] Y-Z. Liao and C. K. Wong. An Algorithm to Compact a VLSI Symbolic Layout with Mixed Constraints. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, 2(2):62–69, 1983.

- [34] J. Cong, L. He, K. Y. Khoo, C. K. Koh, and Z. Pan. Interconnect Design for Deep Submicron ICs. *Proceedings IEEE International Conference* on Computer-Aided Design, pages 478–485, 1997.

PLACE PHOTO HERE **Dennis K.Y. Tong** Dennis K. Y. Tong received his B.Eng.(Hons.) and M.Phil. degrees in Computer Science and Engineering, in 2002 and 2004, respectively, from the Chinese University of Hong Kong, Shatin, N.T., Hong Kong. His research interests include retiming and floorplanning.

PLACE PHOTO HERE Evangeline F.Y. Young Evangeline F.Y. Young received her B.Sc. degree and M.Phil. degree in Computer Science from the Chinese University of Hong Kong (CUHK). She received her Ph.D. degree from the University of Texas at Austin in 1999. Currently, she is an associate professor in the Department of Computer Science and Engineering in CUHK. Her research interests include algorithms and CAD of VLSI circuits. She is now working actively on floorplan design optimization, placement, shuttle mask floorplanning and circuit retiming.

PLACE PHOTO HERE Chris Chu Chris Chu received the B.S. degree in Computer Science from the University of Hong Kong, Hong Kong, in 1993. He received the M.S. degree and the Ph.D. degree in Computer Science from the University of Texas at Austin in 1994 and 1999, respectively.

Dr. Chu is currently an Associate Professor in the Electrical and Computer Engineering Department at Iowa State University. His area of expertises include CAD of VLSI physical design, and design and analysis of algorithms. His recent research interests are

performance-driven interconnect optimization and fast circuit floorplanning, placement, and routing algorithms. He received the IEEE TCAD best paper award at 1999 for his work in performance-driven interconnect optimization. He received the ISPD best paper award at 2004 for his work in efficient placement algorithm. He received the Bert Kay Best Dissertation Award for 1998-1999 from the Department of Computer Sciences in the University of Texas at Austin.

Dr. Chu has served on the technical program committees of several major conferences including ISPD, ISCAS, DATE, ASP-DAC, and SLIP. He has also served as an organizer for the ACM SIGDA Ph.D. Forum.

PLACE PHOTO HERE Sampath Dechu Sampath Dechu received his M.S. degree in Computer Engineering from Iowa State University, Ames, in 2003. He is currently working as Sr. Software Engineer at Blaze-DFM, Inc., developing algorithms and tools for statistical timing analysis, sensitivities of various circuit parameters, such as delay and leakage power, to inter and intra-die variations. Prior to joining Blaze-DFM, he worked as Sr. Software Engineer at Zenasis Technologies from 2004 to 2006. His research interests include areas of statistical timing analysis and optimization,

design for manufacturing.